在硬盘热插拔期间保护硬盘的方法及相应的半导体装置与流程

- 国知局

- 2024-07-31 20:12:17

本发明主要涉及到存储管理的,更确切的说,涉及到了在硬盘热插拔期间保护硬盘的方法以及实现该方法的半导体装置。

背景技术:

1、网络存储器或存储服务器或云服务站等皆大量使用多盘位,以便在存储扩容或存储缩容的需求中能够便捷的在盘位处热插拔硬盘。在由数十个甚至近百个盘位所组网的服务器中硬盘突然的热插拔,会较大概率的增加硬盘故障率、导致硬盘损坏。热插拔时如果未正确保护硬盘数据端口,还会导致数据在热插拔过程中遭到破坏或删除。

2、针对硬盘的被热插拔的端口这一类对象,热插拔处理事件的瞬间,端口处陡然的电压浪涌或者陡然的电压跌落,很容易伤害端口。热插拔导致端口处电压的瞬变不仅仅会损毁端口以及与端口相连的电子元器件、严重的还会损坏存储颗粒等部件。在热插拔期间丢失的数据往往是近乎不太可能恢复的。这是亟待解决的严峻问题之一。

技术实现思路

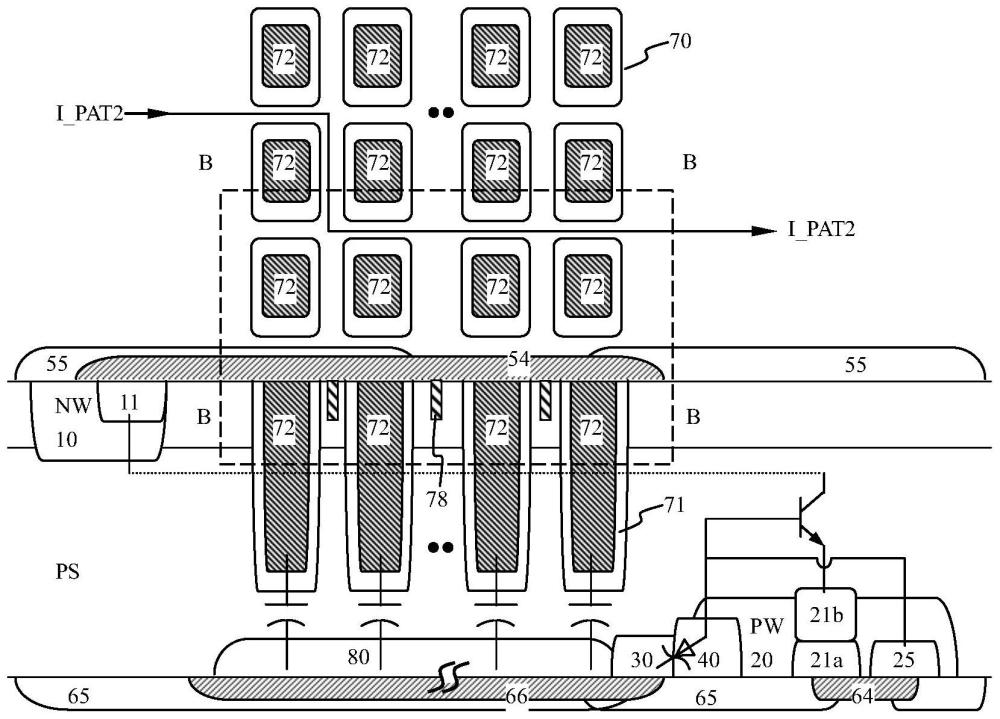

1、本技术涉及一种半导体装置,其特征在于,包括:

2、第一导电类型的衬底,在衬底背面植入的第一导电类型的第一阱区、在衬底正面植入的第二导电类型的第二阱区;

3、开设在衬底正面的多个沟槽,沟槽内壁附着有绝缘层及沟槽内部填充有导电材料;

4、设置在衬底背面的一个极板,每个沟槽在垂直于衬底的方向上皆与极板交叠;

5、位于所述第一阱区的并设在衬底背面的第一导电类型的第一掺杂区和第二导电类型的第二掺杂区、位于所述第二阱区的并设在衬底正面的第二导电类型的第三掺杂区;

6、设置在衬底背面的接触所述极板的一个第二导电类型的钳位区、以及从钳位区延伸到第一阱区的一个第一导电类型的联结区;

7、施加于所述导电材料及第三掺杂区的瞬态电压在引导所述钳位区与联结区之间的结点被反向击穿的条件下,由被触发导通的并介于所述第二掺杂区、衬底、第三掺杂区之间的一个双极晶体管来释放所述瞬态电压。

8、上述的半导体装置,所述衬底正面设置有顶部金属层,其接触所述第三掺杂区和所述导电材料,并且所述瞬态电压连接到所述顶部金属层处;

9、所述衬底背面设置有底部金属层,其接触所述第一掺杂区和所述第二掺杂区,并且所述底部金属层连接到一个参考地处。

10、上述的半导体装置,在所述衬底正面覆盖有顶部介质层,其露出所述顶部金属层的局部区域,以作为承接瞬态电压的一个端口;在衬底背面覆盖有底部介质层,其露出所述底部金属层的局部区域,以作为承接所述参考地的一个端口。

11、上述的半导体装置,在衬底背面覆盖有底部介质层,其露出极板的局部区域,以作为承接所述瞬态电压的一个端口,所述瞬态电压通过电阻连接到所述极板处。

12、上述的半导体装置,所述半导体装置与硬盘的插拔端子电性连接,其中,所述瞬态电压为硬盘的插拔端子在热插拔事件阶段所承受的突变电压。

13、上述的半导体装置,还包括设在衬底背面的一个或多个第二导电类型的掩埋区,掩埋区接触所述极板并且所述掩埋区位于多个所述沟槽与所述极板之间的衬底区域。

14、上述的半导体装置,还包括位于第二阱区的并设在衬底正面的第一导电类型的第四掺杂区;当介于第二掺杂区、衬底、第三掺杂区之间的双极晶体管触发导通时,其导通条件下的电流触发介于第四掺杂区、第二阱区、衬底间的另一双极晶体管导通。

15、上述的半导体装置,所述第一阱区和所述第二阱区分别位于衬底的用于布置多个所述沟槽的一个指定区域的不同侧、且互不交叠,从而使任意一个双极晶体管导通时的电流至少具有横向流经衬底的位于多个所述沟槽之间的间隙区的横向路径。

16、上述的半导体装置,还包括设在衬底正面的第二导电类型的本体区,所述沟槽向下贯穿本体区;以及

17、还包括位于相邻所述沟槽之间的并设在衬底正面的金属栓塞,任意相邻两个所述沟槽之间的一个金属栓塞在本体区内向下延伸、但没有延伸到本体区下侧的衬底处;

18、所述瞬态电压同时还施加在所述的金属栓塞上。

19、本技术还涉及一种在硬盘热插拔期间保护硬盘的方法,其特征在于,利用一个半导体装置来释放硬盘的插拔端子在热插拔事件之时的瞬态电压:

20、所述的半导体装置包括:

21、第一导电类型的衬底,在衬底背面植入的第一导电类型的第一阱区、在衬底正面植入的第二导电类型的第二阱区;

22、开设在衬底正面的多个沟槽,沟槽内壁附着有绝缘层及沟槽内部填充有导电材料;

23、设置在衬底背面的一个极板,每个沟槽在垂直于衬底的方向上皆与极板交叠;

24、位于所述第一阱区的并设在衬底背面的第一导电类型的第一掺杂区和第二导电类型的第二掺杂区、位于所述第二阱区的并设在衬底正面的第二导电类型的第三掺杂区;

25、设置在衬底背面的接触所述极板的一个第二导电类型的钳位区、以及从钳位区延伸到第一阱区的一个第一导电类型的联结区;

26、施加于所述导电材料及第三掺杂区的瞬态电压在引导所述钳位区与联结区之间的结点被反向击穿的条件下,由被触发导通的并介于所述第二掺杂区、衬底、第三掺杂区之间的一个双极晶体管来释放所述瞬态电压;

27、所述的方法包括:

28、对所述硬盘执行热插拔,在所述半导体装置与所述硬盘进行对接时,将所述硬盘的插拔端子在热插拔事件中所产生的浪涌电压视为所述瞬态电压;

29、利用所述极板与多个所述沟槽内的导电材料之间存在的电容而将所述瞬态电压耦合到所述钳位区与联结区之间的结点处,以触发该双极晶体管予以导通。

30、上述的方法,所述的衬底正面设置有顶部金属层,其接触所述第三掺杂区和所述导电材料,并且所述瞬态电压连接到所述顶部金属层处;

31、所述衬底背面设置有底部金属层,其接触所述第一掺杂区和所述第二掺杂区,并且所述底部金属层连接到一个参考地处。

32、上述的方法,在所述的衬底正面覆盖有顶部介质层,其露出所述的顶部金属层的局部区域,以作为承接瞬态电压的一个端口;在衬底背面覆盖有底部介质层,其露出所述底部金属层的局部区域,以作为承接所述参考地的一个端口。

33、上述的方法,在衬底背面覆盖有底部介质层,其露出所述极板的局部区域,以作为承接所述瞬态电压的一个端口,所述瞬态电压通过电阻连接到所述极板处。

34、上述的方法,所述半导体装置与硬盘的插拔端子电性连接,其中,所述瞬态电压为硬盘的插拔端子在热插拔事件阶段所承受的突变电压。

35、上述的方法,还包括设在衬底背面的一个或多个第二导电类型的掩埋区,所述掩埋区接触所述极板并且所述掩埋区位于多个所述沟槽与所述极板之间的衬底区域。

36、上述的方法,还包括位于所述的第二阱区的并设在衬底正面的第一导电类型的第四掺杂区;介于第二掺杂区、衬底、第三掺杂区之间的双极晶体管触发导通时,其导通条件下的电流触发介于第四掺杂区、第二阱区、衬底间的另一双极晶体管进一步导通。

37、上述的方法,所述的第一阱区和所述第二阱区分别位于衬底的用于布置多个所述沟槽的一个指定区域的不同侧、且互不交叠,从而使任意一个双极晶体管导通时的电流至少具有横向流经衬底的位于多个所述沟槽之间的间隙区的横向路径。

38、上述的方法,还包括设在所述衬底正面的第二导电类型的本体区,所述沟槽向下贯穿该本体区;以及

39、还包括位于相邻所述沟槽之间的并设在衬底正面的金属栓塞,任意相邻两个所述沟槽之间的一个金属栓塞在本体区内向下延伸、但没有延伸到本体区下侧的衬底处;

40、所述瞬态电压同时还施加在所述的金属栓塞上。

41、本技术的优势之一:对经常热插拔的硬盘而言,即便其硬件接口存在较大概率的偶发诞生而来的徒增电压或徒降电压,由于本技术之半导体装置面临此类电压时可通过触发导通的双极晶体管来产生泄放路径,所以热插拔的偶发闪变电压对硬件接口的扰动会在较短的时间内消除负面影响。可防止硬盘或主机的相关热插拔接口损毁。也较大程度的降低在热插拔期间硬盘发生数据丢失的概率,例如避免浪涌损坏存储颗粒。

42、本技术的优势之二:半导体装置对热插拔的变化电压极度敏感,首先是以优先级高的方式保障对于高频的闪变电压的高速释放和泄压,而同时也还兼顾到以优先级低的方式保障对于低频的缓变电压的次高速释放和泄压。也就是说,热插拔相关的瞬态电压这类变化电压内部的高频分量和低频分量各自均有合理而又有效的释放途径。

43、本技术的优势之三:半导体装置对热插拔造成的不可抗击电压,具有基于有限雪崩而激活泄放路径的自我保护机制。换而言之,当半导体装置被施加了足以损毁自身及损毁硬盘的不可抗击电压之时,会触发其保护机制来避免损毁的发生或扩大化。

本文地址:https://www.jishuxx.com/zhuanli/20240731/185427.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表