能够为互连协议准备能力信息的控制器以及电子装置的制作方法

- 国知局

- 2024-08-02 14:03:52

本申请是涉及一种电子装置,尤其是涉及能够为互连协议准备能力信息的控制器以及电子装置。

背景技术:

1、现今移动装置(如智能电话、平板电脑、多媒体装置、可穿戴装置之类的计算装置)中发送和处理的数据量不断增加,移动装置内部的芯片对芯片的或受移动装置影响的互连接口技术需要进一步的演进,从而达至能够满足更高的传输速度、低功耗运作、具可扩充性、支援多工处理、易于采用等目标。

2、为此,行动产业处理器接口(mobile industry processor interface,mipi)联盟开发出能够符合上述目标的互连接口技术,例如涉及物理层的mipi m-phy规范以及涉及统一协议(unified protocol,unipro)的mipi unipro规范。另一方面,联合电子装置工程委员会(joint electron device engineering council,jedec)利用mipi m-phy规范及通用传输协议mipi unipro规范推出下一代高性能非易失性存储器标准,称为通用闪存存储(universal flash storage,ufs),其可实现每秒千兆位等级的高速传输及低功耗运作,并具有高阶行动系统所需的功能和可扩展性,从而有助于为业界快速的采用。

3、依据ufs标准的系统(ufs系统)包含了计算装置及具有非易失性存储器的存储装置,计算装置及存储装置分别担任本地的(local)主机与远程的(remote)装置的角色。为了能够依据ufs标准进行通信,本地的主机与远程的装置需要依据ufs标准所采用的unipro规范进行建立链路(link)的过程,并在建立链路的过程中彼此传递涉及链路的能力信息(capability information)给对方,从而让彼此协同完成链路的建立。在本地的主机与远程的装置各自需要准备能力信息。unipro规范指明所需要准备的能力信息。

技术实现思路

1、本披露提供能够为互连协议准备能力信息的控制器以及使用所述控制器的电子装置的多个实施例。借此,所述电子装置能够有效率地及有弹性地依据所述互连协议的规范来准备能力信息,从而有助于链路的建立。

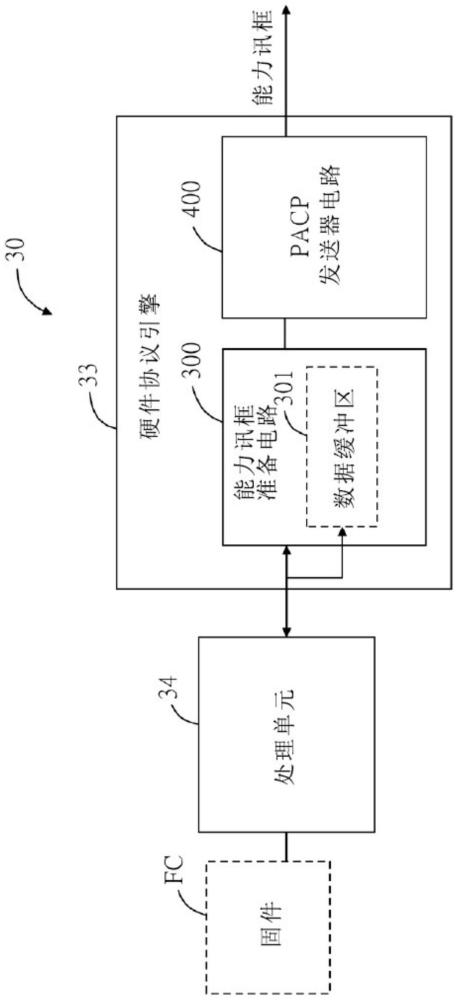

2、本披露提供一种控制器的实施例,其适用于第一装置中且能够为互连协议准备能力信息,所述第一装置能够依据所述互连协议链接第二装置。所述控制器包括硬件协议引擎及处理单元。所述硬件协议引擎用于实现所述互连协议的链接层,其中所述硬件协议引擎还能够进行能力撷取及讯框格式化的运作以输出能力讯框信息至数据缓冲区,以及在所述互连协议的链路启动序列(link startup sequence)的能力交换期间,能够依据所述数据缓冲区的内容来发送至少一能力讯框至所述第二装置,所述至少一能力讯框包含第一能力讯框。所述处理单元耦接于所述硬件协议引擎,且被配置为在所述互连协议的链路启动序列的能力交换期间且在所述硬件协议引擎输出所述能力讯框信息至所述数据缓冲区之后以及在所述至少一能力讯框被发送至所述第二装置之前,能够调整所述数据缓冲区的内容。

3、本披露提供一种电子装置的实施例,其能够依据互连协议链接另一电子装置。所述电子装置包括接口电路及硬件协议引擎。所述接口电路用于实现所述互连协议的物理层以链接所述另一电子装置。所述硬件协议引擎耦接至所述接口电路且用于实现所述互连协议的链接层,其中所述硬件协议引擎还能够进行能力撷取及讯框格式化的运作以输出能力讯框信息至数据缓冲区,以及在所述互连协议的链路启动序列的能力交换期间,能够依据所述数据缓冲区的内容来发送至少一能力讯框至所述另一电子装置,所述至少一能力讯框包含第一能力讯框。所述处理单元耦接于所述硬件协议引擎且被配置为在所述互连协议的链路启动序列的能力交换期间且在所述硬件协议引擎输出所述能力讯框信息至所述数据缓冲区之后以及在所述至少一能力讯框被发送至所述另一电子装置之前,能够调整所述数据缓冲区的内容。

4、在上述控制器或电子装置的一些实施例中,所述硬件协议引擎针对所述第一能力讯框进行能力撷取及讯框格式化的运作以输出所述第一能力讯框的第一能力讯框信息至所述数据缓冲区中,并且所述处理单元针对所述第一能力讯框进行能力撷取及讯框格式化的运作以输出所述第一能力讯框的第二能力讯框信息至所述数据缓冲区中。

5、在上述控制器或电子装置的一些实施例中,所述硬件协议引擎依据所述第一能力讯框的第一版本的数据结构进行能力撷取及讯框格式化的运作以输出所述第一能力讯框的第一能力讯框信息至所述数据缓冲区中,并且所述处理单元依据所述第一能力讯框的第二版本的数据结构进行能力撷取及讯框格式化的运作以输出所述第一能力讯框的第二能力讯框信息至所述数据缓冲区中。

6、在上述控制器或电子装置的一些实施例中,所述第一能力讯框信息对应至所述第一能力讯框的所述第一版本的数据结构,以及所述第二能力讯框信息对应至所述第一能力讯框的所述第二版本的数据结构相较于所述第一能力讯框的所述第一版本的数据结构的不同数据栏位。

7、在上述控制器或电子装置的一些实施例中,所述硬件协议引擎包含能力讯框准备电路,其包括:能力信息收集电路、讯框格式化电路、存储器及流程控制电路。所述能力信息收集电路用以对与能力讯框中多个数据栏位相关的多个寄存器进行读取运作以收集所述多个数据栏位的数据。所述讯框格式化电路用以依据所述多个数据栏位的数据及所述能力讯框的数据结构进行讯框格式化并将对应的讯框格式化结果存储于所述数据缓冲区中。所述存储器包含所述数据缓冲区。所述流程控制电路耦接至所述能力信息收集电路、所述讯框格式化电路及所述存储器,用以控制所述能力信息收集电路及所述讯框格式化电路。其中所述流程控制电路将所述能力信息收集电路开启以收集所述多个数据栏位的数据;其中所述流程控制电路将所述讯框格式化电路开启以接收收集到的所述多个数据栏位的数据、进行讯框格式化并将所述对应的讯框格式化结果存储于所述数据缓冲区中。

8、在上述控制器或电子装置的一些实施例中,所述链接层依据统一协议(unipro)规范实现,所述至少一能力讯框为物理配接器层控制协议(physical adapter layercontrol protocol,pacp)讯框。

9、在上述控制器或电子装置的一些实施例中,所述互连协议是基于通用闪存存储(universal flash storage,ufs)标准。

技术特征:1.一种控制器,其特征在于,其适用于第一装置且能够为互连协议准备能力信息,所述第一装置能够依据所述互连协议链接第二装置,所述控制器包括:

2.根据权利要求1所述的控制器,其特征在于,其中所述硬件协议引擎针对所述第一能力讯框进行能力撷取及讯框格式化的运作以输出所述第一能力讯框的第一能力讯框信息至所述数据缓冲区中,并且所述处理单元针对所述第一能力讯框进行能力撷取及讯框格式化的运作以输出所述第一能力讯框的第二能力讯框信息至所述数据缓冲区中。

3.根据权利要求1所述的控制器,其特征在于,其中所述硬件协议引擎依据所述第一能力讯框的第一版本的数据结构进行能力撷取及讯框格式化的运作以输出所述第一能力讯框的第一能力讯框信息至所述数据缓冲区中,并且所述处理单元依据所述第一能力讯框的第二版本的数据结构进行能力撷取及讯框格式化的运作以输出所述第一能力讯框的第二能力讯框信息至所述数据缓冲区中。

4.根据权利要求3所述的控制器,其特征在于,其中所述第一能力讯框信息对应至所述第一能力讯框的所述第一版本的数据结构,以及所述第二能力讯框信息对应至所述第一能力讯框的所述第二版本的数据结构相较于所述第一能力讯框的所述第一版本的数据结构的不同数据栏位。

5.根据权利要求1所述的控制器,其特征在于,其中所述硬件协议引擎包含能力讯框准备电路,其包括:

6.根据权利要求1所述的控制器,其特征在于,其中所述链接层依据统一协议unipro规范实现,所述至少一能力讯框为物理配接器层控制协议pacp讯框。

7.根据权利要求1所述的控制器,其特征在于,其中所述互连协议是基于通用闪存存储ufs标准。

8.一种电子装置,其特征在于,其能够依据互连协议链接另一电子装置,所述电子装置包括:

9.根据权利要求8所述的电子装置,其特征在于,其中所述硬件协议引擎针对所述第一能力讯框进行能力撷取及讯框格式化的运作以输出所述第一能力讯框的第一能力讯框信息至所述数据缓冲区中,并且所述处理单元针对所述第一能力讯框进行能力撷取及讯框格式化的运作以输出所述第一能力讯框的第二能力讯框信息至所述数据缓冲区中。

10.根据权利要求8所述的电子装置,其特征在于,其中所述硬件协议引擎依据所述第一能力讯框的第一版本的数据结构进行能力撷取及讯框格式化的运作以输出所述第一能力讯框的第一能力讯框信息至所述数据缓冲区中,并且所述处理单元依据所述第一能力讯框的第二版本的数据结构进行能力撷取及讯框格式化的运作以输出所述第一能力讯框的第二能力讯框信息至所述数据缓冲区中。

11.根据权利要求10所述的电子装置,其特征在于,其中所述第一能力讯框信息对应至所述第一能力讯框的所述第一版本的数据结构,以及所述第二能力讯框信息对应至所述第一能力讯框的所述第二版本的数据结构相较于所述第一能力讯框的所述第一版本的数据结构的不同数据栏位。

12.根据权利要求8所述的电子装置,其特征在于,其中所述硬件协议引擎包含能力讯框准备电路,其包括:

13.根据权利要求8所述的电子装置,其特征在于,其中所述链接层依据统一协议unipro规范实现,所述至少一能力讯框为物理配接器层控制协议pacp讯框。

14.根据权利要求8所述的电子装置,其特征在于,其中所述互连协议是基于通用闪存存储ufs标准。

技术总结本申请公开一种能够为互连协议准备能力信息的控制器以及电子装置。控制器适用于第一装置,第一装置能够依据互连协议链接第二装置,控制器包括硬件协议引擎及处理单元。硬件协议引擎用于实现互连协议的链接层且还能够进行能力撷取及讯框格式化的运作以输出能力讯框信息至数据缓冲区,以及在互连协议的链路启动序列的能力交换期间依据数据缓冲区的内容来发送能力讯框至第二装置。处理单元被配置为在互连协议的链路启动序列的能力交换期间且在硬件协议引擎输出能力讯框信息至数据缓冲区之后以及在能力讯框被发送至第二装置之前,能够调整数据缓冲区的内容。技术研发人员:王兰丰受保护的技术使用者:爱思开海力士有限公司技术研发日:技术公布日:2024/7/23本文地址:https://www.jishuxx.com/zhuanli/20240801/241600.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。