一种用于PAM4收发机的并行自适应减状态序列检测器

- 国知局

- 2024-08-02 14:17:29

本发明涉及通信,具体涉及一种用于pam4收发机的并行自适应减状态序列检测器。

背景技术:

1、信道isi(符号间干扰)随符号速率提升严重从而导致判决误码率增高正成为制约超高速串化器/解串器(serdes)的重要因素。传统均衡技术如判决反馈均衡器(dfe)因其结构简单,易于实现在serdes接口中得到广泛应用。尽管dfe在消除符号后isi的作用明显,但突发干扰抑制能力弱和存在错误传递现象等弊端。在超过56gbps的高速serdes中,单独的dfe均衡对于降低判决误码率显得捉襟见肘,因此实际上会增加前端连续时间线性均衡器(ctle)和前馈均衡器(ffe)的负担。因此,在112gbps的超高速serdes中,增加ctle级数和ffe的抽头数成为补偿dfe均衡能力不足的一种方法,但这无疑增加了系统复杂度和功耗。

2、受益于高速模数转换器(adc)的发展,伴随传输速率的不断提升,传统的模拟serdes架构演变为adc加数字信号处理器(dsp)的模数混合架构。半导体工艺制程的发展使得误码性能更为优越,结构更为复杂的数字信号处理架构,如最大似然序列检测器(mlsd)在serdes中的应用成为可能。不同于传统均衡判决方式的逐符号处理方法,mlsd采用基于序列的检测方式,它在同等信道环境具有比dfe更为优越的误码性能。mlsd通常部署在高速有线收发器的dsp中。由于存在复杂性高、延迟大和参数不能自适应等缺点,mlsd并没有取代dfe成为信号检测的手段,而是作为一种补充信号检测手段应用于超高速serdes中。

技术实现思路

1、本发明要解决的技术问题:针对现有技术的上述问题,提供一种用于pam4收发机的并行自适应减状态序列检测器,本发明旨在利用降低误码率,降低传统mlsd结构的复杂度,通过基于isi的迫零算法实现检测器的自适应参数调整。

2、为了解决上述技术问题,本发明采用的技术方案为:

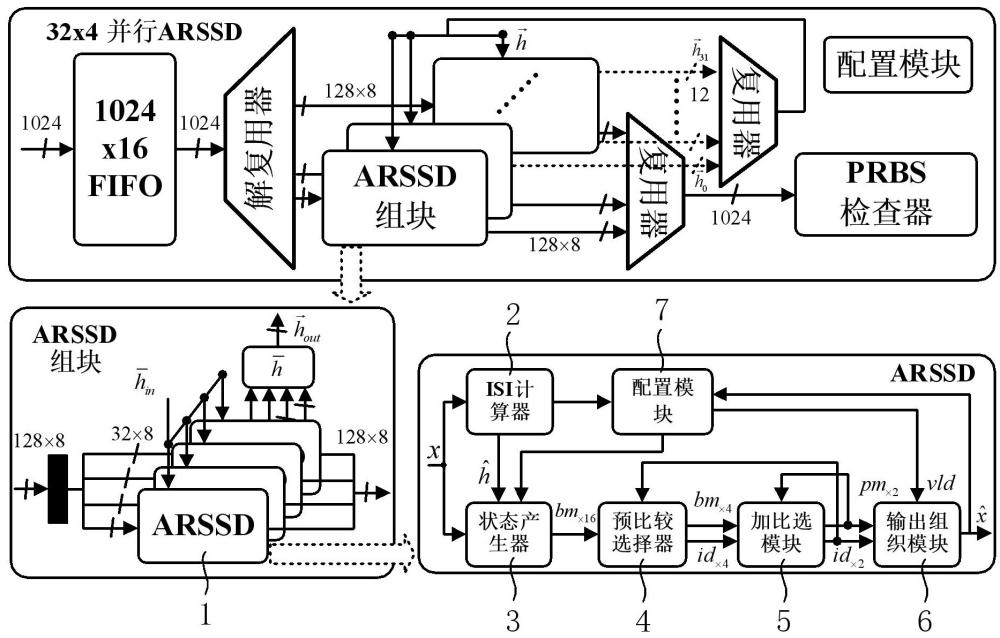

3、一种用于pam4收发机的并行自适应减状态序列检测器,包括由四个并行的序列检测单元构成的序列检测组块,所述序列检测单元包括isi计算器、状态产生器、预比较选择器、加比选模块和输出组织模块,来自外部的128个8位数据分为32路8位数据分别输入四个并行的序列检测单元,所述isi计算器用于根据输入的32路8位数据和上一周期序列检测单元输出的检测值实现isi参数的自适应更新,所述状态产生器用于根据输入的32路8位数据结合isi参数卷积生成预计输入并计算16路可能的分支度量, 16路可能的分支度量通过预比较选择器和加比选模块依次进行分支缩减和路径计算减少为2条幸存路径并输出相应的路径编号,幸存路径在输出组织模块中完成比较输出其路径编号并转换为输出的检测值。

4、可选地,所述序列检测单元还包括配置模块,所述配置模块与状态产生器相连以用于为状态产生器提供初始的isi参数。

5、可选地,所述序列检测组块的数量为多个且多个序列检测组块之间并行布置,多个序列检测组块的前端依次设有解复用器和先入先出队列fifo,所述解复用器将先入先出队列fifo和输出的1024×16路数据拆分为128个8位数据分别输入到各个序列检测组块,各个序列检测组块的输出端均通过复用器与prbs检查器相连以用于将各个序列检测组块输出的128个检测结果复用后依次进入prbs检查器中进行prbs检查及误码计算。

6、可选地,所述状态产生器包含可能值产生器、卷积器和分支计算模块,所述可能值产生器用于对于2-state的pam4信号产生16种12位的可能取值组合,所述可能取值组合经过卷积器与isi参数卷积后产生预计输入, 所述分支计算模块计算预计输入与真实输入的欧式距离后产生相应的16路分支度量。

7、可选地,所述预比较选择器包含四个相同的选择比较器,16条分支度量根据分区算法在预比较选择器中分成四组分别输入选择比较器,选择比较器按照起始节点和目的节点将输入的四组分支度量进行两轮两两比较,先比较分区内路径、然后根据前一时刻反馈的幸存路径编号在到达同一目的分区的不同分区之间做出选择,最终预比较选择器输出4条幸存分支的分支度量和路径编号。

8、可选地,所述加比选模块用于通过维特比算法va在4条幸存分支中,将到达同一分区的分支被进行比较,两条分支加上起始分区累积的路径值进行比较后,较小的值保存为新的路径值且该分支编号也被记录,且两个分区的路径值不断累加新的分支值输出到输出组织模块。

9、可选地,所述输出组织模块包括个寄存器和个复用器,其中为指定的路径长度,个寄存器用于保存2个分区的幸存路径,个复用器用于根据各分区新的路径度量来更新本分区保存的分支编号,当计数器到达长度时,两个分区累积的路径度量进行比较,度量值较小路径的编号保存到输出寄存器,路径编号经由转换函数变为2位pam4编码输出,使得输出组织模块实现32路pam4信号的并行输出。

10、可选地,所述isi计算器包括多个并行系数更新器,所述并行系数更新器用于实现isi参数的自适应更新。

11、可选地,所述实现isi参数的自适应更新的函数表达式为:

12、,

13、上式中,和分别为更新前后的第 j个抽头的isi参数,表示采样时间,表示抽头排序,δ表示步长,为 k时刻卷积后产生的预计输入,为 k- j时刻卷积后产生的预计输入,为 k时刻的真实输入。

14、可选地,所述并行系数更新器用于实现isi参数的自适应更新时, k时刻的真实输入、 k时刻卷积后产生的预计输入、 k- j时刻卷积后产生的预计输入以及更新前后的第 j个抽头的isi参数和均为12位。

15、和现有技术相比,本发明主要具有下述优点:本发明包括由四个并行的序列检测单元构成的序列检测组块,序列检测单元包括isi计算器、状态产生器、预比较选择器、加比选模块和输出组织模块,isi计算器用于实现isi参数的更新,状态产生器用于根据输入数据结合isi参数卷积生成预计输入并计算16路可能的分支度量,分支度量通过预比较选择器和加比选模块进行分支缩减和路径计算减少为2条幸存路径并输出相应的路径编号,幸存路径在输出组织模块中完成比较输出其路径编号并转换为输出的检测值,通过上述四个并行的序列检测单元构成的序列检测组块能够降低误码率,通过预比较选择器和加比选模块进行分支缩减和路径计算减少为2条幸存路径并输出相应的路径编号能够降低传统mlsd结构的复杂度,通过基于isi的迫零算法实现检测器的自适应参数调整。

技术特征:1. 一种用于pam4收发机的并行自适应减状态序列检测器,其特征在于,包括由四个并行的序列检测单元(1)构成的序列检测组块,所述序列检测单元(1)包括isi计算器(2)、状态产生器(3)、预比较选择器(4)、加比选模块(5)和输出组织模块(6),来自外部的128个8位数据分为32路8位数据分别输入四个并行的序列检测单元(1),所述isi计算器(2)用于根据输入的32路8位数据和上一周期序列检测单元(1)输出的检测值实现isi参数的自适应更新,所述状态产生器(3)用于根据输入的32路8位数据结合isi参数卷积生成预计输入并计算16路可能的分支度量, 16路可能的分支度量通过预比较选择器(4)和加比选模块(5)依次进行分支缩减和路径计算减少为2条幸存路径并输出相应的路径编号,幸存路径在输出组织模块(6)中完成比较输出其路径编号并转换为输出的检测值。

2.根据权利要求1所述的用于pam4收发机的并行自适应减状态序列检测器,其特征在于,所述序列检测单元(1)还包括配置模块(7),所述配置模块(7)与状态产生器(3)相连以用于为状态产生器(3)提供初始的isi参数。

3.根据权利要求1所述的用于pam4收发机的并行自适应减状态序列检测器,其特征在于,所述序列检测组块的数量为多个且多个序列检测组块之间并行布置,多个序列检测组块的前端依次设有解复用器和先入先出队列fifo,所述解复用器将先入先出队列fifo和输出的1024×16路数据拆分为128个8位数据分别输入到各个序列检测组块,各个序列检测组块的输出端均通过复用器与prbs检查器相连以用于将各个序列检测组块输出的128个检测结果复用后依次进入prbs检查器中进行prbs检查及误码计算。

4. 根据权利要求1所述的用于pam4收发机的并行自适应减状态序列检测器,其特征在于,所述状态产生器(3)包含可能值产生器、卷积器和分支计算模块,所述可能值产生器用于对于2-state的pam4信号产生16种12位的可能取值组合,所述可能取值组合经过卷积器与isi参数卷积后产生预计输入, 所述分支计算模块计算预计输入与真实输入的欧式距离后产生相应的16路分支度量。

5.根据权利要求1所述的用于pam4收发机的并行自适应减状态序列检测器,其特征在于,所述预比较选择器(4)包含四个相同的选择比较器,16条分支度量根据分区算法在预比较选择器(4)中分成四组分别输入选择比较器,选择比较器按照起始节点和目的节点将输入的四组分支度量进行两轮两两比较,先比较分区内路径、然后根据前一时刻反馈的幸存路径编号在到达同一目的分区的不同分区之间做出选择,最终预比较选择器(4)输出4条幸存分支的分支度量和路径编号。

6.根据权利要求1所述的用于pam4收发机的并行自适应减状态序列检测器,其特征在于,所述加比选模块(5)用于通过维特比算法va在4条幸存分支中,将到达同一分区的分支被进行比较,两条分支加上起始分区累积的路径值进行比较后,较小的值保存为新的路径值且该分支编号也被记录,且两个分区的路径值不断累加新的分支值输出到输出组织模块(6)。

7. 根据权利要求1所述的用于pam4收发机的并行自适应减状态序列检测器,其特征在于,所述输出组织模块(6)包括个寄存器和个复用器,其中为指定的路径长度,个寄存器用于保存2个分区的幸存路径, 个复用器用于根据各分区新的路径度量来更新本分区保存的分支编号,当计数器到达长度时,两个分区累积的路径度量进行比较,度量值较小路径的编号保存到输出寄存器,路径编号经由转换函数变为2位 pam4编码输出,使得输出组织模块(6)实现32路pam4信号的并行输出。

8.根据权利要求1所述的用于pam4收发机的并行自适应减状态序列检测器,其特征在于,所述isi计算器(2)包括多个并行系数更新器,所述并行系数更新器用于实现isi参数的自适应更新。

9.根据权利要求8所述的用于pam4收发机的并行自适应减状态序列检测器,其特征在于,所述实现isi参数的自适应更新的函数表达式为:

10.根据权利要求9所述的用于pam4收发机的并行自适应减状态序列检测器,其特征在于,所述并行系数更新器用于实现isi参数的自适应更新时,k时刻的真实输入、k时刻卷积后产生的预计输入、k-j时刻卷积后产生的预计输入以及更新前后的第j个抽头的isi参数和均为12位。

技术总结本发明公开了一种用于PAM4收发机的并行自适应减状态序列检测器,包括由四个并行的序列检测单元构成的序列检测组块,序列检测单元包括ISI计算器、状态产生器、预比较选择器、加比选模块和输出组织模块,ISI计算器用于实现ISI参数的更新,状态产生器用于根据输入数据结合ISI参数卷积生成预计输入并计算16路可能的分支度量,分支度量通过预比较选择器和加比选模块进行分支缩减和路径计算减少为2条幸存路径并输出相应的路径编号,幸存路径在输出组织模块中完成比较输出其路径编号并转换为输出的检测值。本发明旨在利用降低误码率,降低传统MLSD结构的复杂度,通过基于ISI的迫零算法实现检测器的自适应参数调整。技术研发人员:吕方旭,许超龙,赖明澈,欧洋,翦杰,吴利舟,庞征斌,张建民,黎渊,刘普光,孙岩,王子聪受保护的技术使用者:中国人民解放军国防科技大学技术研发日:技术公布日:2024/7/23本文地址:https://www.jishuxx.com/zhuanli/20240801/242290.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

协作传感器共享的制作方法

下一篇

返回列表