一种CAN总线的标准唤醒的实现电路的制作方法

- 国知局

- 2024-08-02 14:19:54

本发明涉及模拟电路设计,具体涉及一种can总线的标准唤醒的实现电路。

背景技术:

1、控制器局域网总线(can,controller area network)是一种用于实时应用的串行通讯协议总线,用于汽车中各种不同元件之间的通信,是世界上应用最广泛的现场总线之一。

2、can标准iso11898-2:2016中示意出了对can的标准唤醒功能(wake-up patternwake-up)有专门的要求。因此在can芯片的设计中,对于标准唤醒功能的实现也是重要部分。

3、现有常规的can总线的标准唤醒采用的是利用10mhz的时钟进行计数的技术方案来进行判断唤醒,但是这种利用高频时钟的方案全程需要较大功耗,对系统待机功耗影响很大。

4、由此可见,研究一种利用低频时钟进行计数来实现can总线的标准唤醒意义重大。

技术实现思路

1、为了解决上述技术问题,本发明提供了一种can总线的标准唤醒的实现电路,包括:

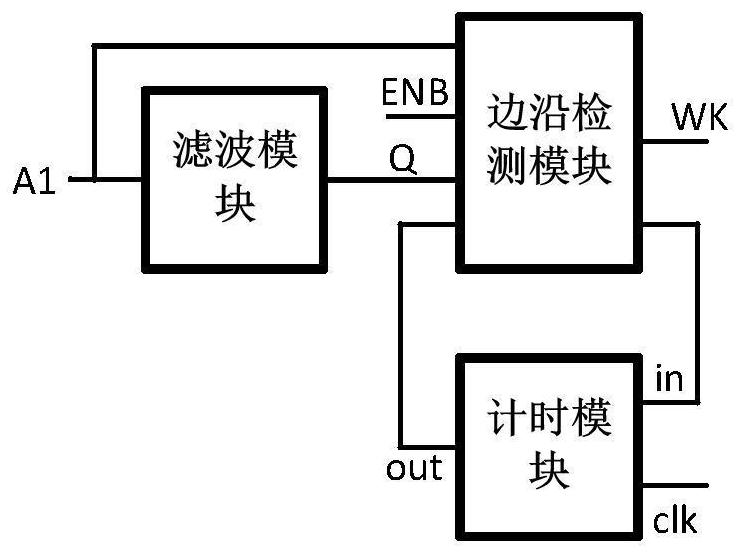

2、滤波模块,用于对can总线传输的差分信号进行滤波处理,得到唤醒信号;

3、边沿检测模块,用于对所述唤醒信号的边沿进行检测;以及

4、计时模块,用于在所述边沿检测模块工作的同时对can总线中的wake-up timeout进行计时;当所述计时模块的计时时间在设定的wake-up timeout时间内,can总线识别到所述唤醒信号后,则can总线可自动唤醒并恢复正常通信状态;当所述计时模块的计时时间超过设定的wake-up timeout时间,则can总线识别当前唤醒信号失败,并重新进入下一次唤醒信号的识别。

5、进一步的,所述滤波模块的输入端a1端口输入所述差分信号,所述滤波模块的输出端q端口连接有所述边沿检测模块;所述边沿检测模块的输出端与所述计时模块的in端口连接,所述计时模块的out端口与所述边沿检测模块的输入端连接。

6、进一步的,所述滤波模块包括延时单元和触发单元,其中:

7、所述延时单元用于设置can总线的唤醒信号的延时时间;

8、所述触发单元用于检测所述唤醒信号,并在满足所述延时时间时触发can总线的唤醒信号边沿。

9、进一步的,所述延时单元包括nmos管nm1、电容c1、电流镜i1和施密特触发器smt1,其中:

10、所述nmos管nm1的源极与所述电流镜i1连接且与所述施密特触发器smt1的输入端连接,所述施密特触发器smt1的输入端还并联有所述电容c1,所述电容c1一端接地。

11、进一步的,所述施密特触发器smt1包括pmos管pm0、pmos管pm1、pmos管pm2、nmos管nm3、nmos管nm4、nmos管nm5以及反相器inv0,其中:

12、所述pmos管pm0的栅极与所述pmos管pm1的栅极、nmos管nm3的栅极、nmos管nm4的栅极连接;所述pmos管pm0的漏极接电源;所述pmos管pm1的源极与所述pmos管pm2的栅极、nmos管nm5的栅极连接;所述pmos管pm1的源极与所述nmos管nm3的源极连接后并与所述反相器inv0的输入端连接。

13、进一步的,所述触发单元包括或非门nor1、或非门nor2以及反相器inv1,其中:

14、所述或非门nor1的输出端与所述或非门nor2的输入端连接,所述或非门nor2的输出端与所述或非门nor1的输入端连接,所述或非门nor2的输出端与所述反相器inv1的输入端连接。

15、进一步的,所述计时模块包括d触发器d0、d触发器d1、d触发器d2、d触发器d3、或非门nor3、与非门nand1、与非门nand2、与门and0以及反相器inv2和反相器inv3,其中:

16、所述或非门nor3的输出端与所述d触发器d0连接;

17、所述d触发器d0的qn0端口、所述d触发器d1的qn1端口分别与所述与非门nand1的输入端连接,所述与非门nand1的输出端与所述反相器inv2的输入端连接;

18、所述d触发器d2的q2端口、所述d触发器d3的q3端口分别与所述与非门nand2的输入端连接,所述与非门nand2的输出端与所述反相器inv3的输入端连接;

19、所述反相器inv2的输出端、反相器inv3的输出端分别与所述与门and0的输入端连接。

20、进一步的,所述边沿检测模块包括d触发器d4、d触发器d5、d触发器d6、d触发器d7、d触发器d8、d触发器d9、d触发器d10、d触发器d11、或非门nor4、或非门nor5、或非门nor6、与非门nand3、反相器inv4、反相器inv5、反相器inv6、反相器inv7、反相器inv8、反相器inv9、反相器inv10、缓冲器buffer1、缓冲器buffer2以及缓冲器buffer3;

21、所述反相器inv8的输出端与所述反相器inv9的输入端连接,所述反相器inv9的输出端与所述缓冲器buffer2的输入端连接,所述缓冲器buffer2的输出端与所述缓冲器buffer3的输入端连接,所述缓冲器buffer3的输出端分别与所述反相器inv4的输入端、d触发器d6的输入端连接;

22、所述反相器inv4的输出端与所述d触发器d4连接,所述d触发器d4与所述d触发器d5连接;所述d触发器d6与所述d触发器d7连接;

23、所述反相器inv4的输出端与所述d触发器d10连接,所述d触发器d10的a1端口与所述反相器inv7的输入端连接,所述反相器inv7的输出端与所述d触发器d11连接;

24、所述d触发器d10的输出端r0端口与所述d触发器d11的输出端r1端口分别与所述或非门nor6的输入端连接,所述或非门nor6的输出端与所述反相器inv10的输入端连接;

25、所述d触发器d7的输出端qi1端口与所述反相器inv5的输入端连接;所述d触发器d5的输出端qr1端口和所述d触发器d5的输入端qr0b端口分别与所述与非门nand3的输入端连接;所述反相器inv5的输出端与所述与非门nand3的输出端分别与所述或非门nor4的输入端连接,所述或非门nor4的输出端与所述d触发器d8连接;所述d触发器d8的输出端分别与所述或非门nor5的输入端、所述缓冲器buffer1的输入端连接,所述缓冲器buffer1的输出端为所述wk端口;所述反相器inv6的输出端与所述或非门nor5的输入端连接,所述或非门nor5的输出端与所述d触发器d9连接。

26、与现有技术相比,本发明具有如下有益效果:

27、本发明提供了一种can总线的标准唤醒的实现电路,通过滤波模块、边沿检测模块和计时模块,实现只需要1khz的时钟就可以完成电路设计,大大降低芯片设计对时钟频率的要求,减小can电路在等待唤醒状态时的功耗。

技术特征:1.一种can总线的标准唤醒的实现电路,其特征在于,包括:

2.根据权利要求1所述的can总线的标准唤醒的实现电路,其特征在于,所述滤波模块的输入端a1端口输入所述差分信号,所述滤波模块的输出端q端口连接有所述边沿检测模块;所述边沿检测模块的输出端与所述计时模块的in端口连接,所述计时模块的out端口与所述边沿检测模块的输入端连接。

3.根据权利要求1所述的can总线的标准唤醒的实现电路,其特征在于,所述滤波模块包括延时单元和触发单元,其中:

4.根据权利要求3所述的can总线的标准唤醒的实现电路,其特征在于,所述延时单元包括nmos管nm1、电容c1、电流镜i1和施密特触发器smt1,其中:

5.根据权利要求4所述的can总线的标准唤醒的实现电路,其特征在于,所述施密特触发器smt1包括pmos管pm0、pmos管pm1、pmos管pm2、nmos管nm3、nmos管nm4、nmos管nm5以及反相器inv0,其中:

6.根据权利要求3所述的can总线的标准唤醒的实现电路,其特征在于,所述触发单元包括或非门nor1、或非门nor2以及反相器inv1,其中:

7.根据权利要求1所述的can总线的标准唤醒的实现电路,其特征在于,所述计时模块包括d触发器d0、d触发器d1、d触发器d2、d触发器d3、或非门nor3、与非门nand1、与非门nand2、与门and0以及反相器inv2和反相器inv3,其中:

8.根据权利要求1所述的can总线的标准唤醒的实现电路,其特征在于,所述边沿检测模块包括d触发器d4、d触发器d5、d触发器d6、d触发器d7、d触发器d8、d触发器d9、d触发器d10、d触发器d11、或非门nor4、或非门nor5、或非门nor6、与非门nand3、反相器inv4、反相器inv5、反相器inv6、反相器inv7、反相器inv8、反相器inv9、反相器inv10、缓冲器buffer1、缓冲器buffer2以及缓冲器buffer3;

技术总结本发明公开一种CAN总线的标准唤醒的实现电路,包括滤波模块,用于对CAN总线传输的差分信号进行滤波处理,得到唤醒信号;边沿检测模块,用于对所述唤醒信号的边沿进行检测;以及计时模块,用于在所述边沿检测模块工作的同时对CAN总线标准中的wake‑up timeout进行计时;当所述计时模块的计时时间在设定的wake‑up timeout时间内,CAN总线识别到所述唤醒信号后,则CAN总线可自动唤醒并恢复正常通信状态;当所述计时模块的计时时间超过设定的wake‑up timeout时间,则CAN总线识别当前唤醒信号失败,并重新进入下一次唤醒信号的识别。本发明实现只需要1KHz的时钟就可以完成电路设计,大大降低芯片设计对时钟频率的要求,减小CAN电路在等待唤醒状态时的功耗。技术研发人员:丁梓恒,潘俊受保护的技术使用者:艾创微(上海)电子科技有限公司技术研发日:技术公布日:2024/7/23本文地址:https://www.jishuxx.com/zhuanli/20240801/242407.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表