具有存储器结构的半导体装置和电子系统,以及相关方法与流程

- 国知局

- 2024-08-02 15:16:56

本发明的实施例涉及半导体装置设计和制造领域。更具体地说,本发明的实施例涉及包含覆在存储器单元上面的介电衬垫材料的存储器结构,涉及形成所述存储器结构的方法,且涉及相关半导体装置和电子系统。

背景技术:

1、半导体装置设计师通常希望通过减小个别特征的尺寸及通过减小相邻特征之间的分隔距离来增大半导体装置内的特征的集成度或密度。另外,半导体装置设计师通常希望设计不仅紧凑而且提供性能优势以及简化设计的架构。

2、半导体装置的一个实例为存储器装置。存储器装置一般被提供为计算机或其它电子装置中的内部集成电路。存在多种类型的存储器,包含(但不限于)随机存取存储器(ram)、只读存储器(rom)、动态随机存取存储器(dram)、同步动态随机存取存储器(sdram)、闪存存储器及可变电阻存储器。可变电阻存储器的非限制性实例包含电阻性随机存取存储器(rram)、导电桥随机存取存储器(导电桥ram)、磁性随机存取存储器(mram)、相变材料(pcm)存储器、相变随机存取存储器(pcram)、自旋力矩转移随机存取存储器(sttram)、氧空位类存储器和可编程导体存储器。

3、一些存储器装置包含存储器阵列,其展现布置成交叉点架构的存储器单元,所述交叉点架构包含垂直(例如,正交)于额外导电线(例如,数据线,如位线)延伸的导电线(例如,存取线,如字线)。存储器阵列可为二维(2d)的,以便展现单个台板(例如,单个层、单个层面)的存储器细胞,或可为三维(3d)的,以便展现多个板(例如,多个层面、多个层)的存储器细胞。选择装置可用于选择存储器阵列的特定存储器单元。

4、与存储器装置制造相关的挑战包含减小存储器装置的大小、增大存储器装置的存储密度和降低制造成本。举例来说,制造3d交叉点存储器阵列通常要求用材料堆叠形成高高宽比存储器单元。对下游处理条件敏感的材料常常存在于所述堆叠中。举例来说,3d交叉点存储器单元可包含如硫族化物材料、含碳材料和其它敏感材料的材料,所述材料可能在常规半导体制造工艺期间所用的温度下受损和/或可能不合需要地与下游处理期间所用的各种材料(例如,蚀刻剂、氧化剂)反应。举例来说,堆叠中的硫族化物材料可能在常规沉积技术期间挥发,引起堆叠材料分层。为了保护堆叠,衬垫材料已形成于堆叠材料上方,之后进行后续处理动作。令人遗憾的是,常规衬垫材料和常规衬垫材料系统可能在形成期间损伤堆叠材料,可能受与不同堆叠材料的一或多种较差粘附力困扰,可能在后续处理动作期间与其上形成的额外材料有害地相互作用,和/或可能阻碍后续处理动作(例如,后续材料去除过程,如后续化学机械平面化动作)的功效。

5、因此,需要新的存储器结构,如包含覆在存储器单元上面的衬垫材料的交叉点存储器结构,且需要包含存储器结构的半导体装置(例如,存储器装置)和电子系统以及形成存储器结构的方法,所述方法克服常规存储器结构、常规半导体装置、常规电子系统和形成存储器结构的常规方法的前述问题中的一或多个(例如,全部)。

技术实现思路

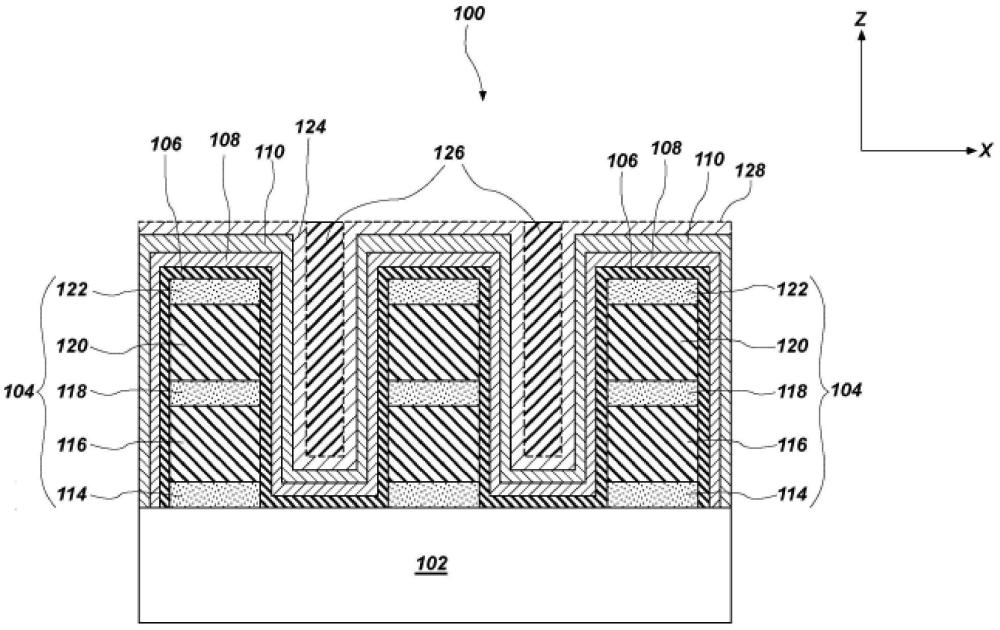

1、本文中所描述的实施例包含含有覆在存储器单元上面的介电衬垫材料的半导体装置、形成存储器结构的相关方法和相关电子系统。根据本文中描述的一个实施例,半导体装置包括存储器单元、覆在存储器单元上面的第一介电衬垫材料、覆在第一介电衬垫材料上面的高k介电材料、覆在高k介电材料上面的第二介电衬垫材料和覆在第二介电衬垫材料上面的额外介电材料。

2、根据本文中所描述的额外实施例,形成存储器结构的方法包括在存储器单元上方形成第一介电衬垫材料。高k介电材料形成于第一介电衬垫材料上方。第二介电衬垫材料形成于高k介电材料上方。额外介电材料形成于第二介电衬垫材料上方。

3、根据本文中描述的其它实施例,电子系统包括与电子信号处理器装置、输入装置和输出装置中的至少一者通信的存储器装置。存储器装置包含存储器结构,所述存储器结构包括存储器单元、存储器单元的侧表面上的第一氮化物介电材料、第一氮化物介电材料的侧表面上的高k介电材料、高k介电材料的侧表面上的第二氮化物介电材料和第二氮化物介电材料的侧表面上方的额外介电材料。

技术特征:1.一种半导体装置,其包括:

2.根据权利要求1所述的半导体装置,其中所述额外介电材料包括与所述第二介电衬垫的所述上表面大体上共面的上表面。

3.根据权利要求1或2所述的半导体装置,其中所述第一氮化物介电衬垫和所述第二氮化物介电衬垫中的至少一者包括氮化硅、氮氧化硅、碳氮化硅、碳氮氧化硅或其任意组合。

4.根据权利要求1或2所述的半导体装置,其中所述第一氮化物介电衬垫包括与所述所述第二氮化物介电衬垫相同的组成。

5.根据权利要求1或2所述的半导体装置,其中所述第一氮化物介电衬垫包括与所述所述第二氮化物介电衬垫不同的组成。

6.根据权利要求1或2所述的半导体装置,其进一步包括位于所述第二氮化物介电衬垫的所述上表面上且位于所述第二氮化物介电衬垫的所述侧表面和所述额外介电材料之间的氧化物介电材料。

7.根据权利要求1所述的半导体装置,所述存储器单元阵列的所述存储器单元中的每一者包含堆叠结构,所述堆叠结构包括:

8.根据权利要求1所述的半导体装置,其中所述选择装置结构位于所述存储元件结构上。

9.根据权利要求7所述的半导体装置,其中所述存储元件结构位于所述选择装置结构上。

10.根据权利要求7所述的半导体装置,其中所述选择装置结构包括与所述存储元件结构相同的材料。

11.根据权利要求7所述的半导体装置,其中所述选择装置结构包括与所述存储元件结构不同的材料。

12.根据权利要求7所述的半导体装置,其中所述存储器单元阵列的所述存储器单元中的至少一者的所述堆叠结构进一步包括位于所述选择装置结构上的第三电极。

13.根据权利要求1、2以及7-12中任意一者所述的半导体装置,其中所述高k介电材料包括二氧化铪(hfo2)、经氮化氧化铪(hfon)、氧化硅酸铪、铝掺杂氧化铪(hfalo)、氧化铝(al2o3)、氧化硅酸铝、二氧化锆(zro2)、五氧化二钽(ta2o5)、氧化镧(la2o3)、二氧化钛(tio2)、氧化钇(y2o3)或任意组合。

14.一种形成存储器结构的方法,其包括:

15.根据权利要求14所述的方法,其进一步包括在所述第二介电衬垫材料上形成所述额外介电材料之前,在所述第二介电衬垫材料上形成氧化物介电材料。

技术总结本申请涉及具有存储器结构的半导体装置和电子系统以及相关方法。一种半导体装置包括存储器单元、覆在所述存储器单元的侧表面上的第一介电衬垫材料、覆在所述第一介电衬垫材料的侧表面上的高k介电材料、覆在所述高k介电材料的侧表面上的第二介电衬垫材料及覆在所述第二介电衬垫材料的侧表面上的额外介电材料。也描述一种电子系统和一种形成存储器结构的方法。技术研发人员:A·J·汉森,J·A·库尔特拉受保护的技术使用者:美光科技公司技术研发日:技术公布日:2024/7/15本文地址:https://www.jishuxx.com/zhuanli/20240801/245504.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表