一种使用错开相位时钟触发的相位插值器的制作方法

- 国知局

- 2024-08-02 15:24:06

本发明涉及相位插值器,尤其涉及一种使用错开相位时钟触发的相位插值器。

背景技术:

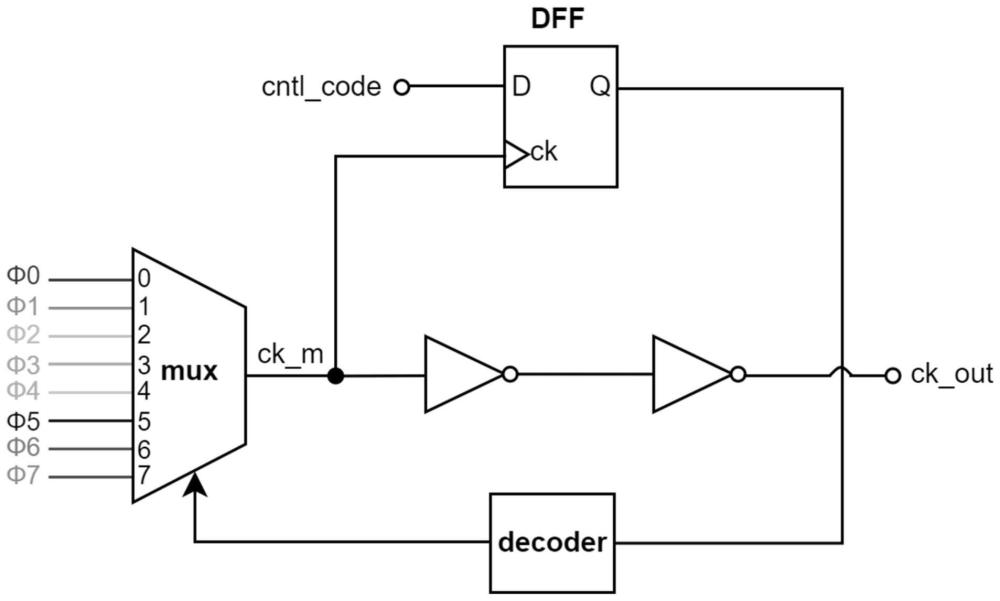

1、相位插值器(phase interpolator,pi)的作用是实现输出时钟相位的调整,本设计所采用的多路选择器(multiplexer,mux)型pi为相位插值器的一种,它使用多路选择器mux选相的方式来实现相位调整。传统的8相位mux型pi结构如图1所示,其中,φ0~φ7为八个同频不同相的时钟输入信号,频率为1ghz,相邻时钟相位间隔45度,ck_out为1ghz的输出时钟。cntl_code为相位控制信号,经过触发器dff采样,通过译码器(decoder)控制mux的输出。输入控制字cntl_code(相位控制信号)采用了格雷码的编码方式,pi接收到控制信号,一次只能动1个bit,即一次只能进行一个相位间隔的移动切换,3bit具体的跳转方式是按000–001–011–010–110–111–101–100–000顺序或逆序逐次切换。多路选择器mux内部环路的时序,指的是从ck_m发生跳变,经过延时ts=clock buffer delay+dff ck to q delay+decoder delay即多路选择器延迟+触发器ck输入端到q输出端的延迟+译码器的延迟之后,又完成选相,回到ck_m的时间。如图2,当时钟相位从ф1向前或向后切换时,希望实现平滑转换。平滑转换指的是:在切换的瞬间,前后两个时钟输入信号的电平相同。具体来说,ф1向前切换到ф0,那么,切换的时间需要在ta-td之间发生,在这段时间里,ф1和ф0同为低电平;同理,ф1向后切换到ф2,那么切换的时间需要在tb-te之间发生,在这段时间里,ф1和ф2同为低电平。

2、定义输入时钟周期为t,假设输入8个时钟的相位差是等间距的45度,即t/8。当小环路的链路延时ts小于t/8,在向前切换相位时,输出时钟会产生毛刺(glitch);若小环路的链路延时ts大于(3/8)t,在向后切换相位时,输出时钟沿会减缓,在电源存在纹波的情况下,缓沿会恶化时钟抖动(jitter)。上述两种情况当中,glitch的后果是功能性问题,jitter的后果是性能退化,所以glitch是绝对要避免的。

3、因此,结合上述两个要求,mux小环路的时序要求是,(1/8)t<ts<(3/8)t。

4、当该电路应用在工作频率为1ghz的高速系统中,mux小环路时序要求是125ps<ts<375ps,在全pvt(工艺角/电压/温度)条件下可以很容易地满足时序要求。但是,当输入时钟频率下降,譬如从1ghz降到了300mhz时,mux小环路时序要求是417ps<ts<1.25ns。为了实现ts>417ps,需要在延时路径中增加多级逻辑门,然而用逻辑门电路硬凑到417ps以上会很吃力,而且延时的pvt误差很大,是一个不可控风险。

技术实现思路

1、基于上述问题,本发明提供一种使用错开相位触发的低速相位插值器,只在解决现有技术中mux型pi适用的时钟频率范围容易出现glitch的技术问题。

2、一种使用错开相位触发的相位插值器,包括:

3、第一多路选择器,具有若干按照输入端编号顺序的第一时钟输入端,分别用于接收不同相位的时钟输入信号;

4、第二多路选择器,具有若干按照输入端编号顺序的第二时钟输入端,用于接收不同相位的时钟输入信号,输入端编号对应的第一时钟输入端和第二时钟输入端输入的时钟输入信号相差两个预定相位间隔;

5、第一触发器,第一触发器的时钟输入端连接第一多路选择器的时钟输出端,以及控制输入端接入相位控制信号;

6、第二触发器,第二触发器的时钟输入端连接第二多路选择器的时钟输出端,控制输入端接入第一触发器的输出端;

7、第一译码器,第一译码器的输入端连接第二触发器的输出端,输出端连接第一多路选择器的相位选择端;

8、第二译码器,第二译码器的输入端连接第一触发器的输出端,输出端连接第二多路选择器的相位选择端;

9、第一多路选择器的时钟输出端用于将最终选择的时钟输入信号作为时钟输出信号输出。

10、进一步的,输入端编号相邻的两个第一时钟输入端接收的时钟输入信号相差一个预定相位间隔;输入端编号相邻的两个第二时钟输入端接收的时钟输入信号具有一个预定相位间隔。

11、进一步的,第一多路选择器和第二多路选择器均具有八个时钟输入端,预定相位间隔为45度。

12、进一步的,还包括缓冲器,缓冲器和第一多路选择器的时钟输出端连接,用于将时钟输出信号整形后输出。

13、进一步的,缓冲器包括:

14、一级反相器,一级反相器的输入端连接第一多路选择器的时钟输出端;

15、二极反相器,二极反相器的输入端连接一级反相器的输出端。

16、进一步的,第一触发器为下降沿触发的d型触发器,第一触发器的控制输入端为d输入端,第一触发器的输出端为q输出端。

17、进一步的,第二触发器为下降沿触发的d型触发器,第二触发器的控制输入端为d输入端,第二触发器的输出端为q输出端。

18、进一步的,第一译码器和第二译码器均为3-8译码器。

19、本发明的有益技术效果在于:对现有多路选择器mux型pi的结构进行优化,利用相差两相位间隔的两路时钟信号进行采样,改变了pi的时序要求。从而达到了减小pvt对时序的影响,拓展了mux型pi适用的时钟频率范围而不容易有毛刺。

技术特征:1.一种使用错开相位触发的相位插值器,其特征在于,包括:

2.如权利要求1所述的一种使用错开相位触发的相位插值器,其特征在于,所述输入端编号相邻的两个所述第一时钟输入端接收的所述时钟输入信号相差一个所述预定相位间隔;所述输入端编号相邻的两个所述第二时钟输入端接收的所述时钟输入信号具有一个所述预定相位间隔。

3.如权利要求1所述的一种使用错开相位触发的相位插值器,其特征在于,所述第一多路选择器和所述第二多路选择器均具有八个所述时钟输入端,所述预定相位间隔为45度。

4.如权利要求1所述的一种使用错开相位触发的相位插值器,其特征在于,还包括缓冲器,所述缓冲器和所述第一多路选择器的时钟输出端连接,用于将所述时钟输出信号整形后输出。

5.如权利要求4所述的一种使用错开相位触发的相位插值器,其特征在于,所述缓冲器包括:

6.如权利要求1所述的一种使用错开相位触发的相位插值器,其特征在于,所述第一触发器为下降沿触发的d型触发器,所述第一触发器的控制输入端为d输入端,所述第一触发器的输出端为q输出端。

7.如权利要求1所述的一种使用错开相位触发的相位插值器,其特征在于,所述第二触发器为下降沿触发的d型触发器,所述第二触发器的控制输入端为d输入端,所述第二触发器的输出端为q输出端。

8.如权利要求1所述的一种使用错开相位触发的相位插值器,其特征在于,所述第一译码器和所述第二译码器均为3-8译码器。

技术总结本发明提供一种使用错开相位触发的相位插值器,第一多路选择器和第二多路选择器中输入端编号对应的时钟输入端输入的时钟输入信号相差两个预定相位间隔;第一触发器的时钟输入端连接第一多路选择器的时钟输出端,控制输入端接入相位控制信号;第二触发器,时钟输入端连接第二多路选择器的时钟输出端,控制输入端接入第一触发器的输出端;第一译码器,输入端连接第二触发器的输出端,输出端连接第一多路选择器的相位选择端;第二译码器,输入端连接第一触发器的输出端,输出端连接第二多路选择器的相位选择端。减小PVT对时序的影响,拓展了Mux型PI适用的时钟频率范围而不容易有毛刺。技术研发人员:董卉,邱志杰受保护的技术使用者:裕太微电子股份有限公司技术研发日:技术公布日:2024/7/18本文地址:https://www.jishuxx.com/zhuanli/20240801/245899.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。