兼容LVDS和PECL电平标准的驱动电路

- 国知局

- 2024-08-02 15:24:00

本技术涉及电子电路,具体涉及一种兼容lvds和pecl电平标准的驱动电路。

背景技术:

1、当信号从芯片内输出到芯片外时,需要经过输出驱动电路将信号电平由芯片内部电压域电平转换为io电平,从而能与外接口通信。其中,传输协议主要包括低压差分信号(low voltage differential,lvds)传输协议、正射极耦合逻辑电平(positive emittercoupled logic,pecl)传输协议。

2、在设计驱动电路时,驱动电路作为数字信号转换为模拟信号再通过引脚输送到芯片外部电路,不同的传输协议的电平并不相同。例如,lvds电平标准的共模电平典型值为1.2v,差模电平典型值为0.35v,而pecl电平标准的共模电平典型值为2v,差模电平典型值为0.7v。

3、因此,单一驱动电路难以驱动多种电平标准的传输协议,对单一驱动电路设计时需要对多种电平标准的兼容性做出取舍。此外,由于传输信道各种非理性因素的干扰,对驱动电路的输出波形会有一定的影响。

技术实现思路

1、本技术提供一种兼容lvds和pecl电平标准的驱动电路,以解决单一驱动电路无法同时适用lvds和pecl两种电平标准的问题。

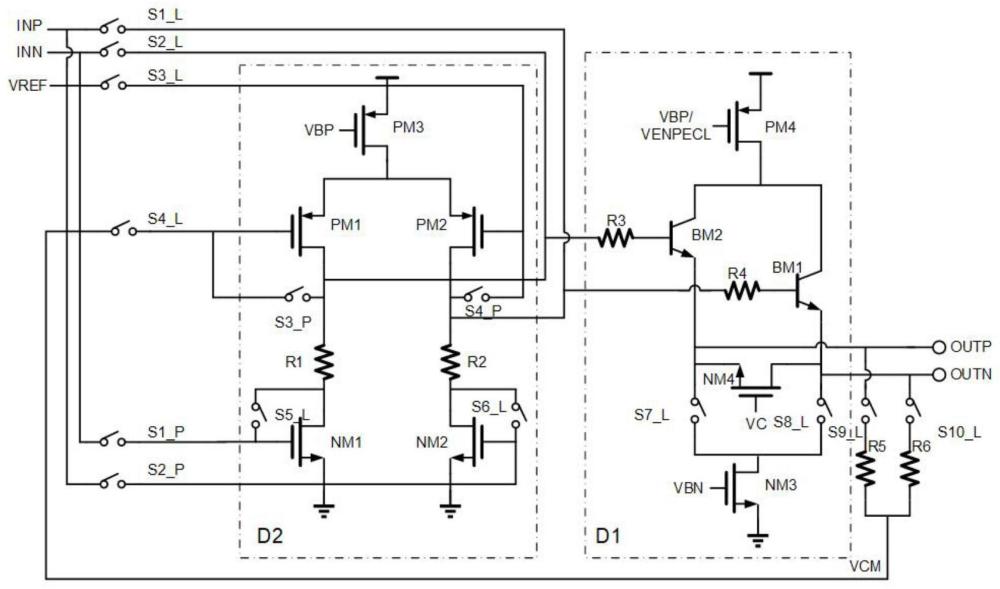

2、本技术提供一种兼容lvds和pecl电平标准的驱动电路,包括:第一信号输入端inp、第二信号输入端inn、共模参考电压输入端vref、第一复用电路单元d1、第二复用电路单d2元、第一信号输出端outp、第二信号输出端outn、电阻r5、电阻r6、开关s1l、开关s2l、开关s3l、开关s4l、开关s9l、开关s10l、开关s1p、开关s2p;

3、所述第一复用电路单元d1包括绝缘栅双极晶体管pm4;

4、所述绝缘栅双极晶体管pm4的发射极分别与三极管bm2、三极管bm1的集电极连接;

5、所述三极管bm2的发射极分别与绝缘栅双极晶体管nm3的集电极、绝缘双极晶体管nm4的发射极连接;

6、所述三极管bm1的发射极分别与所述绝缘栅双极晶体管nm3的集电极、所述绝缘双极晶体管nm4的集电极连接;

7、所述绝缘栅双极晶体管nm3的集电极通过开关s7l与所述绝缘栅双极晶体管的发射极连接;

8、所述绝缘栅双极晶体管nm3的集电极通过开关s8l与所述绝缘栅双极晶体管的集电极连接;

9、所述绝缘栅双极晶体管nm3的发射极接地;

10、所述第二复用电路单元d2包括绝缘栅双极晶体管pm3;

11、所述绝缘栅双极晶体管pm3的发射极分别与绝缘栅双极晶体管pm1、绝缘栅双极晶体管pm2的集电极连接;

12、所述绝缘栅双极晶体管pm1的集电极与电阻r1串联并与绝缘栅双极晶体管nm1的集电极连接;

13、所述绝缘栅双极晶体管pm2的集电极与电阻r2串联并与绝缘栅双极晶体管nm2的集电极连接;

14、所述绝缘栅双极晶体管nm1和所述绝缘栅双极晶体管nm2的发射极接地;

15、所述绝缘栅双极晶体管pm1的栅极和发射极通过开关s3p连接;

16、所述绝缘栅双极晶体管pm2的栅极和发射极通过开关s4p连接;

17、所述绝缘栅双极晶体管nm1的栅极和集电极通过开关s5l连接;

18、所述绝缘栅双极晶体管pm2的栅极和集电极通过开关s6l连接;

19、所述第一信号输入端inp通过所述开关s1l与所述绝缘栅双极晶体管pm2的发射极连接;

20、所述第一信号输入端inp通过所述开关s2p与所述绝缘栅双极晶体管nm2的栅极连接;

21、所述第二信号输入端inn通过所述开关s2l与所述绝缘栅双极晶体管pm1的发射极连接;

22、所述第二信号输入端inn通过所述开关s1p与所述绝缘栅双极晶体管nm1的栅极连接;

23、所述共模参考电压输入端vref通过所述开关s3l与所述绝缘栅双极晶体管pm2栅极连接;

24、所述第一信号输出端outp与所述三极管bm2、所述绝缘栅双极晶体管nm4的共联端连接;

25、所述第二信号输出端outn与所述三极管bm1、所述绝缘栅双极晶体管nm4的共联端连接;

26、所述开关s9l的两端分别连接所述第一信号输出端outp和电阻r5;

27、所述开关s10l的两端分别连接所述第二信号输出端outn和电阻r6;

28、所述电阻r5与所述电阻r6连接;

29、所述开关s4l的一端与所述绝缘栅双极晶体管pm1的栅极连接,所述开关s4l的另一端分别与所述电阻r5、所述电阻r6连接。

30、可选的,还包括电阻r3和电阻r4;

31、所述电阻r3的一端与所述绝缘栅双极晶体管pm1的发射极连接,所述电阻r3的另一端与所述三极管bm2的基极连接;

32、所述电阻r4的一端与所述绝缘栅双极晶体管pm2的发射极连接,所述电阻r4的另一端与所述三极管bm1的基极连接。

33、可选的,所述绝缘栅双极晶体管nm4的栅极与控制信号vc连接。

34、可选的,所述绝缘栅双极晶体管pm3的栅极与偏置电压vbp连接;所述绝缘栅双极晶体管nm4的栅极与偏置电压vbn连接;所述绝缘栅双极晶体管pm4的栅极与偏置电压vbp或激活信号venpecl连接。

35、可选的,所述开关s1l、所述开关s2l、所述开关s3l、所述开关s4l、所述开关s5l、所述开关s6l、所述开关s7l、所述开关s8l、所述开关s9l、所述开关s10l为闭合状态,所述开关s1p、所述开关s2p、所述开关s3p、所述开关s4p为断开状态时,驱动电路被配置为lvds模式。

36、可选的,所述开关s1l、所述开关s2l、所述开关s3l、所述开关s4l、所述开关s5l、所述开关s6l、所述开关s7l、所述开关s8l、所述开关s9l、所述开关s10l为断开状态,所述开关s1p、所述开关s2p、所述开关s3p、所述开关s4为p闭合状态时,驱动电路被配置为pecl模式。

37、由以上技术方案可知,本技术提供一种兼容lvds和pecl电平标准的驱动电路,包括:第一信号输入端inp、第二信号输入端inn、共模参考电压输入端vref、第一复用电路单元d1、第二复用电路单d2元、第一信号输出端outp、第二信号输出端outn、电阻r5、电阻r6、开关s1l、开关s2l、开关s3l、开关s4l、开关s9l、开关s10l、开关s1p、开关s2p。通过对开关的状态切换可以实现lvds模式和pecl模式的配置,所述第一复用电路单元d1作为输出驱动电路,所述第二复用电路单元d2作为多功能电路,当配置为lvds模式时,所述第二复用电路单元d2作为共模反馈模块,能够实时的调整电路的输出共模电压,当配置为pecl模式时,所述第二复用电路单元d2作为预驱动电路,可以将接入的cmos信号转换为cml信号,从而使得输出级能够正常工作。通过将两种驱动电路集成为一套电路,以解决单一驱动电路无法同时适用lvds和pecl两种电平标准的问题。

本文地址:https://www.jishuxx.com/zhuanli/20240801/245890.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表