构建可配置的高码率Turbo编译码器的方法和系统与流程

- 国知局

- 2024-08-02 15:33:56

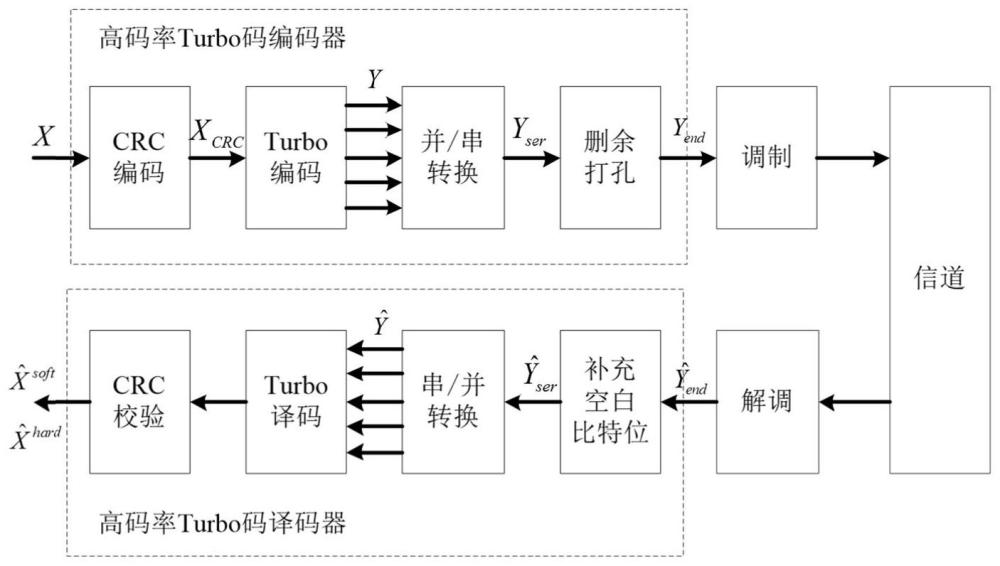

本发明涉及无线通信,具体地,涉及一种构建可配置的高码率turbo编译码器的方法和系统。

背景技术:

1、信道编码是指在发射端对待发送的信息比特中,根据一定的规律插入一些人为生成的冗余比特,从而提升其检错纠错能力的编码方法。对信息进行信道编译码处理,可以提升信号的抗噪声、抗干扰能力,改善数字通信系统的传输质量。常见的信道编码方法有:turbo码、rs码、ldpc码等。其中,turbo码不仅在低信噪比的环境下具有较强的抗噪声能力,具有很高的性能优势,并且在信道环境复杂,并且衰落较大的时候,依然能表现出很强的抗衰落能力与抗干扰能力,所以turbo码在信道复杂的无线通信系统中有很大的应用前景。

2、目前对turbo码的应用主要集中在低码率,如在cdma2000中,可选1/2、1/3或1/4码率的turbo码;在wcdma中,采用码率为1/3的turbo码。低码率适合带宽较宽的通信场景,但是在对带宽利用率要求较高的个人移动通信等场景下,则希望有更高的编码效率。目前,将turbo码作为高带宽利用率无线通信场景下信道编解码方法的应用仍较少。

3、在对带宽利用率要求较高的个人移动通信等场景下,低码率信道编码无法满足通信需求,需要一种高码率、高性能的信道编译码实现方法。因此希望通过循环冗余校验与咬尾turbo编码方式相结合的方式,实现可配置的turbo高码率编译码,满足turbo码在对传输效率要求较高的无线通信场景下的使用需求。

4、专利文献cn101777926a公开了一种turbo乘积码的通用译码器及其方法。该通用译码器由初始信息存储模块,外信息存储模块,不可靠位计算模块,代数译码模块,两个先入先出存储模块,度量比较模块,外信息计算模块,译码控制模块以及接口组成。然而该专利无法完全解决目前存在的技术问题,也无法满足本发明的需求。

技术实现思路

1、针对现有技术中的缺陷,本发明的目的是提供一种构建可配置的高码率turbo编译码器的方法和系统。

2、根据本发明提供的构建可配置的高码率turbo编译码器的方法,包括:

3、步骤1:编码器进行crc编码,收到开始编码指示后,crc编码模块对待编码数据进行crc编码,得到crc编码后的数据,将其存入rom存储模块中;

4、步骤2:编码器生成交织索引表,收到开始编码指示后,交织器模块开始工作,产生交织索引表,存入rom存储模块;

5、步骤3:编码器进行turbo预编码,编码准备结束后,将crc编码模块输出的比特序列引入rsc1子编码器模块;同时将交织过的比特序列引入rsc2子编码器模块,保留rsc1和rsc2寄存器预编码后的状态作为正式编码的初始状态;

6、步骤4:编码器进行turbo正式编码,重复预编码的操作,进行正式编码,输出5路并行比特流;

7、步骤5:编码器进行串行数据输出,串行输出模块对数据进行并串转换,并进行速率匹配,作为编码后的输出序列;

8、步骤6:射频发射,对高码率turbo编码后的输出序列进行调制、射频发射,信号进入无线信道;

9、步骤7:射频接收,从无线信道中接收射频信号,并对其进行解调,得到接收信号,将其送入高码率turbo译码器;

10、步骤8:译码器生成交织索引表及解交织索引表,并存入存储空间;

11、步骤9:译码器提取并行数据,并行数据输入模块将待译码的串行数据处理,转化为输出五路并行信号;

12、步骤10:译码器中siso1子译码器工作,将三路并行信号送入siso1子译码器,同时按照解交织索引表从siso2外信息存储rom中提取数据作为本轮译码的先验信息,将输出的后验信息保存至siso1外信息存储rom1;

13、步骤11:译码器中siso2子译码器工作,siso2子译码器按照交织索引表从siso1的外信息存储rom2中提取数据作为本轮译码的先验信息,同时将三路校验并行信号送入siso2子译码器,保存输出的后验信息至siso2后验信息存储rom中,同时保存译码输出的软信息作为本轮的译码结果,存入译码软信息存储rom;

14、步骤12:译码器进行译码结果校验,对软信息进行crc校验,若校验通过,则进行步骤13,否则判断迭代译码次数是否达到设定的最大次数,若已经达到,进行步骤13,否则返回步骤10;

15、步骤13:译码器判决输出,开始对软信息进行判决输出并截位,得到软判决结果及硬判决结果,同时输出crc校验结果,指示译码正确与否。

16、优选地,crc编码过程为:对长度为25的寄存器,按照生成多项式赋予初值1_1000_0000_0000_0000_0110_0011;将待编码数据后补零24bit,从高位到低位对寄存器内的24位数据进行模二除,得到24位商,即为24bit校验结果,将24bit校验结果添加到待编码数据后,得到crc编码后的数据。

17、优选地,交织器模块采用3gpp标准的交织器,rsc1和rsc2子编码器模块均为3gpp标准下的卷积编码器。

18、优选地,所述步骤5包括:

19、步骤5.1,并串转换:将五路并行信号转换为串行信号,转换顺序为:系统码、rsc1两路输出、rsc2两路输出,并串转换后的串行信号为:

20、

21、步骤5.2,速率匹配:对串行信号进行删余,判决用删余序列表示:

22、

23、其中,n1∈{1,2,…m+24},n2∈{1,2,…m/2+12};m为数据长度,i为序列号;

24、最终得到串行编码比特为:

25、y(i)=yser(i)·d(i),i=1,2,…768。

26、优选地,crc校验过程为:对长度为25的寄存器,按照与crc编码相同的生成多项式赋予初值,将软信息从高位到低位对寄存器内的24位数据进行模二除,得到24位商,即为24bit校验结果,若24bit校验结果为0,表示校验通过;反之,校验未通过。

27、根据本发明提供的构建可配置的高码率turbo编译码器的系统,包括:

28、模块m1:编码器进行crc编码,收到开始编码指示后,crc编码模块对待编码数据进行crc编码,得到crc编码后的数据,将其存入rom存储模块中;

29、模块m2:编码器生成交织索引表,收到开始编码指示后,交织器模块开始工作,产生交织索引表,存入rom存储模块;

30、模块m3:编码器进行turbo预编码,编码准备结束后,将crc编码模块输出的比特序列引入rsc1子编码器模块;同时将交织过的比特序列引入rsc2子编码器模块,保留rsc1和rsc2寄存器预编码后的状态作为正式编码的初始状态;

31、模块m4:编码器进行turbo正式编码,重复预编码的操作,进行正式编码,输出5路并行比特流;

32、模块m5:编码器进行串行数据输出,串行输出模块对数据进行并串转换,并进行速率匹配,作为编码后的输出序列;

33、模块m6:射频发射,对高码率turbo编码后的输出序列进行调制、射频发射,信号进入无线信道;

34、模块m7:射频接收,从无线信道中接收射频信号,并对其进行解调,得到接收信号,将其送入高码率turbo译码器;

35、模块m8:译码器生成交织索引表及解交织索引表,并存入存储空间;

36、模块m9:译码器提取并行数据,并行数据输入模块将待译码的串行数据处理,转化为输出五路并行信号;

37、模块m10:译码器中siso1子译码器工作,将三路并行信号送入siso1子译码器,同时按照解交织索引表从siso2外信息存储rom中提取数据作为本轮译码的先验信息,将输出的后验信息保存至siso1外信息存储rom1;

38、模块m11:译码器中siso2子译码器工作,siso2子译码器按照交织索引表从siso1的外信息存储rom2中提取数据作为本轮译码的先验信息,同时将三路校验并行信号送入siso2子译码器,保存输出的后验信息至siso2后验信息存储rom中,同时保存译码输出的软信息作为本轮的译码结果,存入译码软信息存储rom;

39、模块m12:译码器进行译码结果校验,对软信息进行crc校验,若校验通过,则触发模块m13,否则判断迭代译码次数是否达到设定的最大次数,若已经达到,则触发模块m13,否则触发模块m10;

40、模块m13:译码器判决输出,开始对软信息进行判决输出并截位,得到软判决结果及硬判决结果,同时输出crc校验结果,指示译码正确与否。

41、优选地,crc编码过程为:对长度为25的寄存器,按照生成多项式赋予初值1_1000_0000_0000_0000_0110_0011;将待编码数据后补零24bit,从高位到低位对寄存器内的24位数据进行模二除,得到24位商,即为24bit校验结果,将24bit校验结果添加到待编码数据后,得到crc编码后的数据。

42、优选地,交织器模块采用3gpp标准的交织器,rsc1和rsc2子编码器模块均为3gpp标准下的卷积编码器。

43、优选地,所述模块m5包括:

44、模块m5.1,并串转换:将五路并行信号转换为串行信号,转换顺序为:系统码、rsc1两路输出、rsc2两路输出,并串转换后的串行信号为:

45、

46、模块m5.2,速率匹配:对串行信号进行删余,判决用删余序列表示:

47、

48、其中,n1∈{1,2,…m+24},n2∈{1,2,…m/2+12};m为数据长度,i为序列号;

49、最终得到串行编码比特为:

50、y(i)=yser(i)·d(i),i=1,2,…768。

51、优选地,crc校验过程为:对长度为25的寄存器,按照与crc编码相同的生成多项式赋予初值,将软信息从高位到低位对寄存器内的24位数据进行模二除,得到24位商,即为24bit校验结果,若24bit校验结果为0,表示校验通过;反之,校验未通过。

52、与现有技术相比,本发明具有如下的有益效果:

53、1)码率高:设计了基于fpga的高码率turbo码的编译码器,可完成高于3/4码率的turbo编译码,适应高速率通信需求;

54、2)性能好:在较差的信噪条件下(信噪比小于5db)的情况下,当要达到10-3的误比特率性能时,相较于rs码,采用本发明可带来至少0.5db的增益;

55、3)可移植性强:高码率turbo码编译码器采用模块化设计,编码器可配置编码码率,适用于多场景需求;译码器通过设置译码最大迭代次数,在纠错精度和速度之间实现折中,子译码模块采用乒乓设计,增加了吞吐率;

56、4)适用性好:编码器与译码器硬件资源占用较小,具有较强的适用性。

本文地址:https://www.jishuxx.com/zhuanli/20240801/246644.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表