一种倍乘延迟锁相环和产生稳定时钟信号的方法与流程

- 国知局

- 2024-08-02 15:40:02

本发明涉及锁相环,特别涉及一种倍乘延迟锁相环和产生稳定时钟信号的方法。

背景技术:

1、传统锁相环(phase locked loop)是一个二阶系统,里面的压控振荡器(vco)会使相位误差累积,而且出于环路性能,环路稳定性和环路带宽的考虑,里面的环路滤波器主电容在常规设计里很难小于100pf,所以会占用较大的芯片面积。

2、延迟锁相环(delay locked loop,dll)属于锁相环的一个分支,被广泛地应用于时钟产生电路中。一是更好的噪声性能,因为锁相环采用的压控振荡的传输函数包含一个极点,噪声会累积至下一个周期。而延迟锁相环采用压控延迟线(voltage controlleddelay line,vcdl),不会出现噪声累积。二是因为延迟锁相环传输函数为一阶系统,可以简单地以一个电容作为环路滤波器,但延迟锁相环只能产生一些分立的倍频信号,而且每一个倍频信号要单独占用一个时钟沿组合逻辑,使用起来非常不方便。

3、另一种类似的倍乘延迟锁相环(multiplied delay locked loop,mdll),这个结构可以实现连续的整数倍频输出,在压控延迟线延时大小允许的范围内可以产生更为广泛的输出频率。目前的延迟锁相环主要包括以下几个组成部分,即鉴频器,电荷,滤波器电容,压控延迟线,分频器,二选一选择器,选择器的控制逻辑产生单元。控制逻辑产生单元结构因为插入了一个可编程整数分频器,所以可以产生连续可调的整数倍频输出。这里可以把压控延迟线部分看做是一个时钟沿在延迟线循环n次后,才引入下一个干净的参考时钟沿。对于同样频率的参考时钟,延迟线的长度只有延迟锁相环的1/n,所以压控延迟线模块版图面积更小。控制逻辑产生单元最大的难点在于二选一选择器的选择信号sel的生成,如果设计不合理的话,倍乘延迟锁相环因选择信号时序错误而无法上电锁定,因此相关技术中的倍乘延迟锁相环需搭载辅助设备减小上电锁定误差,达成自启动条件,搭载辅助设备增大了设备体积;并且目前控制逻辑产生单元设计逻辑复杂,电路实现费时费力。

技术实现思路

1、有鉴于此,本发明提供了一种倍乘延迟锁相环和产生稳定时钟信号的方法,以解决目前的倍乘延迟锁相环存在噪声干扰、控制逻辑产生单元设计复杂的问题。

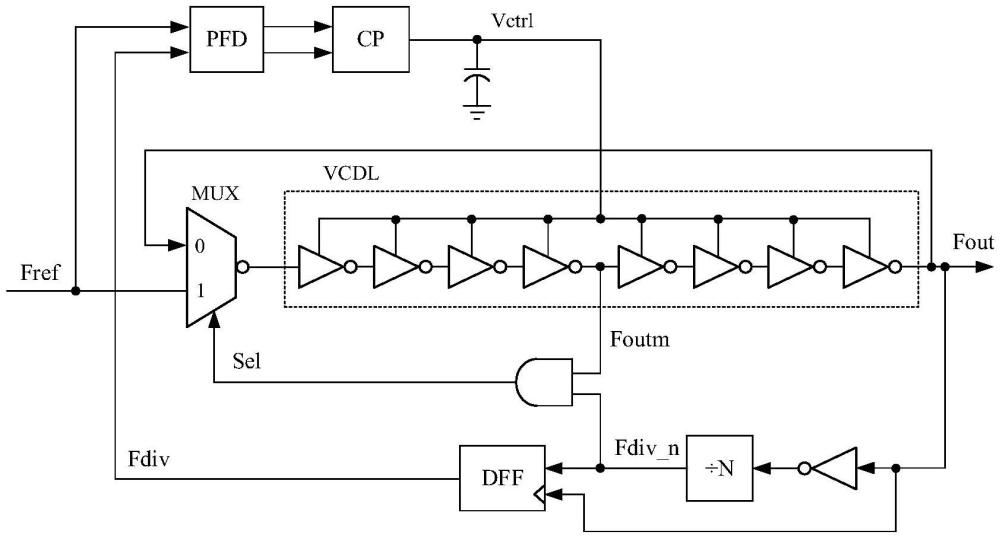

2、第一方面,本发明提供了一种倍乘延迟锁相环,包括鉴频鉴相器pfd、电荷泵cp、环路滤波器、压控延迟线vcdl、二选一选择器mux、第一反相器、分频器n、二输入与门及触发器dff,其中:

3、鉴频鉴相器pfd依次通过电荷泵cp、环路滤波器与压控延迟线vcdl连接;

4、二输入与门包括第一输入端、第二输入端和第一输出端;

5、二输入与门的第一输入端与压控延迟线vcdl连接,压控延迟线vcdl依次通过正向设置的第一反相器、分频器与二输入与门的第二输入端相连接;二输入与门的第一输出端与二选一选择器mux的选择端连接;

6、压控延迟线vcdl用于将输出的时钟信号fout传输至第一反相器,以及用于将时钟信号fout传输至触发器dff的第三输入端;

7、第一反相器用于将时钟信号fout反相处理后传输至分频器n;

8、分频器n用于对反相处理的时钟信号fout分频处理后输出分频信号fdiv_n,以及用于将分频信号fdiv_n传输至二输入与门的第二输入端和触发器dff的第四输入端;

9、二输入与门的第一输入端用于接收压控延迟线vcdl输出的抽头信号foutm,二输入与门的第二输入端用于分频信号fdiv_n,以及用于通过第一输出端将选择信号sel传输至二选一选择器mux;

10、二选一选择器用于根据选择信号sel将输入信号fref传输至压控延迟线vcdl完成倍乘延迟锁相环的压控延迟线时钟输出定期噪声清除;

11、触发器dff用于接收分频信号fdiv_n和时钟信号fout,通过触发器dff的第二输出端输出分频触发信号fdiv至鉴频鉴相器pfd。

12、本发明中提供的倍乘延迟锁相环基于相关技术中的倍乘延迟锁相环进行创新,相关技术中倍乘延迟锁相环内关于二选一选择器mux的选择逻辑模块的设计十分复杂,导致电路设计与实现困难,进一步提高了因误差而造成倍乘延迟锁相环无法自启动的风险;本发明基于该困难点进行了创新,由反相器、分频器n、二输入与门、压控延迟线vcdl和触发器dff构成全新的控制逻辑产生单元,当输入信号fref输入后,该信号经压控延迟线vcdl产生时钟信号fout,时钟信号fout经反相器、分频器n后生成分频信号fdiv_n,本发明中的二输入与门的第一输入端与压控延迟线vcdl连接并接收抽头信号foutm,第二输入端与分频器连接并接收分频信号fdiv_n,二输入与门接收两种信号后输出选择信号sel,选择信号sel控制二选一选择器mux将一个周期的输入信号fref输入至压控延迟线vcdl,触发器dff接收分频信号fdiv_n和时钟信号fout,生成分频触发信号fdiv并将该信号传输至鉴频鉴相器pfd,鉴频鉴相器接收输入信号fref和分频触发信号fdiv并对输入信号fref和时钟信号fout的频率和相位误差进行修正;随着输入信号fref的输入,通过上述逻辑,二选一选择器不断产生选择信号sel,使得压控延迟线vcdl根据输入信号fref不断产生时钟信号fout,并且鉴频鉴相器pfd随着信号的输入不断修正时钟信号fout,即,通过本发明提供的一种倍乘延迟锁相环,在信号输入后,可自启动的产生稳定且误差小的信号输出。

13、在一种可选的实施方式中,二选一选择器mux包括第一端子、第五输入端、第六输入端及第三输出端;

14、第一端子与二输入与门的第一输出端连接,第五输入端与压控延迟线vcdl连接,第六输入端与倍频延迟锁相环输入端连接,第三输出端与压控延迟线vcdl连接。

15、二选一选择器mux基于选择端信号的输入做出不同的输出:当选择端输入高电平信号,二选一选择器mux的第三输出端输出第六输入端的信号;当选择端输入低电平信号,二选一选择器mux的第三输出端输出第五输入端的信号。

16、在一种可选的实施方式中,压控延迟线vcdl包括第二端子、第三端子、第四端子及第五端子;

17、第二端子与二选一选择器mux的第三输出端连接,第三端子与环路滤波器连接,第四端子与倍频延迟锁相环输出端连接,第四端子用于输出时钟信号fout,第五端子与二输入与门的第一输入端连接。

18、在一种可选的实施方式中,压控延迟线包括2n个第二反相器,n≥2;

19、压控延迟线vcdl中的2n个第二反相器均正向串联在第二端子和第四端子之间,2n个第二反相器的压控使能端均与第三端子连接。

20、第二端子指压控延迟线vcdl中包括的2n个第二反相器的第一个第二反相器的输入端,第四端子指压控延迟线vcdl中包括的2n个第二反相器的最后一个第二反相器的输出端。

21、在一种可选的实施方式中,2n个第二反相器中的第n个第二反相器的输出端和第n+1个第二反相器的输入端之间设置有第五端子。

22、在一种可选的实施方式中,环路滤波器包括电容;

23、电容的一端与压控延迟线vcdl的第三端子连接,电容的另一端接地。

24、本发明中的使用的电容容量相比于相关技术中倍乘延迟锁相环中所使用的电容容量更小,同样可达成滤波效果,由于电容容量的使用减小,本发明可使用更小体积的电容达成滤波效果,节省了倍乘延迟锁相环的体积。

25、第二方面,本发明提供了一种产生稳定时钟信号的方法,该方法应用于本发明中的倍乘延迟锁相环,该方法包括:

26、压控延迟线vcdl在接收输入信号fref后,在当前输入信号fref的周期产生时钟信号fout,并将时钟信号fout传输至第一反相器,以及输出抽头信号foutm给二输入与门;

27、第一反相器接收时钟信号fout并进行反相处理,将反相后的时钟信号fout输出至分频器n;

28、分频器n接收反相处理后的时钟信号fout后,生成分频信号fdiv_n,并将分频信号fdiv_n传输至二输入与门的第二输入端和触发器dff的第三输入端;

29、二输入与门的第一输入端接收抽头信号foutm,第二输入端接收分频信号fdiv_n后,与逻辑运算后输出选择信号sel至二选一选择器mux的选择端;

30、在触发器dff的第三输入端接收分频信号fdiv_n,第四输入端接收时钟信号fout后,触发器dff的第二输出端将生成的分频触发信号fdiv传输至鉴频鉴相器pfd;

31、二选一选择器mux的选择端接收选择信号sel后,将对应周期的输入信号fref传输至压控延迟线vcdl;

32、压控延迟线vcdl接收对应周期的输入信号fref后,生成对应周期的输入信号fref的时钟信号fout的上升沿。

33、输入信号fref输入,经过压控延迟线vcdl产生时钟信号fout,时钟信号fout经反相器和分频器n处理生成分频信号fdiv_n,二输入与门接收分频信号fdiv_n和抽头信号foutm生成选择信号sel,选择信号sel在抽头信号foutm处于上升沿且分频信号fdiv_n处于高电平状态下生成高电平的选择信号sel,高电平的选择信号sel输入至二选一选择器mux的选择端,二选一选择器mux将输入信号fref传输至压控延迟线vcdl;触发器dff接收时钟信号fout和分频信号fdiv_n,输出的分频触发信号fdiv与输入信号fref的上升沿保持一致,即,在输入信号fref输入至倍频延迟锁相环后,通过本发明中反相器、分频器n、二输入与门、触发器dff组成的控制逻辑产生单元会根据输入信号fref的输入自启动的同步产生时钟信号fout,且触发器dff输出的分频触发信号fdiv传输至鉴频鉴相器pfd,鉴频鉴相器pfd将基于输入信号fref和分频触发信号fdiv不断修正时钟信号fout的频率和相位与输入信号fref保持一致。

34、在一种可选的实施方式中,在鉴频鉴相器pfd接收输入信号fref和分频触发信号fdiv后:

35、鉴频鉴相器pfd在第一检测周期检测输入信号fref和触发器dff输出的分频触发信号fdiv;

36、如果输入信号fref的频率大于分频触发信号fdiv,鉴频鉴相器pfd输出第一脉冲信号up给电荷泵cp;

37、电荷泵cp接收第一脉冲信号up后进行充电,以及通过提高控制电压vctrl增大压控延迟线vcdl输出的时钟信号fout的频率。

38、倍乘延迟锁相环基于输入信号fref的输入输出时钟信号fout,鉴频鉴相器pfd同时检测基于时钟信号fout的分频触发信号fdiv,当输入信号fref的频率大于分频触发信号fdiv时,通过上述方法,鉴频鉴相器pfd在时钟信号fout输出的同时不断调整时钟信号fout的频率直至与输入信号fref趋近相同。

39、在一种可选的实施方式中,在鉴频鉴相器pfd接收输入信号fref和分频触发信号fdiv后:

40、鉴频鉴相器pfd在第一检测周期检测输入信号fref和触发器dff输出的分频触发信号fdiv;

41、如果输入信号fref的频率小于分频触发信号fdiv,鉴频鉴相器pfd输出第二脉冲信号dn给电荷泵cp;

42、电荷泵cp接收第二脉冲信号dn后进行放电,以及通过降低控制电压vctrl降低压控延迟线vcdl输出的时钟信号fout的频率。

43、倍乘延迟锁相环基于输入信号fref的输入输出时钟信号fout,鉴频鉴相器pfd同时检测基于时钟信号fout的分频触发信号fdiv,当输入信号fref的频率小于分频触发信号fdiv时,通过上述方法,鉴频鉴相器pfd在时钟信号fout输出的同时不断调整时钟信号fout的频率直至分频触发信号fdiv与输入信号fref趋近相同。

44、在一种可选的实施方式中,在输入信号fref处于上升沿时,二输入与门输出高电平信号;

45、二选一选择器mux接收高电平信号,并将输入信号fref输入压控延迟线vcdl,用于定期清除压控延迟线vcdl的噪声。

46、输出的时钟信号fout的分频触发信号fdiv频率和相位需和输入信号fref保持一致,通过上述方法,选择信号sel为高电平时,二选一选择器mux接收该选择信号sel,并将输入信号fref输入压控延迟线vcdl通过选择信号sel的控制,在一个周期的输入信号fref输入后,压控延迟线vcdl产生一组时钟信号fout对应输入信号fref的一个周期,避免了压控延迟线vcdl噪声积累。

本文地址:https://www.jishuxx.com/zhuanli/20240801/247130.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表