一种基于冗余量化的电容失配数字后台校正方法

- 国知局

- 2024-08-02 15:51:26

本发明属于模拟集成电路,特别涉及一种基于冗余量化的电容失配数字后台校正方法。

背景技术:

1、在sar adc的电容失配的数字校正中,基于最陡下降算法的lms(least meansquare,最小均方)算法得到了广泛的应用。lms算法利用迭代来更新adc各位的权重,最终得到符合精度要求的位权重。

2、分裂式adc的lms校正算法主要存在比较明显的两个缺陷:一是需要将adc一分为二,两个adc同时参与权重校正;此操作需要额外的比较器、sar逻辑控制电路,从而增大了面积和功耗开销,将两个子adc电容减半的同时也增大了版图设计难度。二是需要采用某种量化策略,使得两个adc的工作模式不完全相同,否则当两个adc的量化码字相同时lms校正算法失效;这种策略一般是在主电容dac阵列插入辅助的电容dac阵列,在冗余区间内短暂地注入一定偏移量使得adc的工作路线分裂;这种做法增加了面积开销,同时检测冗余区间的信号并注入偏移量需要复杂的逻辑电路。

技术实现思路

1、针对上述存在问题或不足,本发明提供了一种基于冗余量化的电容失配数字后台校正方法,适用于电容dac带冗余的sar adc。本发明方法对冗余区间内的信号进行两次量化,将冗余位依次置0和置1,避免辅助dac的使用同时确保分裂式adc的量化轨迹不完全相同。此处冗余位是指低位电容权重总和大于当前位电容权重的位。低位电容权重总和大于当前位电容权重使得一定范围内的模拟信号可以量化得到两个不同的码字,将这个范围称为冗余区间。

2、由于可以利用低失配的低位电容作为参照,本发明不需要引入额外的高精度adc,对比较器失调也没有严格的要求,冗余量化码字可以在迭代过程中重复使用而不需要重新量化。

3、一种基于冗余量化的电容失配数字后台校正方法,如附图2所示,具体步骤如下:

4、步骤1、生成待冗余量化的模拟信号。

5、对于待校正adc中带冗余的电容dac阵列,参考理想权重下电容dac输出曲线分别选取高n位对应冗余区间的n个信号,n为校正位数。

6、利用额外加载的dac生成所选取的模拟信号输入待校正adc。由于失配导致的最大非线性出现在最高位,中间码字的冗余区间会随机地偏离理想位置。因此依据理想权重下待校正adc中带冗余的电容dac输出曲线选取离中间码字最远的冗余区间取值并令额外加载的dac生成,以避免所选电平不在该位冗余区间内而使校正出错。

7、步骤2、量化步骤1生成的第i位对应冗余区间内的信号(i在n中取值,且i从n到1递减),得到该区间对应冗余位不同的两个码字,具体表示如下:

8、q(vi)=[x1,...xi-1,1,ai+1,...,an,...,an]=[x1,...xi-1,0,bi+1,...,bn,...,bn]

9、其中,n为待校正adc位数。当对第i位冗余区间内的信号进行冗余量化时,由于选定电平处于相应选定冗余区间,于是从最高位到第i-1位为固定的量化码字,可直接根据选定的当前冗余区间赋值并跳过高位比较。量化到第i位时,分别给该位置0和置1,并跳过该位比较,该位之后的比较照常进行。

10、当高n位都冗余量化完成后,将码字存于存储器后进行下一步骤。

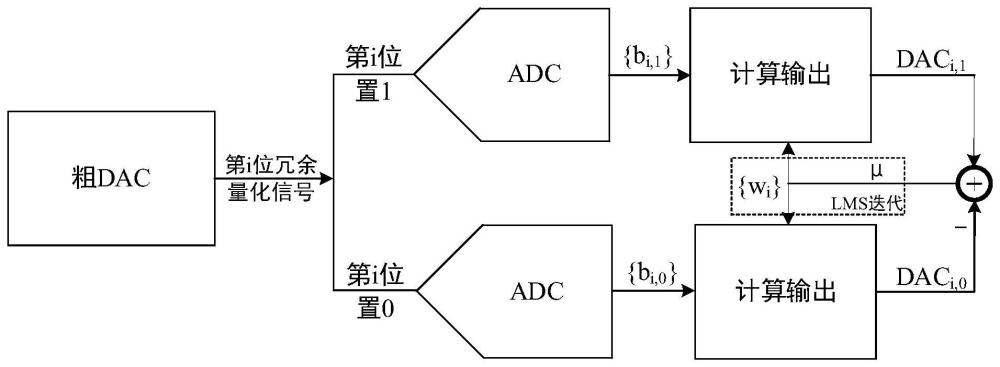

11、步骤3、进行第k次权重迭代,k从1开始取值。

12、从存储器中读出最低校正位第n位的置1量化码和置0量化码,利用理想权重计算冗余输出。理想情况下,非二进制编码[x1,...xi-1,1,ai+1,...,an,...,an]结合真实权重计算得到的冗余输出a与[x1,...xi-1,0,bi+1,...,bn,...,,bn]得到的冗余输出b应相等,如附图1所示。存在失配时,通过校正得到各位权重的精确值后,这两个量也应相等。基于这个等量关系建立误差表达式:

13、ei=(wi+ai+1·wi+1+…+an·wn+…+an·wn)-(bi+1·wi+1+…+bn·wn+…+bn·wn)=0由于低位电容失配较小,我们将低位电容权重作为理想值,用以校正高位电容失配。若存在失配误差,则上式等号不成立:当该位电容实际权重值较当前权重大时,会导致逐次逼近过程中,该位置1操作导致的dac输出节点电压切换偏大,残差偏小,使得后续低位量化该残差时得到的低位码字代表的量与该冗余位当前权重的和偏小,导致误差小于0,此时应该增加该位电容权重值;当该位电容实际权重值较当前权重小时,会导致逐次逼近的过程中该位置1操作导致的dac输出节点电压切换偏小,残差偏大,使得后续低位量化该残差时得到的低位码字代表的量与该冗余位当前权重的和偏大,导致误差大于0,此时应该减小该位电容权重值。基于以上分析,得到本发明校正方法lms迭代格式:

14、wi(k+1)=wi(k)-μ(daci,1(k)-daci,0(k))

15、其中,wi(k)为第i位权重的第k次迭代结果,μ为迭代步长,daci,1(k)、daci,0(k)分别为第i位冗余电平置1和置0量化得到的码字结合第k次迭代得到的各位数字权重计算出来模拟量,daci,1(k)-daci,0(k)即为第k次迭代第i位电容权重误差。

16、通过迭代更新权重,得到该当前位电容相对于低位电容的权重,将最低位到第i位的权重都作为理想权重,用于校正第i-1位电容权重。若当前校正位不是最高位,则采用上述相同校正方法对i-1位进行权重校正;否则重新从第n位开始进行第k+1次权重迭代。根据所需权重精度预设迭代次数k,k达到预设的迭代次数k,迭代停止,校正结束;迭代过程中数字权重不断更新存于存储器中,用以计算adc量化结果。

17、进一步的,所述步骤1中额外加载的dac,采用低精度dac,为片外或片内dac。虽然本发明需要额外的dac,但该额外dac的精度要求较低,可重用性强,可供多通道adc使用,即可片内集成,也可采用片外dac。

18、进一步的,所述步骤3中,在所有位权重均趋于实际相对值时关停校正模块以节省功耗,将最终权重存于存储器中,用以计算adc量化结果。

19、综上所述,对于本发明,由于最低位权重的精度为1,可以直接将迭代步长设置为1,只需要计算1次便可得到计算结果,极大降低了硬件资源的消耗。根据工艺失配情况可灵活调整校正位数,当失配较小时,低位更加趋于理想权重,可以从更高位开始校正,提高校正效率同时减小校正代价。对比电容互换以及dither注入的lms算法,本发明具有更高的校正效率和更简洁的控制逻辑,减小了时间开销和硬件开销。

技术特征:1.一种基于冗余量化的电容失配数字后台校正方法,其特征在于,具体步骤如下:

2.如权利要求1所述基于冗余量化的电容失配数字后台校正方法,其特征在于:所述步骤1中额外加载的dac,采用低精度dac,为片外或片内dac。

3.如权利要求1所述基于冗余量化的电容失配数字后台校正方法,其特征在于:所述步骤3中,在所有位权重均趋于实际相对值时关停校正模块以节省功耗。

技术总结本发明属于模拟集成电路技术领域,具体为一种基于冗余量化的电容失配数字后台校正方法。本发明配合带冗余的电容DAC阵列实现,通过对冗余区间内的信号进行两次量化,将冗余位依次置0和置1,避免辅助DAC的使用同时确保分裂式ADC的量化轨迹不完全相同;由于最低位权重的精度为1,可直接将迭代步长设置为1,只需要计算1次便可得到计算结果,极大降低了硬件资源的消耗。并且本发明根据工艺失配情况可灵活调整校正位数,当失配较小时,低位更加趋于理想权重,可从更高位开始校正,提高校正效率同时减小校正代价。对比电容互换以及dither注入的LMS算法,本发明具有更高的校正效率和更简洁的控制逻辑,减小了时间开销和硬件开销。技术研发人员:张中,钟明灿,何禹,李靖,宁宁,于奇受保护的技术使用者:电子科技大学技术研发日:技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240801/248203.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表