一种SOT-MRAM存储器单元及其制备方法与流程

- 国知局

- 2024-08-02 15:51:52

本发明涉及微电子制造,尤其是涉及一种sot-mram存储器单元及其制备方法。

背景技术:

1、近年来,采用磁性隧道结(mtj)的磁电阻效应的磁性随机存储器(mram,magneticradom access memory)被人们认为是未来的固态非易失性记忆体,它具有高速读写、大容量以及低能耗的特点。铁磁性mtj通常为三明治结构,其中有磁性记忆层,它可以改变磁化方向以记录不同的数据;位于中间的绝缘的隧道势垒层;磁性参考层,位于隧道势垒层的另一侧,它的磁化方向不变。

2、sot-mram(spin orbit torque-magnetic access memory)具有非易失性,高速低功耗数据写入能力以及高器件耐久性等优点,正逐步成为继自旋转移矩随机存储器(stt-mram,spin transfer torque-magnetic random access memory)后新一代随机存储器,并成为有望突破后摩尔时代集成电路功耗瓶颈的关键技术。

3、sot-mram能够产生翻转源于自旋轨道矩效应重金属层的强自旋轨道耦合(spainorbit coupling,soc)作用,因此,sot往往被需要具有很大的自旋电荷转换效率,以提高sot-mram的翻转效率;还被需要具有较大的自旋电导率,以此降低sot-mram器件使用过程中因电阻率过大带来的功率损耗。

4、但是,现有技术中自旋轨道耦合层材料的自旋霍尔角较小,即电流与自旋流之间的转化效率较低,能量损耗较大,使得产生的自旋流较小,难以诱导磁性自由层的磁矩发生翻转,导致读取速度降低。而自旋霍尔角大的拓扑绝缘体具有较大的自旋霍尔效应,但导电率低。因此,对于sot-mram,提升其翻转效率和降低电阻率成为技术难点。

5、鉴于此,特提出本发明。

技术实现思路

1、本发明的目的在于提供一种sot-mram存储器单元及其制备方法,该sot-mram存储器单元隧道结tmr均值可达100%以上。

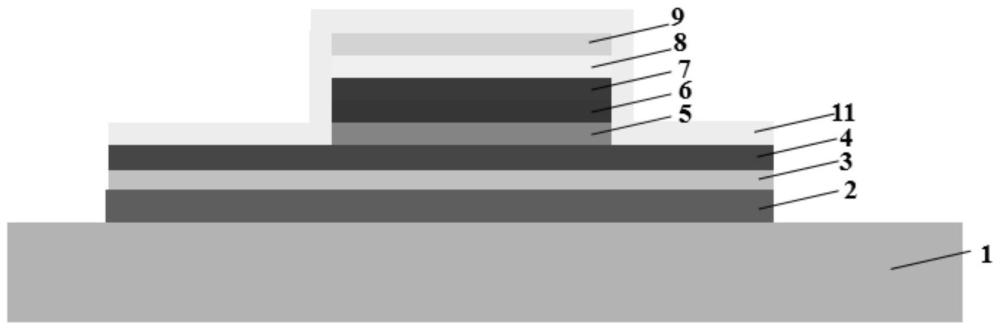

2、本发明提供一种sot-mram存储器单元,包括自下而上依次设置的底电极层、磁隧道结、反铁磁层和顶电极层,所述磁隧道结包括自由层、隧穿层和钉扎层,其中,所述底电极层为w金属层和ta金属层呈奇数设置的叠层结构。

3、作为本技术方案优选地,本发明所述底电极层的厚度优选为3.25-8.5nm,其中,所述底电极层中w金属层和ta金属层的厚度优选比为1:(0.18-0.38),且所述底电极层中靠近衬底晶圆的一侧为w金属层。

4、例如,底电极层的总层数为3层,总厚度为3.25nm,其中,靠近衬底晶圆一侧的w金属层的厚度为1.25nm,中间层ta金属层的厚度为0.5nm,最上层w金属层的厚度为1.25nm。

5、底电极层的总层数为5层,总厚度为5nm,其中,沿衬底晶圆向顶电极层延伸的方向,依次为w金属层(厚度为1.25nm),ta金属层(厚度为0.5nm),w金属层(厚度为1.25nm),ta金属层(厚度为0.5nm),w金属层(厚度为1.5nm)。

6、底电极层的总层数为7层,总厚度为6.75nm,其中,沿衬底晶圆向顶电极层延伸的方向,依次为w金属层(厚度为1.25nm),ta金属层(厚度为0.5nm),w金属层(厚度为1.25nm),ta金属层(厚度为0.5nm),w金属层(厚度为1.25nm),ta金属层(厚度为0.5nm),w金属层(厚度为1.5nm)。

7、底电极层的总层数为9层,总厚度为8.5nm,其中,沿衬底晶圆向顶电极层延伸的方向,依次为w金属层(厚度为1.25nm),ta金属层(厚度为0.5nm),w金属层(厚度为1.25nm),ta金属层(厚度为0.5nm),w金属层(厚度为1.25nm),ta金属层(厚度为0.5nm),w金属层(厚度为1.25nm),ta金属层(厚度为0.5nm),w金属层(厚度为1.5nm)。

8、研究表明,本发明底电极层w和ta厚度比的选择兼顾了自旋轨道耦合层材料对高自旋流转化率和低电阻率的需求。

9、作为本技术方案优选地,所述自由层包括cofeb合金层,所述隧穿层包括mgo层,所述钉扎层包括cofeb合金层,所述顶电极层包括ta金属层和ru金属层。

10、作为本技术方案优选地,所述反铁磁层包括w金属层、co金属层、pt金属层和ru金属层。

11、作为本技术方案优选地,所述存储器单元还包括衬底晶圆和保护层,所述衬底晶圆、所述底电极层、所述自由层、所述隧穿层、所述钉扎层、所述反铁磁层、所述顶电极层和所述保护层自下而上依次设置,所述保护层为sin。

12、作为本技术方案优选地,所述自由层为cofeb,所述隧穿层为mgo,所述钉扎层为cofeb,所述顶电极层为ta/ru和ta层,所述反铁磁层为w/co/[pt/co]m pt/co/ru/co/[pt/co]npt,其中,[pt/co]m的含义为pt/co层重复m次,m为1-4,[pt/co]n中的n为4-8。

13、第二方面,本发明还提供了上述sot-mram存储器单元的制备方法,包括以下步骤:

14、s1、在衬底晶圆上依次形成底电极层、自由层、隧穿层、钉扎层、反铁磁层、顶电极层和硬掩模层;

15、s2、通过光刻和刻蚀,将图形转移到硬掩模层上;

16、s3、以硬掩模层作为掩模,刻蚀顶电极层;

17、s4、以顶电极层作为掩模,刻蚀反铁磁层和钉扎层,停止在隧穿层的表面;

18、s5、沉积保护层;

19、s6、光刻图形化刻蚀底电极层。

20、作为本技术方案优选地,步骤s1中,首先在衬底晶圆上进行cmp,使其粗糙度ra值小于0.3nm,然后溅射沉积底电极层;其中,所述溅射沉积前进行除气,所述除气时,控制温度为250-300℃,时间为20-60s。

21、作为本技术方案优选地,步骤s4中,刻蚀反铁磁层和钉扎层时,采用离子束进行刻蚀,离子束的方向角为30-60°,能量50-200v,保护气体为氩气。

22、本发明的sot-mram存储器单元,至少具有以下技术效果:

23、本发明以w和ta呈奇数设置的叠层结构作为底电极层,其具有较高的自旋霍尔角和较低的电阻,电流与自旋流之间的转化效率较高,产生的垂直于电流方向的自旋流较高,使得能够自旋轨道耦合层能够更快地翻转磁性自由层的磁化方向,提高读取速度。

24、其中,自由层为cofeb,隧穿层为mgo,钉扎层为cofeb,反铁磁层为w/co/[pt/co]mpt/co/ru/co/[pt/co]npt和顶电极层为ta/ru,叠层薄膜沉积在以w为表面界面的底电极上,由此可以实现自由层、钉扎层、反铁磁层的垂直各向异性,并且实现了钉扎层和反铁磁层的铁磁耦合。

25、因此,在上述各层级结构的相互作用下,本发明的sot-mram存储器单元隧道结tmr均值可达100%以上。

本文地址:https://www.jishuxx.com/zhuanli/20240801/248246.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。