一种高精度低功耗的10bitSARADC电路的制作方法

- 国知局

- 2024-08-02 12:48:59

本发明涉及一种adc电路,特别是一种高精度低功耗的10bit sar adc电路,属于半导体集成电路。

背景技术:

1、模数转换器是一种能够将连续变化的模拟信号转换为相应的数字编码的工具,是现代电子设备必备的电路模块,其按照电路结构可细分为过采样σ-δadc、逐次逼近型adc、流水线型adc、全并行闪烁型adc等,其中逐次逼近型adc结构简单,仅需要一个比较器、一个采样保持电路、一些控制逻辑和寄存器等,且其功耗会随着采样率的变化而变化,更适合低功耗的应用。

2、传统的逐次逼近型模数转换器的dac电路多采用以下两种结构,第一种是把一串等值的电阻放置于参考电压v_ref和地之间,并且每个电阻的端点电压都由一个开关来控制引出作为分段参考电压,通过控制开关即可实现按照二进制搜索算法来将相应的分段参考电压送至比较器,但电阻串dac输出电容大,且开关控制的信号线庞杂,n位dac就需要2^n条单独的开关控制信号线,虽然单调性良好,但很大程度上增加了电路的功耗和芯片的面积。

3、如图12所示是现有技术的8位电阻阵列dac的电路示意图。它是将基准电压vref转换成一组28个电压值,它们可根据输入码字被译码为单个模拟输出电压。电压定标型dac通常是使用连接在vref和地之间的串联电阻的选择来获得vref范围内的电压。在电阻阵列的每个节点和输出之间只有一个开关,开关的闭合取决于逻辑电路,它由一个8:28的译码器组成。假如不需要输出驱动电流,且电阻阵列满足dac的匹配误差,则电压定标型dac具有良好的精度。但其模拟输出端总是连接着2n-1个关断的开关和一个导通的开关,当n的值较大时,输出节点的寄生电容也随之增大,降低了每一次的转换速度。此外,该结构还难以保证面积与功耗之间的平衡。当n的值较大时,结构需要大量的电阻,占用了大量的芯片面积,且电阻的匹配精度不高,导致其积分非线性inl较差。但其也有可取之处,比如该结构与cmos工艺兼容性好,且由于其任意抽头的电压都不低于其下任意抽头的电压,故单调性很好,具有良好的微分非线性dnl。

4、第二种是利用电容通过电荷再分配来完成二进制搜索算法,其具有功耗低的优点,常采用并行电容,即使用二进制加权电容阵列和一个与lsb电容等值的冗余电容,但是该结构的问题在于电容阵列的匹配误差会引入非线性误差,且二进制加权的电容阵列随着逐次逼近型adc位数的增多,电容值呈指数级上升,不但降低了转换速度,也增加了芯片的面积。

5、如图13所示是现有技术的8位电容阵列dac的电路示意图。这种结构的dac采用一个并联的电容阵列,在该阵列中,每个电容的大小为二进制权重乘以单位电容c,因此总电容为28c。其中有一个单位电容c为冗余电容,只参与采样,在转换过程中一直接地,256c为比较器另一端的匹配电容,该匹配电容可以有效减小在比较过程中存在的电容漏电问题。整个da过程可分为三步,第一步为采样,将电容的下极板均接至vin,上极板接vcm,此时在上极板存储的电荷为q=256c*(vcm-vin);第二步为保持,vcm的开关断开,电容的下极板均由vin切换到地,由电荷守恒可知此时比较器负端的电压为vx=vcm-vin;第三步为量化,首先将最高位电容即128c的下极板接至vref,其他电容的下极板保持接地不变,则由电荷守恒可得:256c*(vcm-vin)=128c*(vx-vref)+128c*vx,则可知比较器负端的电压增加了当时,比较器输出高电位,则最高位的数字码为1,当时,比较器输出低电位,则最高位的数字码为0。当最高位输出1时,则最高位开关不变,次高位电容的下极板接至vref,其余电容保持接地,继续下一步量化过程;当最高位输出0时,则最高位电容的下极板切换至地,次高位电容的下极板接至vref,其余电容保持接地,继续下一步量化过程。以此类推,重复以上过程,直至确定每一位的数字输出。该结构不消耗直流功耗,且电容的匹配精度比电阻更高,但随着dac位数的增加,最高位电容的面积呈指数级上升,故消耗了很多面积。

技术实现思路

1、本发明所要解决的技术问题是提供一种高精度低功耗的10bit sar adc电路,减小了adc电路的功耗和芯片面积。

2、为解决上述技术问题,本发明所采用的技术方案是:

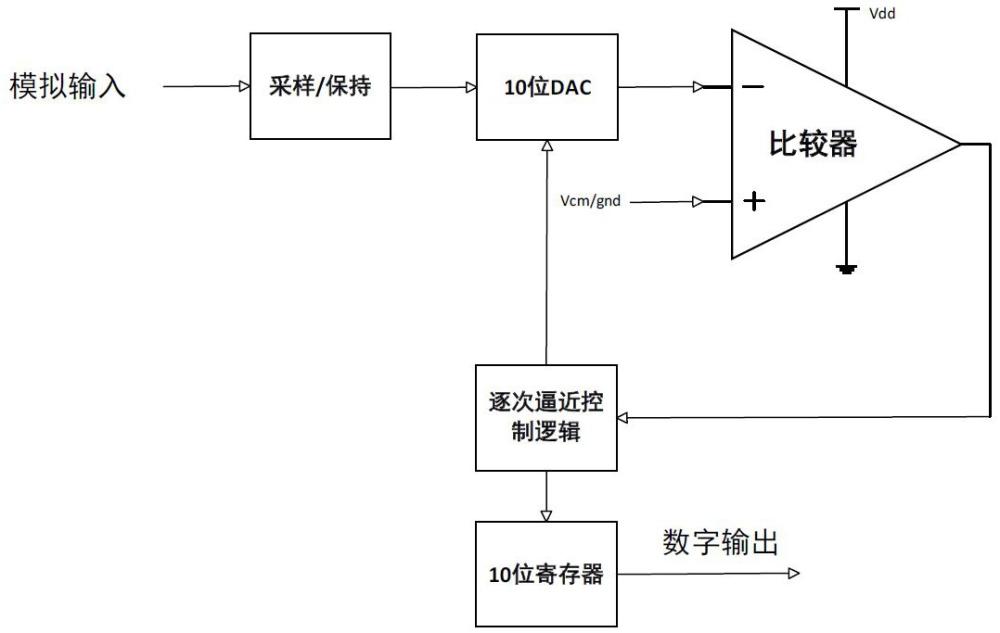

3、一种高精度低功耗的10bit sar adc电路,包含采样保持模块、10位dac模块、比较器模块、逐次逼近控制逻辑模块和寄存器模块,采样保持模块的输入端连接模拟输入信号,采样保持模块的输出端与10位dac模块的输入端连接,10位dac模块的输出端与比较器模块的反向输入端连接,比较器模块的同向输入端连接vcm或接地,比较器模块的输出端连接逐次逼近控制逻辑模块的输入端,逐次逼近控制逻辑模块的第一输出端与10位dac模块的控制端连接,逐次逼近控制逻辑模块的第二输出端与寄存器模块的输入端连接,寄存器模块的输出端输出10bit输出代码。

4、进一步地,所述10位dac模块包含高五位电阻阵列和低五位电容阵列,高五位电阻阵列采用32个阻值相同的电阻将vdd分成32个一级区间,然后低五位电容阵列继续将电阻划分的每个一级区间再次细分为32个二级子区间。

5、进一步地,所述高五位电阻阵列包含电阻res1、电阻res2、...、电阻res32,电阻res1、电阻res2、...、电阻res32依次串联,电阻res1的一端接地,电阻res32的一端连接vdd,对于电阻res1~电阻res17中的任意一个电阻resp,电阻resp的一端与第一开关的一端连接,第一开关的另一端连接基准电压vref2,电阻resp的另一端与第二开关的一端连接,第二开关的另一端连接基准电压vref1,其中第一开关和第二开关均由信号res_ctrlp控制,1≤p≤17;对于电阻res18~电阻res21中的任意一个电阻resq,电阻resq的一端与第一晶体管开关的一端连接,第一晶体管开关的另一端连接基准电压vref2,电阻resq的另一端与第二晶体管开关的一端连接,第二晶体管开关的另一端连接基准电压vref1,第一晶体管开关和第二晶体管开关分别包含第一晶体管和第二晶体管,第一晶体管和第二晶体管的两端分别相接,第一晶体管由信号res_ctrlq控制,第二晶体管由信号res_ctrlqn控制,17≤q≤32。

6、进一步地,所述电阻res1、电阻res2、...、电阻res32的电阻相等且均为10kω。

7、进一步地,所述低五位电容阵列包含第一电容阵列、第二电容阵列、第三电容阵列、第四电容阵列、第五电容阵列、第六电容阵列和第七电容阵列,第一电容阵列、第二电容阵列、第三电容阵列、第四电容阵列、第五电容阵列、第六电容阵列和第七电容阵列的容量分别为4c、64c、32c、16c、8c、4c和2c,第一电容阵列、第二电容阵列、第三电容阵列、第四电容阵列、第五电容阵列、第六电容阵列和第七电容阵列的一端连接比较器单元的反向输入端并通过开关连接共模电压vcm,第一电容阵列的另一端通过两个开关分别连接输入电压vin和基准电压vref2,第二电容阵列、第三电容阵列、第四电容阵列、第五电容阵列和第六电容阵列的另一端通过三个开关分别连接输入电压vin、基准电压vref1和基准电压vref2,第七电容阵列的另一端通过两个开关分别连接电压信号vdd/32和接地,第八电容阵列的一端通过开关连接电压信号vdd/2,第八电容阵列的另一端连接比较器模块的同向输入端。

8、进一步地,所述第一电容阵列、第二电容阵列、第三电容阵列、第四电容阵列、第五电容阵列、第六电容阵列、第七电容阵列和第八电容阵列均由两个等值的电容并联构成。

9、进一步地,所述比较器模块包含第一二级放大器、第二二级放大器、第三二级放大器、电容c1、电容c2、电容c3、电容c4、反相器inv1和反相器inv2,第一二级放大器包含nmos管m1、nmos管m2、nmos管m3、pmos管m4、pmos管m5、pmos管m6、pmos管m7、pmos管m8、pmos管m9、nmos管m10、nmos管m11、nmos管m12和nmos管m13,nmos管m1的源极接地,nmos管m1的栅极连接偏置信号bias1,nmos管m1的漏极与nmos管m2的源极和nmos管m3的源极连接,nmos管m2的栅极连接信号vinp,nmos管m3的栅极连接信号vinn,nmos管m2的漏极与pmos管m4的漏极、pmos管m4的栅极、pmos管m8的栅极、pmos管m6的栅极和pmos管m7的漏极连接,nmos管m3的漏极与pmos管m5的漏极、pmos管m5的栅极、pmos管m9的栅极、pmos管m7的栅极和pmos管m6的漏极连接,pmos管m4、pmos管m5、pmos管m6、pmos管m7、pmos管m8和pmos管m9的源极连接电源vdd,pmos管m8的漏极与电容c2的一端、nmos管m10的漏极和nmos管m13的漏极的连接,pmos管m9的漏极与电容c1的一端、nmos管m11的漏极和nmos管m12的漏极的连接,nmos管m10的栅极与nmos管m12的栅极连接,nmos管m13的栅极与nmos管m11的栅极连接,nmos管m10、nmos管m11、nmos管m12和nmos管m13的源极接地;

10、第二二级放大器包含nmos管m14、nmos管m15、nmos管m16、pmos管m17、pmos管m18、pmos管m19、pmos管m20、pmos管m21、pmos管m22、nmos管m23、nmos管m24、nmos管m25和nmos管m26,nmos管m14的源极接地,nmos管m14的栅极连接偏置信号bias2,nmos管m14的漏极与nmos管m15的源极和nmos管m16的源极连接,nmos管m15的栅极与电容c1的另一端和开关s1的一端连接,nmos管m16的栅极与电容c2的另一端和开关s2的一端连接,nmos管m15的漏极与开关s1的另一端、pmos管m17的漏极、pmos管m17的栅极、pmos管m21的栅极、pmos管m19的栅极和pmos管m20的漏极连接,nmos管m16的漏极与开关s2的另一端、pmos管m8的漏极、pmos管m8的栅极、pmos管m22的栅极、pmos管m20的栅极和pmos管m19的漏极连接,pmos管m17、pmos管m18、pmos管m19、pmos管m20、pmos管m21和pmos管m22的源极连接电源vdd,pmos管m21的漏极与电容c4的一端、nmos管m23的漏极和nmos管m26的漏极的连接,pmos管m22的漏极与电容c3的一端、nmos管m24的漏极和nmos管m25的漏极的连接,nmos管m23的栅极与nmos管m25的栅极连接,nmos管m26的栅极与nmos管m24的栅极连接,nmos管m23、nmos管m24、nmos管m25和nmos管m26的源极接地;

11、第三二级放大器包含nmos管m25、nmos管m26、nmos管m27、pmos管m28、pmos管m29、pmos管m30、pmos管m31、pmos管m32、pmos管m33、nmos管m34、nmos管m35、nmos管m36和nmos管m37,nmos管m25的源极接地,nmos管m25的栅极连接偏置信号bias3,nmos管m25的漏极与nmos管m26的源极和nmos管m27的源极连接,nmos管m26的栅极与电容c4的另一端和开关s3的一端连接,nmos管m27的栅极与电容c3的另一端和开关s4的一端连接,nmos管m26的漏极与开关s3的另一端、pmos管m28的漏极、pmos管m28的栅极、pmos管m32的栅极、pmos管m30的栅极和pmos管m31的漏极连接,nmos管m27的漏极与开关s4的另一端、pmos管m29的漏极、pmos管m29的栅极、pmos管m33的栅极、pmos管m31的栅极和pmos管m30的漏极连接,pmos管m28、pmos管m29、pmos管m30、pmos管m31、pmos管m32和pmos管m33的源极连接电源vdd,pmos管m32的漏极与nmos管m34的漏极和nmos管m37的漏极的连接,pmos管m33的漏极与反相器inv1的输入端、nmos管m35的漏极和nmos管m36的漏极的连接,nmos管m34的栅极与nmos管m36的栅极连接,nmos管m37的栅极与nmos管m35的栅极连接,nmos管m34、nmos管m35、nmos管m36和nmos管m37的源极接地,反相器inv1的输出端与反相器inv2的输入端连接,反相器inv2的输出端输出信号comp_out。

12、进一步地,所述逐次逼近控制逻辑模块包含移位寄存器模块、控制信号产生模块、多路选择器mux模块和控制信号输出模块;移位寄存器模块包含12个首位相连的d触发器,相邻两个d触发器中,前一个d触发器的q端与后一个d触发器的d端连接,所有d触发器的set端均连接置位信号set,相邻两个d触发器的时钟控制信号反相,从第二个d触发器开始,任意一个d触发器的q端输出时钟控制信号ck<a>,1≤a≤11,任意一个d触发器的端输出时钟控制信号ckn<a>,1≤a≤11;

13、控制信号产生模块包含反相器inv3、反相器inv4、与非门nand1、反相器inv5和10条信号产生支路,反相器inv3的输入端输入信号comp_out,反相器inv3的输出端与反相器inv4的输入端连接,反相器inv4的输出端与与非门nand1的第一输入端连接,与非门nand1的第二输入端输入控制信号ck<1>,与非门nand1的输出端与反相器inv5的输入端连接,反相器inv5的输出端与10条信号产生支路的输入端连接,每条信号产生支路包含反相器inv6、与非门nand2、与非门nand3、与非门nand4、与非门nand5和反相器inv7,反相器inv6的输入端与反相器inv5的输出端连接,反相器inv6的输出端与与非门nand2的第一输入端连接,与非门nand2的第二输入端连接控制信号ckn<a>,2≤a≤11,与非门nand3的第一输入端连接控制信号ck<a>,2≤a≤11,与非门nand3的第二输入端与反相器inv5的输出端连接,与非门nand2的输出端与与非门nand4的第一输入端连接,与非门nand4的第二输入端与与非门nand5的输出端连接,与非门nand4的输出端与反相器inv7的输入端和与非门nand5的第一输入端连接,与非门nand3的输出端与与非门nand5的第二输入端连接,反相器inv7的输出端输出控制信号dac_ctrlb,1≤b≤10;

14、多路选择器mux模块包含10路mux选择器支路,每一路mux选择器支路包含选择器mux、反相器inv8和反相器inv9,选择器mux的in0端输入控制信号dac_ctrlb,第1路mux选择器支路的选择器mux的in1端输入信号d1,第2路至第10路mux选择器支路的选择器mux的in1端输入控制信号ck<a>,选择器mux的s端输入控制信号ckn<a>,选择器mux的out端与反相器inv8的输入端连接,反相器inv8的输出端与反相器inv9的输入端连接并输出控制信号dac_stepbn,1≤b≤10,反相器inv9的输出端输出控制信号dac_stepb,1≤b≤10;

15、控制信号输出模块包含32路控制信号输出支路,每一路控制信号输出支路分别包含与非门nand6、反相器inv10、与非门nand7、反相器inv11和反相器inv12,与非门nand6的第一输入端输入控制信号dac_step5,与非门nand6的第二输入端输入控制信号dac_step4,与非门nand6的输出端与反相器inv10的输入端连接,反相器inv10的输出端与与非门nand7的第一输入端连接,与非门nand7的第二输入端输入控制信号dac_step3,与非门nand7的第三输入端输入控制信号dac_step2,非门nand7的第四输入端输入控制信号dac_step1,与非门nand7的输出端与反相器inv11的输入端连接,反相器inv11的输出端与反相器inv12的输入端连接并输出控制信号res_ctrld,1≤d≤32,第1路至第17路控制信号输出支路的反相器inv12的输出端无输出信号,第17路至第32路控制信号输出支路的反相器inv12的输出端输出控制信号res_ctrlen,18≤e≤32。

16、进一步地,所述寄存器模块包含10路寄存器支路,每一路寄存器支路包含与非门nand8、反相器inv13、反相器inv14和反相器inv15,与非门nand8的第一输入端输入信号en_adc_out,与非门nand8的第二输入端输入控制信号dac_ctrlb,与非门nand8的输出端与反相器inv13的输入端连接,反相器inv13的输出端与反相器inv14的输入端连接,反相器inv14的输出端与反相器inv15的输入端连接,反相器inv15的输出端输出信号adc_outb,1≤b≤10。

17、本发明与现有技术相比,具有以下优点和效果:

18、1、本发明的高精度低功耗的10bit sar adc电路提出了一种结合电阻和电容阵列的新型结构,在保证了adc具有良好的线性度、单调性和精度之外,大大减小了电路的功耗和版图的面积;

19、2、本发明的比较器模块采用了3个二级放大器级联,且每一级放大器都采用了交叉耦合对技术,大大增加了放大器的增益,且级间加入了输出失调存储技术,有效降低了比较器的输入失调电压;

20、3、本发明的移位寄存器采用反相的时钟信号触发,相比于采用同一个时钟信号触发,节省了一半的量化时间。

本文地址:https://www.jishuxx.com/zhuanli/20240802/237950.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表