一种用于提供溯源参考的高精度网络时间源的制作方法

- 国知局

- 2024-08-05 11:58:11

本申请涉及时间溯源与校准,尤其涉及一种用于提供溯源参考的高精度网络时间源。

背景技术:

1、网络时间协议(ntp,network time protocol)和精确时间协议(ptp,precisiontime protocol)是通过将时钟与计算机网络链接来然后同步时间的两个协议标准。时钟和计算机上的精确和连接时间显示对人们的工作、生活和社会的运行有着重要作用。如果时间显示出现问题,时间同步系统还可以使问题故障排除变得更容易,因为人们可以准确地看到问题发生的时间,进而定位问题发生地点和方位。ntp协议用于通过数据包交换的可变延迟数据网络在计算机系统之间进行时钟同步。ptp协议的结构框架和ntp(网络时间协议)类似,内部有不同的层级,gps、北斗、伽利略等卫星可以作为时间源。但是,ntp和ptp之间的主要区别在于ptp精确到微秒甚至纳秒级别,意味着它比ntp更精确。

2、从溯源角度,要求用于溯源参考的网络时间源精度比被校准的网络时间同步设备精度高出至少一个数量级。但现有的ptp网络时间源、ntp网络时间源与被校准的网络时间同步设备精度在同一量级,无法作为溯源参考。如何提高ntp/ptp网络时间同步精度成为需要解决的技术问题。

技术实现思路

1、本申请实施例提供一种用于提供溯源参考的高精度网络时间源,解决了现有技术的ntp/ptp网络时间同步精度较低的问题。

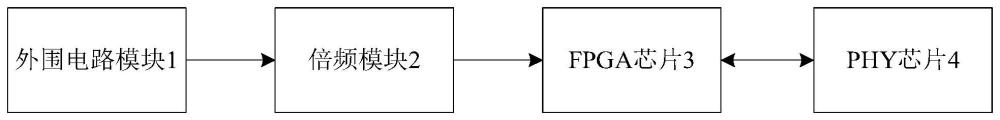

2、所述一种用于提供溯源参考的高精度网络时间源,包括外围电路模块、倍频器模块、fpga芯片和phy芯片;所述外围电路模块包括电源和频率源;其中:所述电源为外围电路模块、倍频器模块、fpga芯片和/或phy芯片供电;所述频率源提供兆赫兹频率信号至倍频器模块,所述倍频器模块将所述兆赫兹频率信号进行倍频放大生成g赫兹时钟信号并输出至fpga芯片;所述fpga芯片包括通过编程方式实现的mac层;所述fpga芯片采用g赫兹时钟信号进行计数,在mac层标记时间戳,通过mac层接口与所述phy芯片基于g赫兹时钟信号进行数据交互。

3、优选地,所述phy芯片包括gmii或rgmii接口,通过所述gmii或rgmii接口与fpga芯片的mac层接口进行数据交互。

4、优选地,所述fpga芯片还包括:接口复用单元、udp协议栈单元和/或时间同步协议栈单元;在接收链路中,所述fpga芯片通过mac层从phy芯片接收数据,所述接收数据经过接口复用单元、udp协议栈单元、时间同步协议栈单元进行处理得到时间同步数据;在发送链路中,时间同步协议栈单元将时间同步数据经过udp协议栈单元、接口复用单元、mac层发送至phy芯片;在接收和发送过程中,时间同步协议栈单元生成打入时间同步数据包的时间戳的脉冲。

5、优选地,所述时间同步协议栈单元为ptp协议栈单元;所述fpga芯片与phy芯片通过gmii或rgmii接口进行数据交互;在接收链路中,通过mac层接口获得从phy芯片进入fpga芯片的mac层数据,接口复用单元将mac层数据分为第一部分、第二部分数据,所述第一部分数据通过ps的emio mac接口发送给ps进行处理,所述第二部分数据送入udp协议栈单元完成数据的解析,解析完成的数据送至ptp协议栈单元进行处理;在发送链路中,ptp协议栈单元完成时间同步数据的组帧操作,将组帧后的时间同步数据送至udp协议栈单元完成udp、ip和/或mac层的组帧,接口复用单元将udp组帧数据与ps emio mac的数据完成复用后发送至mac层接口,将复用后的数据从fpga芯片发送至phy芯片。

6、优选地,所述时间同步协议栈单元为ntp协议栈单元;所述fpga芯片与phy芯片通过gmii或rgmii接口进行数据交互;接收链路中,通过mac层接口获得从phy芯片进入fpga芯片的mac层数据,接口复用单元将mac层数据分为第一部分、第二部分数据,所述第一部分数据通过ps的emio mac接口发送给ps进行处理,所述第二部分数据送入udp协议栈单元完成数据的解析,解析完成的数据送至ntp协议栈单元进行处理;在发送链路中,ntp协议栈单元完成时间同步数据的组帧操作,将组帧后的时间同步数据送至udp协议栈单元完成udp、ip和/或mac层的组帧,接口复用单元将udp组帧数据与ps emio mac的数据完成复用后发送至mac层接口,将复用后的数据从fpga芯片发送至phy芯片。

7、优选地,在所述udp组帧形成的udp报文中封装有时钟同步报文。

8、优选地,所述电源为每路输出提供4a电流的四通道dc/dc降压型的模块稳压器;所述倍频器模块为从10mhz倍至100mhz再从100mhz倍至1ghz的高稳时钟产生模块;所述fpga芯片为具有四核高性能处理器和可编程逻辑的融合芯片;所述phy芯片为符合10base te、100base-tx和1000base-tieee 802.3标准的高度集成以太网收发器。

9、优选地,udp协议栈单元运行于1ghz的以太网phy芯片时钟域下。

10、优选地,所述ptp协议栈单元需实现sync、follow_up、delay_req、announce、delay_resp或signaling六种报文。

11、优选地,所述udp协议栈单元在接收链路接收到mac层的数据包后,按照mac层、ip层、udp层的帧结构依次解帧,并判断该数据包的目的mac地址和目的ip地址是否为本机ip地址,若不是本机地址则丢弃该数据包;

12、在udp解包时,如果目的端口号不是123、319或320端口,则丢弃该数据包。

13、本申请实施例采用的上述至少一个技术方案能够达到以下有益效果:

14、本申请的用于提供溯源参考的高精度网络时间源,可以适用于作为ptp/ntp网络时间源,通过提高时钟周期至g赫兹、将时间戳标记位置最大限度靠近物理层、提高时间戳标记时钟等方式,该时间源的ptp/ntp时间同步精度可以有效控制在5ns以内,能作为溯源参考,满足所有网络时间同步设备的校准需求。

技术特征:1.一种用于提供溯源参考的高精度网络时间源,其特征在于,包括外围电路模块、倍频器模块、fpga芯片和phy芯片;所述外围电路模块包括电源和频率源;其中:

2.根据权利要求1所述的一种用于提供溯源参考的高精度网络时间源,其特征在于,所述phy芯片包括gmii或rgmii接口,通过所述gmii或rgmii接口与fpga芯片的mac层接口进行数据交互。

3.根据权利要求1所述的一种用于提供溯源参考的高精度网络时间源,其特征在于,所述fpga芯片还包括:接口复用单元、udp协议栈单元或时间同步协议栈单元;

4.根据权利要求1所述的一种用于提供溯源参考的高精度网络时间源,其特征在于,所述时间同步协议栈单元为ptp协议栈单元;所述fpga芯片与phy芯片通过gmii或rgmii接口进行数据交互;

5.根据权利要求1所述的一种用于提供溯源参考的高精度网络时间源,其特征在于,所述时间同步协议栈单元为ntp协议栈单元;所述fpga芯片与phy芯片通过gmii或rgmii接口进行数据交互;

6.根据权利要求5所述的一种用于提供溯源参考的高精度网络时间源,其特征在于,在所述udp组帧形成的udp报文中封装有时钟同步报文。

7.根据权利要求4或5中任一项所述的一种用于提供溯源参考的高精度网络时间源,其特征在于,

8.根据权利要求1所述的一种用于提供溯源参考的高精度网络时间源,其特征在于,

9.根据权利要求5或6中任一项所述的一种用于提供溯源参考的高精度网络时间源,其特征在于,udp协议栈单元运行于1ghz的以太网phy芯片时钟域下。

10.根据权利要求5所述的一种用于提供溯源参考的高精度网络时间源,其特征在于,所述ptp协议栈单元实现sync、follow_up、delay_req、announce、delay_resp或signaling报文。

技术总结本申请公开了一种用于提供溯源参考的高精度网络时间源,包括外围电路模块、倍频器模块、FPGA芯片和PHY芯片;外围电路模块包括电源和频率源;其中:电源为外围电路模块、倍频器模块、FPGA芯片或PHY芯片供电;频率源提供兆赫兹频率信号至倍频器模块,所述倍频器模块将所述兆赫兹频率信号进行倍频放大生成G赫兹时钟信号并输出至FPGA芯片;所述FPGA芯片包括通过编程方式实现的MAC层;所述FPGA芯片采用G赫兹时钟信号进行计数,在MAC层标记时间戳,通过MAC层接口与所述PHY芯片基于G赫兹时钟信号进行数据交互。应用本发明提高了PTP/NTP网络时间源的精度在5ns以内,能够作为溯源参考。技术研发人员:杨帆,乔彩霞,张然受保护的技术使用者:北京无线电计量测试研究所技术研发日:技术公布日:2024/8/1本文地址:https://www.jishuxx.com/zhuanli/20240802/260367.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表