基于五输入多数门的QCA电路

- 国知局

- 2024-08-30 15:04:49

本发明涉及纳米集成电路,尤其涉及一种基于五输入多数门的qca电路。

背景技术:

1、传统的cmos技术已经规范了纳米技术行业几十年。纳米级cmos的实现面临着严峻的挑战,如大漏电流、高功耗和高光刻成本。这些挑战对集成电路(ic)的发展产生了重大影响。据著名的国际半导体技术路线图(itrs)报道,提出了替代技术,如碳纳米管场效应晶体管(cnfet)、纳米线和量子点细胞自动机(qca)。其中,qca可以有效克服cmos的缺点。

2、qca可以为ic设计人员提供新的解决方案,目前也已经提出了部分结构,其中多数门结构作为基础部件使用频率很高。但是目前提出的结构也存在部分问题,例如功耗较高,使用元胞数量较多,使用旋转元胞或多层结构实现信号传输等,这使得基于此类结构构建的电路成本增加,扩展性差。正因为如此,设计低功耗高扩展性的结构应提上日程。

技术实现思路

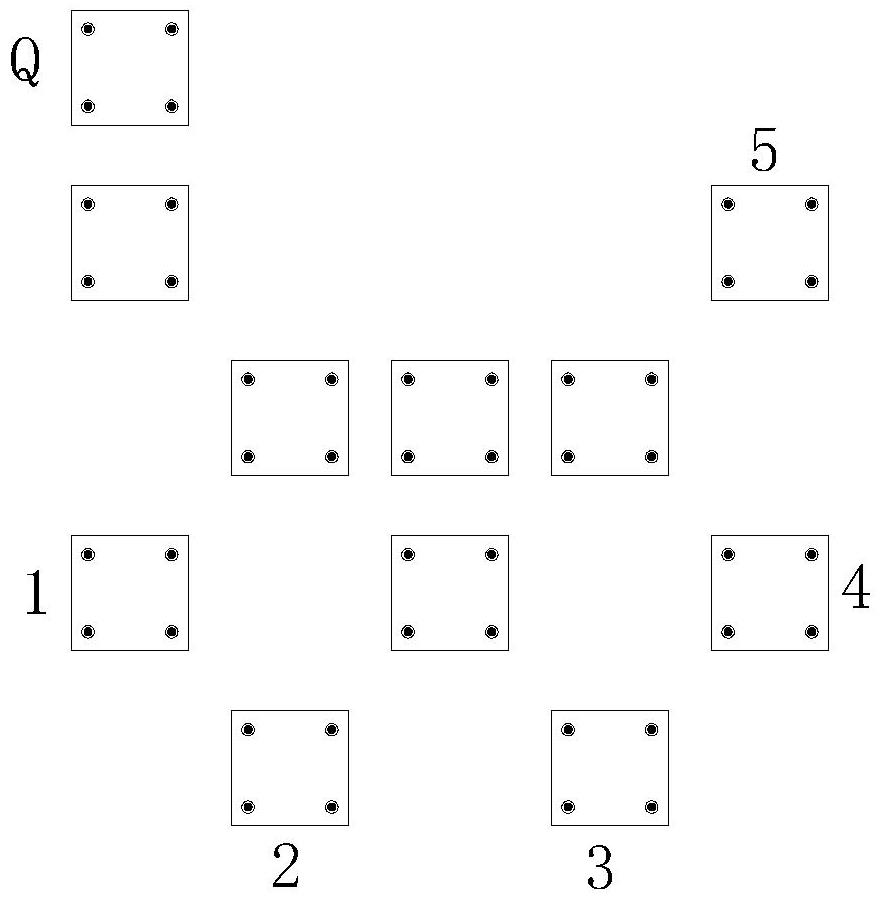

1、本发明旨在至少在一定程度上解决相关技术中的技术问题之一。为此,本发明的一个目的在于提出一种基于五输入多数门的qca电路,多数门具有高极化,低功耗和低成本的优点,并且基于此门提出全加器,多路复用器和d触发器。

2、根据本发明提出的一种基于五输入多数门的qca电路,包括均由量子元胞组成的全加器、2-1多路复用器和d触发器;

3、所述全加器包括一组三输入多数门一、二组反相器一和一组五输入多数门一,所述三输入多数门一的信号输入端分别外接有三组输入信号a、b、c,所述三输入多数门一的信号输出端分别通过两组所述反相器一与所述五输入多数门一的两组信号输入端口连接,所述五输入多数门一的剩余三组信号输入端口分别与信号a、b、c连接,所述五输入多数门一的信号输出端口作为全加器的信号输出端口;

4、所述2-1多路复用器包括一组三输入多数门二、一组反相器二和一组五输入多数门二,所述三输入多数门二的信号输入端分别外接有三组输入信号s、y和二进制信号0,所述五输入多数门二的两组信号输入端口共连与所述三输入多数门二的信号输出端连接,所述输入信号s还通过所述反相器二与所述五输入多数门二的一组信号输入端口连接,所述五输入多数门二的剩余两组信号输入端口分别与信号h和二进制信号1连接,所述五输入多数门二的信号输出端口作为2-1多路复用器的信号输出端口;

5、所述d触发器包括所述2-1多路复用器、输出返回线路、输入信号d和输入信号clk,所述输入信号d和所述输入信号clk与所述2-1多路复用器的信号输入端连接,所述2-1多路复用器的信号输出端通过所述输出返回线路与所述2-1多路复用器的信号输入端连接。

6、优选地,在所述全加器中:

7、三组输入信号a、b、c分别为加数信号a、加数信号b和低位进位信号c,所述加数信号a由两组连接线路分别与所述三输入多数门一信号输入端口1和五输入多数门一信号输入端口4连接,所述加数信号b由两组连接线路分别与所述三输入多数门一信号输入端口2和五输入多数门一信号输入端口5连接,所述低位进位信号c由两组连接线路分别与所述三输入多数门一信号输入端口3和五输入多数门一信号输入端口1连接,所述三输入多数门一信号输出端口4分别通过两组所述反相器一线路与所述五输入多数门一信号输入端口2和五输入多数门一信号输入端口3连接。

8、优选地,所述加数信号a与所述三输入多数门一信号输入端口1连接的线路、所述加数信号b与所述三输入多数门一信号输入端口2连接的线路和所述低位进位信号c与所述三输入多数门一信号输入端口3连接的线路均经过时钟0传入所述三输入多数门一信号输入端;

9、所述加数信号a与所述五输入多数门一信号输入端口4连接的线路、所述加数信号b与所述五输入多数门一信号输入端口5连接的线路和所述低位进位信号c与所述五输入多数门一信号输入端口1连接的线路均经过时钟0、时钟1和时钟2传入所述五输入多数门一信号输入端;

10、所述三输入多数门一的量子元胞均为时钟1;

11、所述五输入多数门一信号输入端口的量子元胞均为时钟2,所述五输入多数门一信号输出端口为时钟3;

12、所述三输入多数门一信号输出端口4分别与所述五输入多数门一信号输入端口2和五输入多数门一信号输入端口3连接的线路均通过时钟1和时钟2传入所述五输入多数门一信号输入端。

13、优选地,在所述2-1多路复用器中:

14、所述二进制信号0与所述三输入多数门二的信号输入端口1连接,所述输入信号y与所述三输入多数门二的信号输入端口2连接,所述输入信号s由两组连接线路分别与所述反相器二的信号输入端口和所述三输入多数门二的信号输入端口3连接,所述反相器二的信号输出端口与所述五输入多数门二的输入端口4连接,所述三输入多数门二的信号输出端口4由两组连接线路分别与五输入多数门二的信号输入端口2和五输入多数门二的信号输入端口3连接,所述输入信号h与所述五输入多数门二的信号输入端口5连接,所述二进制信号1与所述五输入多数门二的输入端口1连接。

15、优选地,所述三输入多数门二的信号输入端口1的量子元胞极化为-1表示为二进制信号0输入,所述输入信号y与所述三输入多数门二的信号输入端口2连接的线路、所述输入信号s与所述三输入多数门二的信号输入端口3连接的线路均经过时钟0传入所述三输入多数门二的信号输入端,所述输入信号s与所述五输入多数门二的信号输入端口4连接的线路经过时钟0和时钟1传入所述五输入多数门二的信号输入端口,所述输入信号h经过时钟1传入所述五输入多数门二的信号输入端口,所述五输入多数门二的信号输入端1与二进制信号1连接的量子元胞极化为1表示为二进制信号1输入;

16、所述三输入多数门二的量子元胞均为时钟1;

17、所述三输入多数门二的信号输出端4分别与所述五输入多数门二的信号输入端2和所述五输入多数门二的信号输入端3连接的线路均通过时钟1传入所述五输入多数门二的信号输入端;

18、所述五输入多数门二的信号输入端口1、五输入多数门二的信号输入端口4、五输入多数门二的信号输入端口5和五输入多数门二的信号输出端口均为时钟2,所述五输入多数门二的信号输入端口2和五输入多数门二的信号输入端口3均为时钟1。

19、优选地,在所述d触发器中:

20、所述2-1多路复用器中的五输入多数门二的信号输出端口q通过所述输出返回线路与所述五输入多数门二的信号输入端口5连接,所述输入信号clk由两组连接线路分别与所述2-1多路复用器的所述反相器二的信号输入端口和所述三输入多数门二的信号输入端口3连接,所述输入信号d与所述2-1多路复用器中的所述三输入多数门二的信号输入端口2连接。

21、优选地,所述输入信号d与所述三输入多数门二的信号输入端口2连接的线路、所述输入信号clk与所述三输入多数门二的信号输入端口3连接的线路均经过时钟0传入所述三输入多数门二的信号输入端,所述输入信号clk与所述五输入多数门二的信号输入端口4连接的线路经过时钟0和时钟1传入所述五输入多数门二的信号输入端口,所述输出返回线路依次经过上一时钟周期的时钟3、下一时钟周期的时钟0、时钟1、时钟2传出。

22、本发明中的有益效果是:五输入多数门使用极化状态和非极化状态两种类型的元胞;全加器、2-1多路复用器和d触发器均使用四种时钟方案实现电路中数据的传输;它们都包括多数门和反相器结构;并且使用更加稳定的共面交叉布线实现器件的联通;降低了qca电路的功耗,增加了电路的可扩展性,同时使用五输入多数门组建电路,可以减少元胞数量,减小占用面积;使用更少的极化元胞实现设计,减小设计复杂性。

本文地址:https://www.jishuxx.com/zhuanli/20240830/285409.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。