UVM验证平台及验证、生成方法、装置、系统、介质、设备与流程

- 国知局

- 2024-09-14 14:25:59

本发明涉及计算机,具体涉及一种uvm验证平台及验证、生成方法、装置、系统、介质、设备。

背景技术:

1、随着大规模集成电路的发展和摩尔定律的不断应验,单位面积上晶体管的数量变的越来越多,一块芯片上可以集成数以千万计的电路,而随着设计复杂程度的提高,对验证的要求也随之越来越高。使用vhdl和verilog语言进行验证的传统方式虽然现在还有使用,但是弊端已经逐渐显现,比如代码数量巨大、验证效率低下、激励无法自动生成等。对复杂系统而言,传统的验证方式将会消耗极大的人力成本与时间成本,更难以保证验证的完备性。

2、通用验证方法学(universal verification methodology,uvm)基于systemverilog语言,通过构建一个包含多种类的库。uvm具有带约束随机激励产生、标准化验证组件等特点,为验证提供极大的便利,是现在业界认可度最高且使用最普遍的验证方法学。

3、相对于传统verilog验证方法,基于uvm的验证方法需要一些额外的组件用于激励的产生、通信和检查,代码量有所增加,结构更加复杂,但是功能也更加强大。总的来说,uvm框架大同小异,基于这个特点,在验证平台的具体搭建过程中,使用脚本成为一种通用的、高效的方式。

4、目前,已有的uvm验证平台在实现时,主要是针对某一种既定设计,通过分析需求,来搭建一个有针对性的uvm验证平台。对于不同的待验模块(device under test,dut),如果每个dut都单独搭建一uvm验证平台,会使得每个uvm验证平台的通用性较差,验证dut时工作量较大。

技术实现思路

1、本发明要解决的问题是:提升uvm验证平台的通用性。

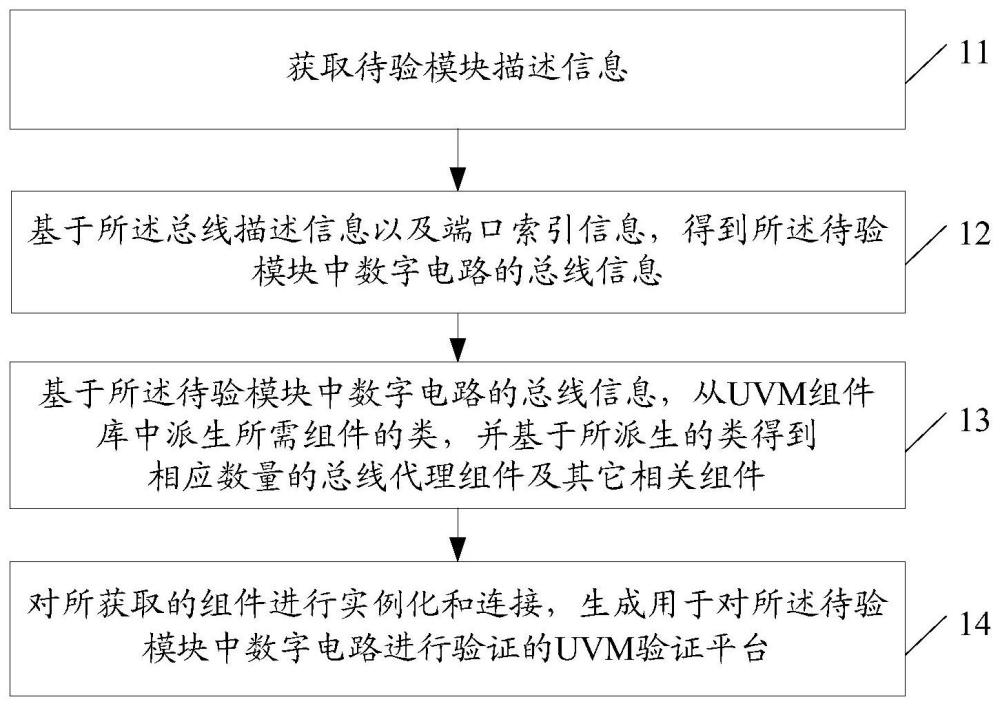

2、为解决上述问题,本发明实施例提供了一种uvm验证平台生成方法,所述方法包括:

3、获取待验模块描述信息,所述待验模块描述信息包括:所述待验模块中数字电路的总线描述信息以及端口索引信息;

4、基于所述总线描述信息以及端口索引信息,得到所述待验模块中数字电路的总线信息;

5、基于所述待验模块中数字电路的总线信息,从uvm组件库中派生所需组件的类,并基于所派生的类得到相应数量的总线代理组件及其它相关组件;

6、对所获取的组件进行实例化和连接,生成用于对所述待验模块中数字电路进行验证的uvm验证平台。

7、可选地,当所述待验模块描述信息中还包括寄存器信息时,所述方法还包括:

8、针对所述待验模块中数字电路的每种总线,生成寄存器模型,并将所述寄存器模型自动集成在顶层环境中。

9、可选地,所述寄存器信息包括:通过转换器组件访问所述寄存器模型的总线标识信息;

10、所述其它相关组件包括:与通过转换器组件访问所述寄存器模型的总线相对应的转换器组件。

11、可选地,当所述待验模块中还包括模拟电路,且所述待验模块描述信息中还包括数模混合仿真需求信息时,所述方法还包括:

12、获取所述待验模块中模拟电路所对应的等效数字模块信息;

13、基于所述等效数字模块标识信息生成模拟电路仿真文件,以用于对所述待验模块中模拟电路进行仿真。

14、可选地,所述待验模块描述信息还包括非总线描述信息;

15、所述方法还包括:

16、基于所述非总线描述信息,得到所述待验模块中数字电路的非总线信息,并基于所述待验模块中数字电路的非总线信息,从uvm组件库中获取相应数量的非总线代理组件。

17、本发明实施例还提供了一种uvm验证平台生成装置,所述装置包括:

18、信息获取单元,适于获取待验模块描述信息,所述待验模块描述信息包括:所述待验模块中数字电路的总线描述信息以及端口索引信息;

19、总线信息生成单元,适于基于所述总线描述信息以及端口索引信息,得到所述待验模块中数字电路的总线信息;

20、组件获取单元,适于基于所述待验模块中数字电路的总线信息,从uvm组件库中派生所需组件的类,并基于所派生的类得到相应数量的总线代理组件及其它相关组件;

21、例化连接单元,适于对所获取的组件进行实例化和连接,生成用于对所述待验模块中数字电路进行验证的uvm验证平台。

22、可选地,所述装置还包括:

23、寄存器模型生成单元,适于当所述待验模块描述信息中还包括寄存器信息时,针对所述待验模块中数字电路的每种总线,生成寄存器模型,并将所述寄存器模型自动集成在顶层环境中。

24、可选地,所述寄存器信息包括:通过转换器组件访问所述寄存器模型的总线标识信息;

25、所述其它相关组件包括:与通过转换器组件访问所述寄存器模型的总线相对应的转换器组件。

26、可选地,所述装置还包括:

27、混仿处理单元,适于当所述待验模块中还包括模拟电路,且所述待验模块描述信息中还包括数模混合仿真需求信息时,获取所述待验模块中模拟电路所对应的等效数字模块信息,基于所述等效数字模块标识信息生成模拟电路仿真文件,以用于对所述待验模块中模拟电路进行仿真。

28、可选地,所述待验模块描述信息还包括非总线描述信息;所述组件获取单元还适于:基于所述非总线描述信息,得到所述待验模块中数字电路的非总线信息,并基于所述待验模块中数字电路的非总线信息,从uvm组件库中派生所需组件的类,并基于所派生的类得到相应数量的非总线代理组件。

29、本发明实施例还提供了一种uvm验证平台,所述uvm验证平台采用上任一种的uvm验证平台生成方法生成。

30、可选地,所述待验模块还包括:模拟电路;

31、所述验证平台还包括:

32、选择器,第一输入端与所述模拟电路的端口连接,第二输入端与所述模拟电路的等效数字模块连接,输出端与所述待验模块的数字电路连接;

33、所述选择器,适于接收仿真控制指令,并基于所述接收仿真控制指令,将所述模拟电路与所述待验模块的数字电路连接,或者将所述模拟电路的等效数字模块与所述待验模块的数字电路连接;其中,所述仿真控制指令包括数模混合仿真控制指令或数字仿真控制指令。

34、本发明实施例还提供了一种uvm验证方法,所述方法包括:

35、获取所述待验模块对应的测试用例信息;

36、采用上述任一种所述的uvm验证平台生成方法所生成的uvm验证平台,对所述待验模块中数字电路进行验证。

37、可选地,所述待验模块还包括:模拟电路;

38、所述uvm验证平台还包括:

39、选择器,第一输入端与所述模拟电路的端口连接,第二输入端与所述模拟电路的等效数字模块连接,输出端与所述待验模块的数字电路连接;

40、所述选择器,适于接收仿真控制指令,并基于所述接收仿真控制指令,将所述模拟电路与所述待验模块的数字电路连接,或者将所述模拟电路的等效数字模块与所述待验模块的数字电路连接;其中,所述仿真控制指令包括数模混合仿真控制指令或数字仿真控制指令。

41、可选地,所述方法还包括:

42、当接收到所述数模混合仿真指令时,将所述模拟电路与所述待验模块的数字电路连接,并对所述待验模块的数字电路及模拟电路进行混合仿真;

43、当接收到所述数字仿真控制指令,将所述模拟电路的等效数字模块与所述待验模块的数字电路连接,并对所述待验模块的数字电路进行仿真。

44、本发明实施例还提供了一种uvm验证系统,所述系统包括:

45、上述任一种的uvm验证平台生成装置;

46、以及上述的uvm验证平台。

47、本发明实施例还提供了一种计算机存储可读存储介质,其上存储有计算机程序,所述计算机程序被处理器执行,以实现上述任一种所述方法的步骤。

48、本发明实施例还提供了一种电子设备,包括存储器和处理器,所述存储器上存储有能够在所述处理器上运行的计算机程序,所述处理器运行所述计算机程序时执行上述任一种所述方法的步骤。

49、与现有技术相比,本发明实施例的技术方案具有以下优点:

50、应用本发明的方案,通过获取待验模块描述信息,进而可以基于待验模块中数字电路的总线描述信息以及端口索引信息,得到待验模块中数字电路的总线信息,基于所述待验模块中数字电路的总线信息,从uvm组件库中派生所需组件的类,并基于所派生的类得到相应数量的总线代理组件及其它相关组件,最终可以对所获取的组件进行实例化和连接,生成用于对所述待验模块中数字电路进行验证的uvm验证平台。采用该方案,基于待验模块中数字电路的总线信息,去获取总线代理组件,从而可以为每种总线单独生成一个子环境,最终生成的uvm验证平台,是可以扩展总线的uvm结构,从而可以使得该uvm验证平台的灵活性更高,通用性更强,可以明显降低验证dut的工作量。

本文地址:https://www.jishuxx.com/zhuanli/20240914/294024.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表