一种熔丝更新电路、方法、存储器、电子设备及存储介质与流程

- 国知局

- 2024-09-14 14:49:09

本技术涉及存储器,尤其涉及一种熔丝更新电路、方法、存储器、电子设备及存储介质。

背景技术:

1、近年来,随着半导体技术的发展与普及,诸多存储器开始使用熔丝(efuse)技术或反熔丝(anti-fuse)技术来存储芯片数据。熔丝技术的原理是通过熔断金属或聚合物的方式将芯片数据编程到存储单元中,在编程为“1”的存储单元中会有一个明显的开口,而编程为“0”的存储单元中不存在开口。与熔丝技术相对应的,反熔丝技术的原理是根据量子穿隧效应在存储单元的单晶体氧化层上形成导电路径,无论是编程为“1”的存储单元,还是编程为“0”的存储单元,其表面上都没有可见的痕迹,看起来并无明显差异。

2、然而,无论是熔丝技术还是反熔丝技术,其对存储单元的烧写操作都是不可逆的。芯片在每次上电启动后,都会加载采用熔丝技术或反熔丝技术烧写在存储单元中的芯片数据。但由于某些原因(比如烧写出错、存储单元老化或磨损或者使用环境发生变化等)影响,导致原有的芯片数据无法再适用于当前的使用环境,甚至导致用于存储芯片数据的存储单元的性能出现问题时,若想不影响芯片的可用性,则需要对芯片进行熔丝更新,比如将性能出现问题的存储单元中的芯片数据存储到其它的备用电路中,或者在其它的备用电路中配置满足当前使用需求的新的芯片数据等。

3、目前,虽然业界提出了一些对芯片进行熔丝更新的方案,但这些方案仅仅只能在某个特定的模式下使用新配置的备用电路或新的芯片数据,而无法实现对芯片进行熔丝更新的长久性。因此,目前对芯片熔丝更新的长久性方面还有待进一步研究。

技术实现思路

1、本技术提供一种熔丝更新电路、方法、存储器、电子设备及存储介质,用以实现芯片熔丝更新的长久性。

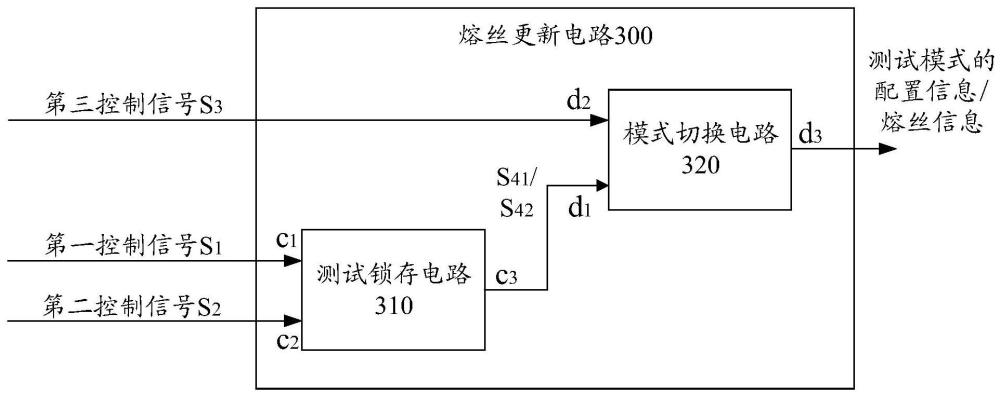

2、第一方面,本技术提供一种熔丝更新电路,该熔丝更新电路包括测试锁存电路和模式切换电路,测试锁存电路的第一输入端用于接收第一控制信号,测试锁存电路的第二输入端用于接收第二控制信号,测试锁存电路的输出端连接模式切换电路的第一输入端,模式切换电路的第二输入端用于接收第三控制信号。测试锁存电路用于在第二控制信号呈现为有效电平时输出第一信号,以及,用于在第二控制信号呈现为无效电平且第一控制信号呈现为有效电平时输出第二信号;模式切换电路用于在第三控制信号呈现为无效电平时,若测试锁存电路输出第一信号,则加载测试模式的配置信息,若测试锁存电路输出第二信号,则加载熔丝信息。

3、需要说明的是,上述第一控制信号是指与是否退出测试模式相关的信号,在接收到测试命令时,该第一控制信号的电平被翻转为无效电平,芯片进入测试模式,反之,在接收到测试退出命令时,该第一控制信号的电平被翻转为有效电平,芯片退出测试模式。上述第二控制信号是指与是否锁存测试模式的配置信息相关的信号,在接收到测试锁存命令时,该第二控制信号的电平被翻转为有效电平,反之,在未接收到测试锁存命令时,该第二控制信号的电平被翻转为无效电平。上述第三控制信号是指与芯片上电相关的信号,在接收到上电命令后,芯片上电启动,该第三控制信号的电平被翻转为有效电平,并在一段时间后被芯片中的其它配置电路自动恢复为无效电平。

4、另外,上述有效电平和无效电平是指电平相反的两个电平,比如,有效电平为“1”电平且无效电平为“0”电平,或者,有效电平为“0”电平且无效电平为“1”电平。

5、在上述设计中,熔丝更新电路可以支持根据实际需求选择锁存或不锁存测试模式的配置信息,当需要长时间锁存测试模式时,可以触发第二控制信号翻转为有效电平,如此,即使后续退出测试模式,也仍旧可以继续使用测试模式的配置信息,而不需要在每次需要测试模式的配置信息时都重新进入测试模式,有效节省用户或测试人员的工作量,提高测试人员的测试体验或者用户的使用体验。反之,当不需要长时间锁存测试模式时,可配置第二控制信号呈现为无效电平,此时熔丝更新电路即可在退出测试模式后自动切换回熔丝信息。可见,该种熔丝更新电路既能支持需要对熔丝更新进行长久性锁存的场景,又能支持不需要对熔丝更新进行长久性锁存的场景,其灵活性和通用性较好。

6、一种可能的设计中,测试锁存电路还可以用于:在第二控制信号呈现为无效电平且第一控制信号呈现为无效电平时,输出第一信号。也即是说,即使指示不锁存测试模式,只要未退出测试模式,则熔丝锁存电路就会继续加载测试模式的配置信息,如此,能确保在测试模式期间顺利加载测试模式的配置信息。

7、一种可能的设计中,模式切换电路还可以用于:在第三控制信号呈现为有效电平时,加载熔丝信息。通过该设计,芯片在每次重新启动后,都能重新切换回原本的熔丝信息,有助于实现芯片的初始化。

8、一种可能的设计中,当有效电平为“1”电平且无效电平为“0”电平时:

9、测试锁存电路用于实现如下逻辑:在第一控制信号的电平为“1”和/或第二控制信号的电平为“1”时,输出“0”电平;以及,在第一控制信号和第二控制信号的电平都为“0”时,输出“1”电平;

10、以及,模式切换电路用于实现如下逻辑:在第三控制信号的电平为“1”和/或测试锁存电路的输出信号的电平为“1”时,加载熔丝信息;以及,在第三控制信号和测试锁存电路的输出信号的电平都为“0”时,加载测试模式的配置信息。

11、另一种可能的设计中,当有效电平为“0”电平且无效电平为“1”电平时:

12、测试锁存电路用于实现如下逻辑:在第一控制信号的电平为“0”和/或第二控制信号的电平为“0”时,输出“1”电平;以及,在第一控制信号和第二控制信号的电平都为“1”时,输出“0”电平。

13、以及,模式切换电路用于实现如下逻辑:在第三控制信号的电平为“0”和/或测试锁存电路的输出信号的电平为“0”时,加载熔丝信息;以及,在第三控制信号和测试锁存电路的输出信号的电平都为“1”时,加载配置信息。

14、应理解,凡是能够实现如上逻辑的测试锁存电路和模式切换电路均在本技术的保护范围内。

15、示例性地,下面以有效电平为“1”电平且无效电平为“0”电平为例,给出几种测试锁存电路和模式切换电路的具体设计。

16、电路设计一,测试锁存电路包括第一非门、与非门和第二非门,第一非门的输入端为测试锁存电路的第二输入端,第一非门的输出端连接与非门的第二输入端,与非门的第一输入端为测试锁存电路的第一输入端,与非门的输出端连接第二非门的输入端,第二非门的输出端为测试锁存电路的输出端。对此对应的,模式切换电路包括或非门和模式选择器,或非门的第一输入端为模式切换电路的第一输入端,或非门的第二输入端为模式切换电路的第二输入端,或非门的输出端连接模式选择器,模式选择器用于在接收到高电平时,输出测试模式的配置信息,在接收到低电平时,输出熔丝信息。

17、在上述电路设计一中,测试模式的配置信息的优先权高于熔丝信息,也即是说,即使熔丝信息已经烧写在存储单元中,也能通过测试模式来重新设置所需要的配置信息,并能在使用过程中通过触发第二控制信号,使得芯片即使退出了测试模式也能使用在测试模式下所设置的配置信息,实现熔丝更新的长久性。

18、电路设计二,测试锁存电路包括非门和与门,非门的输入端为测试锁存电路的第二输入端,非门的输出端连接与门的第二输入端,与门的第一输入端为测试锁存电路的第一输入端,与门的输出端为测试锁存电路的输出端。对此对应的,模式切换电路包括或非门和模式选择器,或非门的第一输入端为模式切换电路的第一输入端,或非门的第二输入端为模式切换电路的第二输入端,或非门的输出端连接模式选择器,模式选择器用于在接收到高电平时,输出测试模式的配置信息,在接收到低电平时,输出熔丝信息。

19、上述电路设计二不仅能实现与上述电路设计一相同的熔丝更新逻辑,而且还能比电路设计一中的测试锁存电路少一个非门,该熔丝更新电路的结构更为简单,电路成本更低,有助于实现芯片的小型化设计。

20、电路设计三,测试锁存电路包括第一非门、或门和第二非门,第一非门的输入端为测试锁存电路的第一输入端,第一非门的输出端为或门的第一输入端,或门的第二输入端为测试锁存电路的第二输入端,或门的输出端为第二非门的输入端,第二非门的输出端为测试锁存电路的输出端。对此对应的,模式切换电路包括或非门和模式选择器,或非门的第一输入端为模式切换电路的第一输入端,或非门的第二输入端为模式切换电路的第二输入端,或非门的输出端连接模式选择器,模式选择器用于在接收到高电平时,输出测试模式的配置信息,在接收到低电平时,输出熔丝信息。

21、上述电路设计三通过在测试锁存电路中设置一个或门和两个非门,也能实现与上述电路设计一相同的熔丝更新逻辑。

22、在上述电路设计一至三的进一步设计中,模式切换电路还可以包括第三非门和第四非门,第三非门的输入端连接或非门的输出端,第三非门的输出端连接第四非门的输入端,第四非门的输出端连接模式选择器。

23、在上述设计中,串联的第三非门和第四非门能用于过滤所经过的信号中的不规则的毛刺等杂质信号,以通过消颤而得到纯净的信号,有助于提高信号的准确度。

24、第二方面,本技术提供一种熔丝更新方法,该方法适用于如上述第一方面所述的熔丝更新电路,该方法包括:首先,通过控制第二控制信号呈现为有效电平,控制测试锁存电路输出第一信号,然后,通过控制第三控制信号呈现为无效电平,控制模式切换电路根据第一信号加载测试模式的配置信息。

25、一种可能的设计中,该方法还可以包括:首先,通过控制第二控制信号呈现为无效电平以及控制第一控制信号呈现为有效电平,控制测试锁存电路输出第二信号,然后,通过控制第三控制信号呈现为无效电平,控制模式切换电路根据第二信号加载熔丝信息。

26、一种可能的设计中,该方法还可以包括:通过控制第二控制信号和第一控制信号均呈现为无效电平,控制测试锁存电路输出第一信号。

27、一种可能的设计中,该方法还可以包括:通过控制第三控制信号呈现为有效电平,控制模式切换电路加载熔丝信息。

28、第三方面,本技术提供一种存储器,该存储器包括控制器和如上述第一方面中任一项所述的熔丝更新电路,其中,控制器连接熔丝更新电路中的熔丝锁存电路的第一输入端和第二输入端,以及连接熔丝更新电路中的模式切换电路的第二输入端,用于通过执行如上述第二方面中任一项所述的熔丝更新方法,控制熔丝更新电路加载熔丝信息或测试模式的锁存信息。

29、第四方面,本技术提供一种电子设备,包括印刷电路板(printed circuit board,pcb)和上述第四方面中任一项设计所述的存储器,其中存储器设置在pcb的表面。

30、具体地,该电子设备包括但不限于:智能手机、智能手表、平板电脑、虚拟现实(virtual reality,vr)设备、增强现实(augmented reality,ar)设备、车载设备、台式计算机、个人计算机、手持式计算机或个人数字助理。

31、第五方面,本技术提供一种计算机可读存储介质,该计算机可读存储介质存储有计算机程序,当计算机程序被运行时,实现如上述第二方面中任一项所述的方法。

32、第六方面,本技术提供一种计算机程序产品,当该计算机程序产品在处理器上运行时,实现如上述第二方面中任一项所述的方法。

33、上述第二方面至第六方面的有益效果,具体请参照上述第一方面中相应设计可以达到的技术效果,这里不再重复赘述。

本文地址:https://www.jishuxx.com/zhuanli/20240914/296029.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表