晶体管、电力电子开关器件和用于制造晶体管的方法与流程

- 国知局

- 2024-10-09 15:06:19

本公开涉及一种晶体管、特别是宽带隙功率晶体管,其包括外延层、至少一个阱区域、以及至少一个端子区域、特别是源极区域。本公开进一步涉及一种包括多个开关单元的电力电子开关器件和一种用于制造晶体管、特别是sic功率晶体管的方法。

背景技术:

1、在许多应用(包括电力电子学)中使用晶体管。通常期望晶体管(诸如,金属氧化物半导体场效应晶体管(mosfet))能够在指定的时间内承受住所谓的短路状况。例如,可能期望提供短路耐受时间(scwt)至少为10μs的功率晶体管。控制电路可使用scwt来识别对应的电力电路中的故障并使其断电。

2、同时,期望最小化晶体管且特别是功率晶体管的传导损耗。低传导损耗通常导致半导体材料中的饱和电流密度更高,进而缩短其scwt。

3、因此,描述改进的器件及其制造方法是一项挑战,这些器件和方法允许将低传导损耗的目标与预定的scwt的目标相平衡。

技术实现思路

1、本公开的实施例涉及一种晶体管、一种电力电子开关器件、以及一种用于制造晶体管的方法,以上各者允许选择性地增加端子区域中的一个内部的电阻率以控制晶体管结构内的电压降并因此控制晶体管的对应scwt。这至少部分地通过引入包括两性杂质(amphoteric impurities)的至少一个电阻区域来实现。

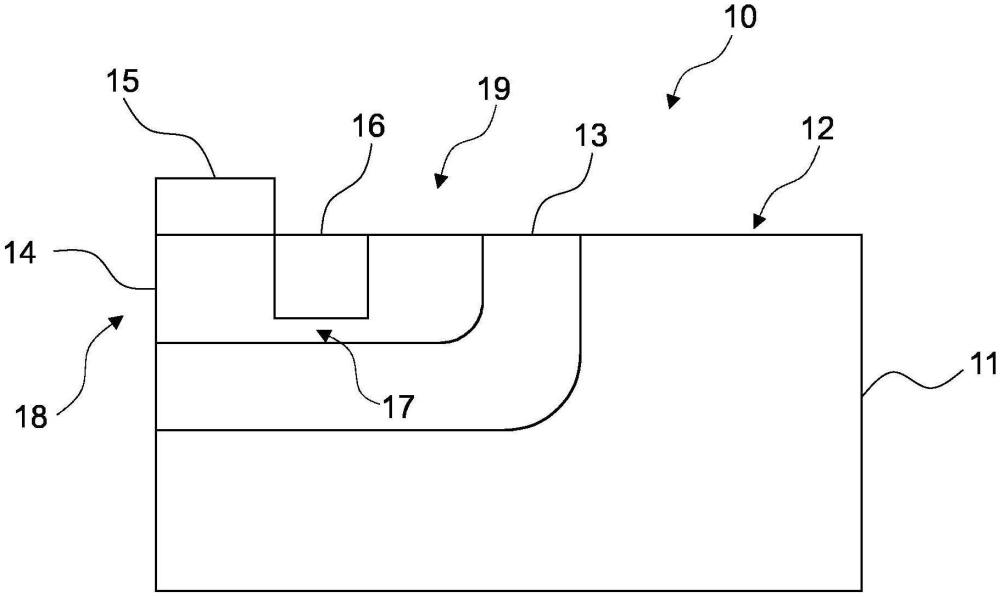

2、根据第一方面,公开了一种晶体管、特别是宽带隙半导体功率晶体管。该晶体管包括:第一导电类型的外延层;第二导电类型的至少一个阱区域,其形成在外延层的选定区域中;第一导电类型的至少一个端子区域、特别是源极区域,其形成在所述至少一个阱区域中或形成为与其毗邻;至少一个端子电极、特别是源电极,其至少部分地形成在所述至少一个端子区域的第一部分的表面上;以及形成在所述至少一个端子区域内的至少一个电阻区域,所述至少一个电阻区域包括两性杂质。

3、通过引入形成在至少一个端子区域内的至少一个电阻区域,可以增加端子区域的电阻,并且晶体管结构的其他部分可以通过降低其中的电压降而得到保护。两性杂质的使用允许严密控制电阻区域的电阻率并因此控制端子区域的总电阻。除了别的以外,本发明人已发现,可以控制注入有两性物质的端子区域的电阻率,例如基于注入剂量或电阻区域的激活温度。

4、另外,本发明人已发现,两性掺杂剂的使用并不导致或仅导致一般地在外延层中且特别地在形成于至少一个端子区域内的所述至少一个电阻区域中微量的晶体缺陷。例如,在将锰(mn)注入到用作宽带隙半导体材料的碳化硅(sic)中时,z1/2晶格缺陷的浓度可处于或低于1e11 cm-3。对于其他两性物质和/或注入剂量,z1/2晶格缺陷的浓度仍处于相对低的水平,诸如处于或低于1e13 cm-3。这可以归因于c间隙的形成,即在注入期间,c原子被撞出了其在晶格中的格位(site)。此类间隙甚至在室温下也可以扩散,并且可以湮没z1/2,从而对应于晶格中的空位c格位。相比之下,注入其他类型的掺杂剂可能导致晶格缺陷的浓度增加。例如,注入质子、氦(he)或氩(ar)可能导致z1/2晶格缺陷处于或高于1e15 cm-3的相对高的浓度,例如,比使用两性掺杂剂实现的z1/2晶格缺陷的浓度高了一个或多个数量级。

5、所述至少一个电阻区域可包括作为两性掺杂剂的锰(mn)和钒(v)中的至少一种。这些掺杂剂可选择性地操作为对电力电子学有用的常见宽带隙半导体材料中的电荷受主或施主,特别是在诸如4h-sic或6h-sic之类的碳化硅(sic)中。

6、使用常见的半导体加工步骤和参数,可以将端子区域的电阻率调节为超过10ωcm,例如在20ωcm与20kωcm之间的范围内的某个值,该范围是用于控制功率晶体管的scwt的有用范围。

7、可通过使用各种注入技术来获得端子区域内的不同结构。例如,有可能通过其中存在两性杂质的一个或多个第一子区域来完全分离端子区域的基本不包括两性杂质的第二子区域。通过对所述至少一个端子区域图案化,可以严密控制端子区域的不同部分中的电流密度。

8、所描述的端子结构适用于许多不同的晶体管类型,包括金属氧化物半导体场效应晶体管(mosfet)、金属绝缘体半导体场效应晶体管(misfet)、结型场效应晶体管(jfet)和绝缘栅双极晶体管(igbt)。此外,可以以不同的配置(包括平面配置和沟槽配置)使用所描述的端子结构。

9、根据第二方面,公开了一种电力电子开关器件。该器件包括并联电连接的多个开关单元,其中,所述多个开关单元中的每个开关单元包括根据第一方面的晶体管。通过使用以上的并联晶体管中的几个,可以获得相对高的额定电流,如电力电子学中常常需要的。

10、结合单独的晶体管所描述的特征和优点也可在更复杂的器件中使用,诸如包括布置在公共衬底上和/或并联电连接的多个晶体管单元的电力电子开关器件。

11、根据以上方面的晶体管或电力电子开关器件可具有600伏或以上的额定电压。

12、根据第三方面,提供了一种用于制造晶体管、特别是宽带隙半导体功率晶体管的方法。该方法包括以下步骤:

13、-外延生长第一导电类型的半导体层;

14、-形成第二导电类型的至少一个阱区域,所述至少一个阱区域形成在外延层的选定区域中;

15、-将第一导电类型的至少一个端子区域、特别是源极区域形成在所述至少一个阱区域中或形成为与其毗邻;以及

16、-将两性掺杂剂注入于所述至少一个端子区域的至少一部分中。

17、以上步骤允许使用用于制造电力电气器件的完善的加工步骤来制造根据第一方面的晶体管。

18、例如,可使用在50kev至1000kev的范围内的适当注入能量来控制两性掺杂剂的注入深度并因此控制控制电阻区域的形状。

19、此外,通过使用在1010cm-2至1014cm-2的范围内的注入剂量来注入两性掺杂剂,可以控制电阻区域的总电阻率。

20、在至少一个实施例中,该方法进一步包括:在第一温度t1下对包括注入的两性掺杂剂的至少一个电阻区域进行退火,其中,第一温度t1是基于端子区域的目标电阻率ρ来选择的。根据本发明人的实验,激活温度与掺杂并激活的电阻区域的电阻率之间存在某种关系,可以利用这种关系来限制在短路状况期间通过晶体管的峰值电流。特别地,如果源极区域掺杂有两性掺杂剂,则可以降低邻近沟道区域中的电流密度,该电流密度由功率晶体管中的栅极-源极电位(vgs)定义。

21、本公开包括一种半导体器件、特别是晶体管的端子结构、以及一种用于制造此类晶体管和端子的方法的几个方面。关于这些方面中的一个所描述的每个特征也在本文中关于其他方面进行了公开,即使相应特征没有在特定方面的上下文中明确提及。

技术特征:1.一种晶体管(10),特别是宽带隙半导体功率晶体管(40),包括:

2.根据权利要求1所述的晶体管(10),其中,所述至少一个电阻区域(16)包括作为两性掺杂剂的锰mn和钒v中的至少一种。

3.根据权利要求1或2所述的晶体管(10),其中,所述至少一个电阻区域(16)中的两性掺杂剂的浓度位于1014至1018cm-3的范围内。

4.根据权利要求1至3中任一项所述的晶体管(10),其中,

5.根据权利要求1至4中任一项所述的晶体管(10),其中,所述晶体管的短路耐受时间scwt超过3μs,并且优选地为10μs或超过10μs。

6.根据权利要求1至5中任一项所述的晶体管(10),其中,

7.根据权利要求1至6中任一项所述的晶体管(10),其中,所述至少一个端子区域(14)包括至少三个子区域,该至少三个子区域包括:包括两性杂质的至少一个第一子区域(45)、以及基本不含两性杂质的至少一个第二子区域(18、19、46),该至少三个子区域特别地包括以下各者中的一者:

8.根据权利要求1至7中任一项所述的晶体管(10),其中,所述晶体管(10)是呈平面配置或沟槽配置的以下各者中的一者:金属氧化物半导体场效应晶体管mosfet、金属绝缘体半导体场效应晶体管misfet、结型场效应晶体管jfet和绝缘栅双极晶体管igbt。

9.根据权利要求1至8中任一项所述的晶体管(10),进一步包括以下各者中的至少一者:

10.一种电力电子开关器件,包括布置在公共衬底上和/或并联电连接的多个晶体管单元,每个晶体管单元包括根据权利要求1至9中任一项所述的晶体管(10)。

11.一种用于制造晶体管(10),特别是宽带隙半导体功率晶体管(40)的方法,所述方法包括:

12.根据权利要求11所述的方法,其中,使用在50kev至1000kev的范围内的注入能量来注入所述两性掺杂剂。

13.根据权利要求11或12所述的方法,其中,使用在1010cm-2至1014cm-2的范围内的注入剂量来注入所述两性掺杂剂。

14.根据权利要求11至13中任一项所述的方法,进一步包括:

15.根据权利要求14所述的方法,进一步包括:

技术总结本发明涉及一种晶体管(10)、特别是宽带隙半导体功率晶体管(40),包括:第一导电类型的外延层(11);第二导电类型的至少一个阱区域(13),其形成在外延层(11)的选定区域中;第一导电类型的至少一个端子区域,特别是源极区域(29),其形成在至少一个阱区域(13)中或形成为与其毗邻;至少一个端子电极(15),特别是源电极(21),其至少部分地形成在至少一个端子区域(14)的第一部分的表面(12)上;和形成在至少一个端子区域(14)内的至少一个电阻区域(16),至少一个电阻区域(16)包括两性杂质。本公开进一步涉及一种包括多个开关单元的电力电子开关器件和一种用于制造晶体管(10)、特别是宽带隙半导体功率晶体管(40)的方法。技术研发人员:G·阿尔菲里,G·罗马诺,A·米哈埃拉受保护的技术使用者:日立能源有限公司技术研发日:技术公布日:2024/9/29本文地址:https://www.jishuxx.com/zhuanli/20241009/307641.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表