一种应用于图像传感器的三分之一行读出架构的制作方法

- 国知局

- 2024-12-06 12:29:34

本发明涉及图像传感器,尤其涉及一种应用于图像传感器的三分之一行读出架构。

背景技术:

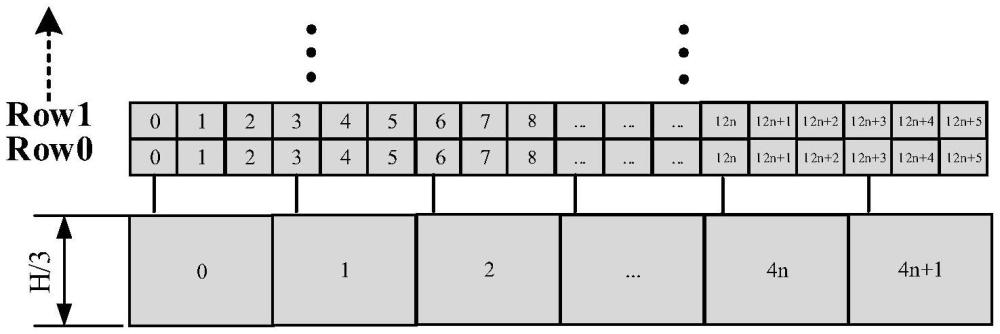

1、目前cmos图像传感器广泛应用于电子消费、安防监控、自动控制、医疗以及国防等众多领域,在图像传感器中,业界流行的读出方式有一整行同时读出或半行同时读出,如图1所示为现有技术一整行读出方式的架构示意图,整行读出是一次将改行的所有pixel同时读出,那么对应的列电路就需要对应的pixel数量,比如pixel有12n+5个,那么对应就需要12n+5个列电路,且对应的列电路宽度就是pixel的宽度,故整行同时读出功耗最大,面积最大,但是对电路的速度要求低。

2、如图2所示为现有技术半行读出方式的架构示意图,半行读出是先读出0,2,4,6…12n,12n+2,12n+4等偶数列,然后再下一次读出1,3,5,7,…12n+5等奇数列,这样列电路的宽度可以是两倍pixel的宽度,因此高度就会是整行读出的一半,且列数量变为原来的一半,功耗和面积都减半,速度需要增加一倍。

3、由此可见,现有技术的读出架构均存在一定缺陷,如何减小电路功耗和面积是急需解决的问题。

技术实现思路

1、本发明的目的是提供一种应用于图像传感器的三分之一行读出架构,该三分之一行读出架构相对整行读出来说,列电路功耗减小了2/3,面积减小了2/3,有效减小了电路功耗和面积。

2、本发明的目的是通过以下技术方案实现的:

3、一种应用于图像传感器的三分之一行读出架构,在图像传感器中,所述三分之一行读出架构先读出0,3,6,…12n,12n+3列,再读出1,4,7…12n+1,12n+4列,最后读出2,5,8…12n+2,12n+5列,其中n表示像素阵列一行像素所拥有的列数量;

4、且用于读出每行的列电路为整行读出时电路的三分之一。

5、所述三分之一行读出架构将一行分3次读出,列电路的宽度是三倍像素pixel的宽度,高度为整行读出的1/3;列电路的数量为整行读出的1/3,那么列电路的功耗和面积都为整行读出的1/3。

6、由上述本发明提供的技术方案可以看出,上述三分之一行读出架构相对整行读出来说,列电路功耗减小了2/3,面积减小了2/3,有效减小了电路功耗和面积。

技术特征:1.一种应用于图像传感器的三分之一行读出架构,其特征在于,在图像传感器中,所述三分之一行读出架构先读出0,3,6,…12n,12n+3列,再读出1,4,7…12n+1,12n+4列,最后读出2,5,8…12n+2,12n+5列,其中n表示像素阵列一行像素所拥有的列数量;

2.根据权利要求1所述应用于图像传感器的三分之一行读出架构,其特征在于,

技术总结本发明公开了一种应用于图像传感器的三分之一行读出架构,在图像传感器中,所述三分之一行读出架构先读出0,3,6,…12n,12n+3列,再读出1,4,7…12n+1,12n+4列,最后读出2,5,8…12n+2,12n+5列。该三分之一行读出架构相对整行读出来说,列电路功耗减小了2/3,面积减小了2/3,有效减小了电路功耗和面积。技术研发人员:李文杰,旷章曲受保护的技术使用者:豪威科技(北京)股份有限公司技术研发日:技术公布日:2024/12/2本文地址:https://www.jishuxx.com/zhuanli/20241204/341702.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表