1.本发明涉及电力电子技术领域,尤其涉及一种多芯片并联大功率碳化硅模块。

背景技术:

2.功率半导体模块是将多个半导体芯片按照一定功能、模式组合再灌封成一体的器件,其主要应用于电力电子系统功率回路,是实现电能转换的核心硬件。

3.多芯片并联封装的功率模块面临着很多挑战,包括如何保证各并联芯片的均流特性,如何减小功率模块的寄生电感,如何降低门极回路和功率回路的耦合问题。sic mosfet相比于si igbt具有更高的开关速度,对寄生参数更敏感。

4.现有封装结构中sic mosfet的布局中,芯片间的热耦合现象严重,同时不对称的布局会使并联芯片的均流特性难以保证,且信号回路与功率回路耦合对门极驱动有不利影响,芯片的可靠性和器件的寿命都将降低。

技术实现要素:

5.为了降低了芯片串扰电压,在实现低杂感和高功率密度的同时实现良好的均流特性,本技术提供一种多芯片并联大功率碳化硅模块。

6.本技术提供的多芯片并联大功率碳化硅模块,采用如下的技术方案:多芯片并联大功率碳化硅模块包括:基板、在基板上布局的电路铜层以及设置于所述电路铜层上的半导体功率电子元件;所述半导体功率电子元件包括上桥功率芯片组、下桥功率芯片组、电极探针及若干控制极电阻;所述上桥功率芯片组包括六个并联设置的半导体功率芯片,所述下桥功率芯片组包括六个并联设置的半导体功率芯片。

7.在一些实施方式中,所述电路铜层包括用于连接上桥功率芯片组的上桥半导体功率芯片导电区、用于连接下桥功率芯片组的下桥半导体功率芯片导电区、用于连接电极探针的电极探针导电区、用于连接控制极电阻的控制极电阻导电区,以及输入电极区和输出电极区,所述上桥半导体功率芯片导电区、下桥半导体功率芯片导电区、电极探针导电区、控制极电阻导电区、输入电极区和输出电极区相互之间独立设置。

8.在一些实施方式中,所述上桥功率芯片组上的六个并联设置的半导体功率芯片在上桥半导体功率芯片导电区上一字排开设置;所述下桥功率芯片组上的六个并联设置的半导体功率芯片在下桥半导体功率芯片导电区上一字排开设置,所述上桥功率芯片组与所述下桥功率芯片组相互平行。

9.在一些实施方式中,包括两个所述控制极电阻导电区,两个所述控制极电阻导电区分别位于所述上桥半导体功率芯片导电区和所述下桥半导体功率芯片导电区一侧。

10.在一些实施方式中,两个所述控制极电阻导电区上分别连接六个控制极电阻,所述控制极电阻与所述半导体功率芯片一一对应设置。

11.在一些实施方式中,两个所述控制极电阻导电区上的控制极电阻成一字排开。

12.在一些实施方式中,所述电极探针包括第一电极探针组及第二电极探针组,所述第一电极探针组包括一个第一电极探针和一个第二电极探针,所述第二电极探针组包括一个第三电极探针和一个第四电极探针。

13.在一些实施方式中,所述电极探针导电区包括用于连接所述第一电极探针的第一电极探针导电区、用于连接所述第二电极探针的第二电极探针导电区、用于连接所述第三电极探针的第三电极探针导电区,及用于连接所述第四电极探针的第四电极探针导电区,所述第一电极探针导电区、第二电极探针导电区、第三电极探针导电区及第四电极探针导电区相互独立设置。

14.综上,本发明提供的多芯片并联大功率碳化硅模块,与现有技术相比,具有以下优点:上桥功率芯片组通过六个半导体功率芯片并联设置,下桥功率芯片组通过六个半导体功率芯片并联设置,该布局方式有利于保证各并联芯片换流路径杂散电感参数分布保持一致,以实现良好的均流特性。且该布局方式减小了相邻芯片的热耦合影响,有利于提高功率半导体模块的最大输出功率,减小芯片的最大结温。

15.在增加芯片数量的同时减小dbc的尺寸,不仅减小了换流回路的路径减小了寄生电感的大小而且大大提高了整个功率模块的功率密度。门极回路分布均匀可以提高并联芯片间动态性能的一致性,通过减小共源极电感来减小信号回路与功率回路的耦合影响,降低了芯片串扰电压。

16.本技术实现了低杂感设计,提升了各并联芯片的均流性能,降低了信号回路与功率回路的耦合,降低了芯片串扰电压,提升模块的功率密度。

附图说明

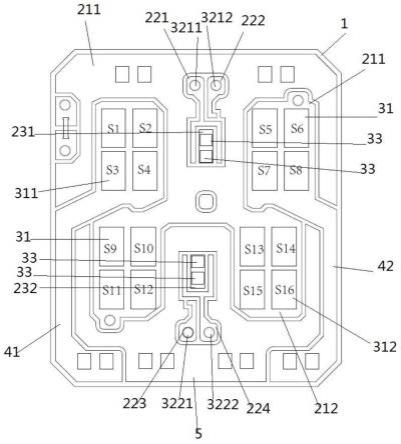

17.图1为本技术提供的一种多芯片并联大功率碳化硅模块的结构图。

18.图中:1、基板;211、上桥半导体功率芯片导电区;212、下桥半导体功率芯片导电区;221、第一电极探针导电区;222、第二电极探针导电区;223、第三电极探针导电区;224、第四电极探针导电区;231、第一控制极电阻导电区;232、第二控制极电阻导电区;31、半导体功率芯片;311、上桥功率芯片组;312、下桥功率芯片组;32、电极探针;321、第一电极探针组;322、第二电极探针组;33、控制极电阻;3211、第一电极探针;3212、第二电极探针;3221、第三电极探针;3222、第四电极探针;4、输入电极区;41、第一输入电极区;42、第二输入电极区;5、输出电极区。

具体实施方式

19.以下结合附图对本发明作进一步详细说明。

20.本技术实施例公开了一种多芯片并联大功率碳化硅模块,如图1所示,包括基板1、在基板1上布局的电路铜层以及设置于电路铜层上的半导体功率电子元件。

21.半导体功率电子元件包括半导体功率芯片31,半导体功率芯片31为两组,分别为

上桥功率芯片组311及下桥功率芯片组312,上桥功率芯片组311和下桥功率芯片组312分别包括六个并联的半导体功率芯片31,上桥功率芯片组311上的六个并联设置的半导体功率芯片31在上桥半导体功率芯片导电区211上一字排开设置;下桥功率芯片组312上的六个并联设置的半导体功率芯片31在下桥半导体功率芯片导电区212上一字排开设置,上桥功率芯片组311与下桥功率芯片组312相互平行。

22.半导体功率芯片31为mos管,半导体功率芯片31包括第一主电极、第二主电极及控制电极,第一主电极为mos管的漏极d,第二主电极为mos管的源极s,控制极为mos管的栅极g,其中第一主电极为位于半导体功率芯片31电源输入方向的主电极,第二主电极为位于半导体功率芯片31电源输出方向的主电极,即第一主电极和第二主电极接驱动电源,控制电极作为输入控制极,用于输入控制信号,控制第一主电极和第二主电极之间的通断。

23.半导体功率电子元件还包括电极探针32及若干控制极电阻33,电极探针32及控制极电阻33也设置为两组,分别连接至上桥功率芯片组311及下桥功率芯片组312。

24.电极探针32用于传输电极电压,电极探针32包括第一电极探针组321及第二电极探针组322,第一电极探针组321包括一个第一电极探针3211和一个第二电极探针3212,第二电极探针组322包括一个第三电极探针3221和一个第四电极探针3222。电极探针导电区包括用于连接第一电极探针3211的第一电极探针导电区221、用于连接第二电极探针3212的第二电极探针导电区222、用于连接第三电极探针3221的第三电极探针导电区223,及用于连接第四电极探针3222的第四电极探针导电区224,第一电极探针导电区221、第二电极探针导电区222、第三电极探针导电区223及第四电极探针导电区224相互独立设置。第一电极探针3211和第三电极探针3221与半导体功率芯片31的第二主电极连接,用于传输第二主电极的电压,第二电极探针3212和第四电极探针3222与半导体功率芯片31的控制电极连接,用于传输控制电极的电压,电极探针32将测量得到的电压传输至驱动控制电路,以便驱动控制电路根据测得的电极电压控制半导体功率回路。

25.包括两个控制极电阻导电区,两个控制极电阻导电区分别位于上桥半导体功率芯片导电区211和下桥半导体功率芯片导电区212一侧,两个控制极电阻导电区上分别连接六个成一字排开的控制极电阻33,控制极电阻33与半导体功率芯片31一一对应设置。控制极电阻33能够有效降低半导体功率回路中发生电压过冲的概率,并且用于对半导体功率回路进行分流,防止半导体功率芯片31的电流超出要求,导致半导体功率芯片31过热损坏,控制极电阻33即为栅极电阻或门极电阻。

26.本技术上桥功率芯片组通过六个半导体功率芯片并联设置,下桥功率芯片组通过六个半导体功率芯片并联设置,有利于保证各并联芯片换流路径杂散电感参数分布保持一致,以实现良好的均流特性。且该布局方式减小了相邻芯片的热耦合影响,有利于提高功率半导体模块的最大输出功率,减小芯片的最大结温。在增加芯片数量的同时减小dbc的尺寸,不仅减小了换流回路的路径减小了寄生电感的大小而且大大提高了整个功率模块的功率密度。门极回路分布均匀可以提高并联芯片间动态性能的一致性,通过减小共源极电感来减小信号回路与功率回路的耦合影响,降低了芯片串扰电压。

27.本具体实施方式的实施例均为本发明的较佳实施例,并非依此限制本发明的保护范围,故:凡依本发明的结构、形状、原理所做的等效变化,均应涵盖于本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。