基于先进封装工艺的CPO光模块组件及其制备方法与流程

- 国知局

- 2024-06-21 12:10:10

本技术涉及光、电混合集成/封装,具体而言,涉及一种基于先进封装工艺的cpo光模块组件及其制备方法。

背景技术:

1、光模块主要应用于数据通信领域,其功能是实现光电信号的相互转化。随着用于数据中心及ai应用相关的asic芯片容量的增加,高速光模块的传输速率由从100g gbps已发展至800gbps。对于单个光模块来说,模块速率的提升也意味着内部光电芯片数量的提升。如何在满足现有光模块外壳及速率标准的条件下,实现多芯片、多收发通道的互连,降低光模块的功耗、信号损失,将是未来光模块面临的重要技术挑战。

2、目前常用的400g dr4、800g dr8光模块产品主要满足qsfp与osfp相关的模块封装标准,其内部可靠贴片区域的宽度在16~18mm。目前国内量产的发射模组芯片(激光器芯片、调制器芯片、driver芯片)及接收模组芯片(探测器、tia)普遍最高速率在400gbps左右。因此随着交换机容量的提升,速率800gbps以上的非相干光模块内部光电芯片数量以及单芯片尺寸的增长是不可避免的问题。同时光模块内部的光电芯片互连依然以cob工艺为主,cob工艺为主的引线键合的互连方式往往占据较大的板上空间,数量激增的引线数量也会造成延时和功率损耗的积累,最后造成功耗的消耗以及模块传输距离的减少。

3、然而,经过发明人研究发现现有高速光模块的损耗和延迟来源一部分是由于集成度提高累计的引线数量造成的;基于cob的贴片方式导致光模块内部的光电芯片都粘贴在同一平面,严重压缩模块内部的贴片空间;除此之外,cob基于wire bonding的pad连接方式,导致光电芯片表面的散热面积有限,同时需要在耦合过程中对引线进行保护。

技术实现思路

1、本技术实施例的目的在于提供基于先进封装工艺的cpo光模块组件及其制备方法,用以解决在光模块内部光电芯片数量以及单芯片尺寸的增长时传统的引线键合方式光电芯片表面的散热面积有限,进而导致功耗的消耗以及模块传输距离的减少的技术问题。

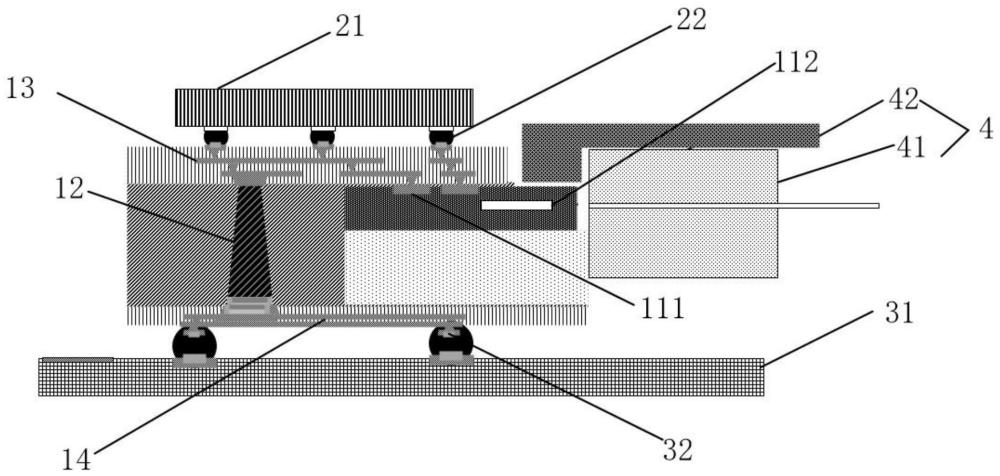

2、第一方面,根据本发明实施例提供一种基于先进封装工艺的cpo光模块组件,包括:

3、重构光芯片,包括光芯片晶圆体、导电单元、第一rdl+ubm单元及第二rdl+ubm单元,其中:

4、所述光芯片晶圆体中包括电性引出单元及硅波导单元;光芯片晶圆体中硅波导单元靠近的一个侧壁外设有出光口;

5、导电单元,位于所述重构光芯片的背离所述光出口的一侧;

6、第一rdl+ubm单元位于光芯片晶圆体正面,第二rdl+ubm单元位于光芯片晶圆体的背面,第一rdl+ubm单元与第二rdl+ubm单元均与导电单元连接,第一rdl+ubm单元还与所述电性引出单元连接,用于电性引出;

7、所述cpo光模块组件,还包括:

8、重构电芯片,包括电芯片及与第一电性连接引脚,所述第一电性连接引脚与所述第一rdl+ubm单元电性连接;

9、pcb板,包括基板及在基板上设的第二电性连接引脚,所述第二电性连接引脚与所述第二rdl+ubm单元电性连接;

10、光纤阵列fa组件,通过所述出光口与硅波导单元耦合。

11、优选地,所述导电单元包括金属种子单元及位于金属种子单元之上的柱状金属;

12、所述金属种子单元的材质包括ti和cr中的至少一种。

13、优选地,所述光纤阵列fa组件包括光纤阵列fa及fa盖板,所述fa盖板位于光纤阵列fa的背离pbc基板的表面之上,用于对光纤阵列fa进行保护。

14、优选地,所述的基于先进封装工艺的cpo光模块组件,还包括:

15、散热单元,位于重构电芯片的背离第一rdl+ubm单元的表面的上方,用于对cpo光模块组件产生的热量进行疏导。

16、优选地,所述的基于先进封装工艺的cpo光模块组件,还包括:

17、壳体,包括上壳体单元和下壳体单元,下壳体单元连接于pcb板的基板的背离所述重构光芯片的表面;

18、上壳体单元连接于散热单元的背离重构电芯片的表面;

19、夹持件,连接于上壳体单元与fa盖板之间,用于对光纤阵列fa组件进行固定。

20、第二方面,根据本发明实施例提供一种基于先进封装工艺的cpo光模块组件的制备方法,包括:

21、提供重构光芯片及重构电芯片,所述重构光芯片包括光芯片晶圆体、导电单元、第一rdl+ubm单元、第二rdl+ubm单元及电性引出单元;

22、将所述重构电芯片与重构光芯片进行集成,其中,重构电芯片的第一电性连接引脚与第一rdl+ubm单元连接;

23、提供一包括基板和第二电性连接引脚的pcb板,将pcb板与包括重构电芯片和重构光芯片的集成体进行集成,使第二电性连接引脚与第二rdl+ubm单元电性连接;

24、将光纤阵列fa组件于出光口与硅波导单元耦合连接。

25、优选地,所述的制备方法,还包括:制备重构光芯片;所述制备重构光芯片,包括:

26、提供一包括衬底层、介质层及于所述介质层中制备有若干硅波导单元及电性引出单元的光芯片晶圆;

27、针对所述光芯片晶圆,经过端面刻蚀、涂覆pi材料层、固化及切割划片工艺,得到光芯片晶圆体;

28、提供临时玻璃衬底,并在所述临时玻璃衬底上涂覆光致释放层及光刻胶,并在经过显影后制备导电单元及去除多余的光刻胶后,形成基底单元;

29、将所述光芯片晶圆体集成于所述基底单元的相邻两个导电单元之间,其中,光芯片晶圆体的衬底层与所述基底单元的光致释放层连接;

30、针对光芯片晶圆体与基底单元形成的集成结构,经过塑封料注塑、芯片减薄工艺及rdl+ubm制造工艺于光芯片晶圆体的正面制备与导电单元、电性引出单元连接的第一rdl+ubm单元,在相邻两个第一rdl+ubm单元之间制备pic光口,并在光芯片晶圆体的背面制备与导电单元连接的第二rdl+ubm单元;

31、去除pic光口处的保护胶,并刻蚀相邻两个硅波导之间的pi层直至衬底层形成出光口;

32、沿端面刻蚀形成的凹槽中间切割划片,形成多个重构光芯片;

33、优选地,所述的制备方法,包括:

34、在经过显影后的目标区域制备溅射种子层;所述溅射种子层的材质包括ti和cr中的至少一种;

35、于所述种子层之上及周边电镀导电金属,电镀的导电金属的高度于显影前涂覆的光刻胶的高度齐平;所述导电金属为金属铜。

36、优选地,所述的制备方法,还包括:

37、制备第一介质层,以埋覆及保护第一rdl+ubm单元;和/或

38、制备第二介质层,以埋覆及保护第二rdl+ubm单元。

39、优选地,所述的制备方法,还包括:

40、于重构电芯片的背离第一rdl+ubm单元的表面的上方集成散热单元,用于对cpo光模块组件产生的热量进行疏导;以及

41、提供一包括壳体及夹持件的外壳,所述壳体包括上壳体单元和下壳体单元;

42、将所述下壳体单元连接于pcb板的基板的背离所述重构光芯片的表面;

43、将所述上壳体连接于散热单元的背离重构电芯片的表面;

44、将所述夹持件连接于上壳体与fa盖板之间,用于对光纤阵列fa组件进行固定;

45、其中,光纤阵列fa组件包括光纤阵列fa和fa盖板,所述fa盖板位于光纤阵列fa组件之上。

46、本发明实施例提供的基于先进封装工艺的cpo光模块组件,基于扇出、倒装的方法对光电芯片进行重构,并将重构光电芯片、外部光组件、外壳等部件组装,完成一种基于先进封装技术的cpo光模块组件,重构电芯片的上表面无器件覆盖或连接,因而有效确保了较大的散热面积,避免了现有技术方案中散热面积有限导致功耗的消耗及光模块传输距离的减少的问题,同时,本方案中在耦合过程中不涉及复杂的引线,引线也是造成功耗损耗以及带宽下降的原因,因此,本方案提高了封装可靠性和效率,改善了由于引线键合方式的额外阻抗。减少了eic、pic插损,增大了两者间的传输带宽。

本文地址:https://www.jishuxx.com/zhuanli/20240618/25844.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表