一种控制电路的制作方法

- 国知局

- 2024-06-21 14:01:52

本发明涉及集成电路cmos工艺芯片中lvds接口电路的设计领域,特别涉及一种应用于micro-oled显示驱动芯片中lvds高速接口信号电平转换及增益控制电路。

背景技术:

1、在目前通用的cmos制造平台上,一般地一种工艺会提供两种电源电压的mos管器件即使用于io或模拟电路中和内部数字逻辑控制单元的mos器件。但mos器件只能承受其电气特性内的极限电源电压,如果要提供更高的电源电压、或传输更高电压信号时就会受到永久性的损坏。因此,产品应用会收到很大的限制,或者需要增加更高的制造成本。

2、随着科技发展,芯片面积越来越大,同时功耗也随之增大;为了在同样尺寸的晶圆上得到更多的颗粒数,集成电路cmos工艺尺寸越来越小,采用更低电源域的mos管器件来达到降低功耗目的,例如在micro-oled 55nm制程里有1.2v低压器件,同时中高压器件有5v、8v乃至更高(满足oled驱动的需求)。在micro-oled微型显示器实现功能时,其驱动电路会接收到lvds信号并基于此信号进行驱动控制,一般由lvds发送端发送过来lvds信号被接收,然后进行驱动处理;如专利申请号为201811115528.8的一种micro-oled微型显示器驱动电路,包括信号源模块、与所述信号源模块电性连接的fpga((field programmable gatearray,现场可编程门阵列)模块、micro-oled模块以及用于分别给fpga模块和micro-oled模块提供所需电压的电源模块;所述信号源模块提供图像视频信号给fpga模块,该fpga模块对图像视频信号进行解码编码处理,然后传输数据信息到micro-oled模块部位进行视频显示;所述信号源模块包括mipi信号、hdmi信号、lvds信号或edp信号。

3、在lvds发送端,一般其电源电压的最高电平在1.8v或2.5v,输出差分信号最高电压幅值达到1.5v或更高,要求接收端的器件能兼容这个输出最高电压幅值的需求。由于在micro-oled 55nm或更小尺寸的工艺里,没有1.8v或2.5v器件,如果用5v、8v的中高压器件来设计接收电路,其传输速率将严重下降;如果用1.2v低压器件来设计接收电路,其对lvds发送端发送信号的最高电压有所限制,或接收高于低压mos极限电源电压会造成低压mos器件永久性损坏。基于此需要对lvds接收电路中增加有差分信号电平的转换电路,现有技术的接收电路并没有设计有信号电平转换电路。

4、在micro-oled显示领域,高分辨率高刷新率作为发展趋势,意味着数据传输量越来越大、传输速率越来越高,决定了在micro-oled显示驱动芯片的lvds接收器电路里,对输入的差分信号进行电平转换、以及增益的控制处理尤为重要。

技术实现思路

1、本发明的目的在于克服现有技术的不足,提供一种控制电路,用于实现对接收到的lvds差分信号电平进行转换控制以满足电平兼容的目的。

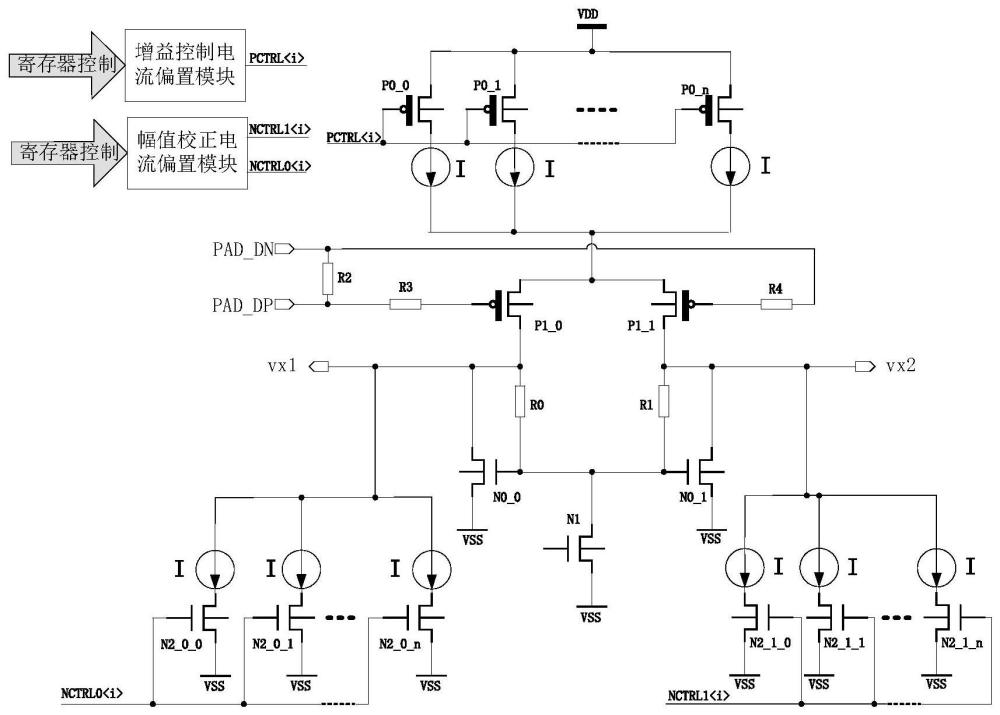

2、为了实现上述目的,本发明采用的技术方案为:一种控制电路,包括:pmos管p1_0、p1_1、增益控制电路和nmos管n0_0、n0_1;接收的lvds差分信号分别送入到端子pad_dn和端子pad_dp;端子pad_dn经电阻r4连接至pmos管p1_1的栅极;端子pad_dp经电阻r3连接至pmos管p1_0的栅极;端子pad_dn和端子pad_dp通过电阻r2连接;pmos管p1_0的源极和pmos管p1_1的源极连接在一起后接入到增益控制电路的输出端;

3、nmos管n0_0的栅极和nmos管n0_1的栅极连接在一起后分别经电阻r0连接至pmos管p1_0的漏极、经电阻r2连接至pmos管p1_1的漏极;

4、pmos管p1_0的漏极引出端子vx1、pmos管p1_1的漏极引出端子vx2,端子vx1、端子vx2输出转换控制后的lvds电平信号;

5、端子vx1连接至nmos管n0_0的源极,nmos管n0_0的漏极接vss;端子vx2连接至nmos管n0_1的源极,nmos管n0_1的漏极接vss。

6、所述控制电路还包括nmos管n1,nmos管n1的源极连接至nmos管n0_0或n0_1的栅极;nmos管n1的漏极接地;nmos管的栅极输入使能控制信号。

7、所述的增益控制电路包括多个pmos管p0,每个pmos管p0的源极均连接至电源vdd;每个pmos管p0的漏极连接在一起形成增益控制电路的输出端,用以连接至pmos管p1_0或p1_1的源极;每个pmos管p0的栅极分别输入驱动控制信号pctrl<0:n>,用以分别驱动每个pmos管p0的导通与否。

8、所述的控制电路还包括幅值校正电路,所述幅值校正电路用于对端子vx1、vx2输出电压幅值进行调整,其用于分别连接至端子vx1、vx2。

9、所述的幅值校正电路包括第一幅值校正电路和第二幅值校正电路,第一幅值校正电路连接至端子vx1,第二幅值校正电路连接至端子vx2。

10、所述的第一幅值校正电路和第二幅值校正电路均分别包括多个nmos管n2,第一幅值校正电路中:每个nmos管n2源极均连接至端子vx1,每个nmos管n2的漏极均连接至vss,每个nmos管n2的栅极分别输入驱动信号nctrl0<0:n>;第二幅值校正电路中:每个nmos管n2的源极均连接至端子vx2,每个nmos管n2的漏极均连接至vss,每个nmos管n2的栅极分别输入驱动信号nctrl1<0:n>,驱动信号nctrl0<0:n>、驱动信号nctrl1<0:n>用于分别驱动每个nmos管n2导通状态。

11、所述控制电路还包括增益控制电流偏置模块,其用于根据寄存器控制来输出二进制数字信号控制码pctrl<0:n>。

12、所述控制电路还包括幅值校正电流偏置模块,其用于根据寄存器控制来输出二进制数字信号控制码nctrl0<0:n>、nctrl1<0:n>。

13、本发明的优点在于:对接收到的lvds差分信号电平进行转换控制以满足电平兼容的目的,避免电平不兼容对器件损坏等缺陷;电路简单,仅使用集成电路cmos工艺中的中高压mos管、低压mos管、以及电阻即可实现电平转换,宜于集成;利用中高压pmos可编程电流控制,配合中高压pmos差分对,有效的限制差分输出信号幅值,同时差分输出信号增益实现了可调节的目的。利用改变低压nmos流过的电流大小,实现了改变vx1/vx2中单个输出信号的幅值,有效抑制和改善在芯片在制造过程中产生的失配效应,以及在lvds长距离传输过程中传输途径差异带来信号失配现象。

技术特征:1.一种控制电路,其特征在于:包括:pmos管p1_0、p1_1、增益控制电路和nmos管n0_0、n0_1;接收的lvds差分信号分别送入到端子pad_dn和端子pad_dp;端子pad_dn经电阻r4连接至pmos管p1_1的栅极;端子pad_dp经电阻r3连接至pmos管p1_0的栅极;端子pad_dn和端子pad_dp通过电阻r2连接;pmos管p1_0的源极和pmos管p1_1的源极连接在一起后接入到增益控制电路的输出端;

2.如权利要求1所述的一种控制电路,其特征在于:所述控制电路还包括nmos管n1,nmos管n1的源极连接至nmos管n0_0或n0_1的栅极;nmos管n1的漏极接地;nmos管的栅极输入使能控制信号。

3.如权利要求1所述的一种控制电路,其特征在于:所述的增益控制电路包括多个pmos管p0,每个pmos管p0的源极均连接至电源vdd;每个pmos管p0的漏极连接在一起形成增益控制电路的输出端,用以连接至pmos管p1_0或p1_1的源极;每个pmos管p0的栅极分别输入驱动控制信号pctrl<0:n>,用以分别驱动每个pmos管p0的导通与否。

4.如权利要求1-3任一所述的一种控制电路,其特征在于:

5.如权利要求4所述的一种控制电路,其特征在于:所述的幅值校正电路包括第一幅值校正电路和第二幅值校正电路,第一幅值校正电路连接至端子vx1,第二幅值校正电路连接至端子vx2。

6.如权利要求5所述的一种控制电路,其特征在于:所述的第一幅值校正电路和第二幅值校正电路均分别包括多个nmos管n2,第一幅值校正电路中:每个nmos管n2源极均连接至端子vx1,每个nmos管n2的漏极均连接至vss,每个nmos管n2的栅极分别输入驱动信号nctrl0<0:n>。

7.如权利要求6所述的一种控制电路,其特征在于:在第二幅值校正电路中:每个nmos管n2的源极均连接至端子vx2,每个nmos管n2的漏极均连接至vss,每个nmos管n2的栅极分别输入驱动信号nctrl1<0:n>,驱动信号nctrl0<0:n>、驱动信号nctrl1<0:n>用于分别驱动每个nmos管n2导通状态。

8.如权利要求1-7任一所述的一种控制电路,其特征在于:

9.如权利要求1-7任一所述的一种控制电路,其特征在于:

技术总结本发明公开了一种控制电路,包括:PMOS管P1_0、P1_1、增益控制电路和NMOS管N0_0、N0_1;接收的LVDS差分信号分别送入到端子PAD_DN和端子PAD_DP;端子PAD_DN经电阻R4连接至PMOS管P1_1的栅极;端子PAD_DP经电阻R3连接至PMOS管P1_0的栅极;端子PAD_DN和端子PAD_DP通过电阻R2连接;PMOS管P1_0的源极和PMOS管P1_1的源极连接在一起后接入到增益控制电路的输出端;通过增益控制电路对电路中差分输入信号进行幅值调节,以满足电平转换的目的。技术研发人员:孙林,刘胜芳,赵铮骁,赵铮涛受保护的技术使用者:安徽熙泰智能科技有限公司技术研发日:技术公布日:2024/5/29本文地址:https://www.jishuxx.com/zhuanli/20240618/35604.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。