一种MEMS结构的制作方法

- 国知局

- 2024-07-27 12:32:21

一种mems结构技术领域[0001]本申请涉及半导体技术领域,具体来说,涉及一种mems(microelectro mechanical systems的简写,即微机电系统)结构。背景技术:[0002]mems传声器(即麦克风)主要包括电容式和压电式两种。mems压电传声器是利用微电子机械系统技术和压电薄膜技术制备的传声器,由于采用半导体平面工艺和体硅加工等技术,所以其尺寸小、体积小、一致性好。同时相对于电容传声器还有不需要偏置电压、工作温度范围大、防尘、防水等优点,但由于衬底受限使得制造成本较高制约着mems压电传声器的发展。[0003]针对相关技术中如何降低压电式mems结构的制造成本的问题,目前尚未提出有效的解决方案。技术实现要素:[0004]针对相关技术中制造成本较高的问题,本申请提出一种mems结构,能够降低制造成本。[0005]本申请的技术方案是这样实现的:[0006]根据本申请的一个方面,提供了一种mems结构,包括:[0007]衬底,具有贯穿的空腔;[0008]第一电极层,形成在所述衬底的正面上方并且覆盖所述空腔,其中,所述第一电极层的材料包括单层或多层二维材料;[0009]第一压电层,形成在所述第一电极层上方;[0010]第二电极层,形成在所述第一压电层上方。[0011]其中,第一支撑层形成在所述衬底的背面、所述空腔的顶部和侧壁上。[0012]其中,所述第一支撑层在形成所述第二电极层之后被去除。[0013]其中,所述第一支撑层的材料包括金属材料。[0014]其中,所述mems结构还包括振膜,所述振膜形成在所述衬底和所述第一电极层之间。[0015]其中,所述振膜的材料包括二维材料。[0016]其中,所述振膜的二维材料包括氮化硼、单层或多层石墨烯、云母中的一种或多种。[0017]其中,所述mems结构还包括:[0018]第二压电层,形成在所述第二电极层上方;[0019]第三电极层,形成在所述第二压电层上方;[0020]其中,所述第二压电层的材料与所述第一压电层的材料相同或不同,所述第一电极层、所述第二电极层和所述第三电极层的材料相同或不同。[0021]其中,所述衬底的材料选自柔性材料、玻璃、塑料、半导体材料中的一种或多种。[0022]其中,所述第一电极层的材料包括单层或多层石墨烯或其他导电材料,所述第二电极层的材料包括单层或多层石墨烯或其他导电材料。[0023]其中,所述第一压电层的材料包括具有压电特性的二维材料、氧化物、氮化物、三五族半导体材料或压电陶瓷中的一种或多种。[0024]其中,所述具有压电特性的二维材料包括二硫化钼(mos2)、二硒化钼(mose2)、二碲化钼(mote2)二硫化钨(ws2)、二硒化钨(wse2)、二碲化钨(wte2)、氮化硼(bn)中的一种或多种。[0025]其中,所述氧化物包括氧化镉(cdo)、氧化锌(zno)、氧化钙(cao)、氧化镁(mgo)、氧化镓(gao)中的一种或多种;所述氮化物包括氮化镓(gan)、氮化铝中的一种或多种;所述三五族半导体材料包括砷化铟(inas)、磷化铟(inp)、砷化铝(alas)、砷化镓(gaas)中的一种或多种;所述压电陶瓷包括有机压电膜、钙钛矿型压电膜或驰豫型压电膜中的一种或多种。[0026]与传统的通过先形成振膜和压电单元而后湿法或干法蚀刻形成背面空腔的方法相比,本申请可以采用激光穿孔或是其他方式先在衬底上形成空腔,从而降低了制造成本,而且降低了传统的背面蚀刻给mems结构造成的损伤或性能退化的几率。附图说明[0027]为了更清楚地说明本申请实施例或现有技术中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。[0028]当结合附图进行阅读时,根据下面详细的描述可以更好地理解本申请的各个方面。需要强调的是,根据行业的标准实践,各个部件未按比例绘制,并且仅用于说明目的。实际上,为了清楚的讨论,各个部件的尺寸可以任意地增大或减小。[0029]图1是根据本申请实施例的mems结构的制造方法的中间阶段的截面示意图;[0030]图2是根据本申请实施例的mems结构的制造方法的中间阶段的截面示意图;[0031]图3是根据本申请实施例的mems结构的制造方法的中间阶段的截面示意图;[0032]图4是根据本申请实施例的mems结构的截面示意图。具体实施方式[0033]下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员所获得的所有其他实施例,都属于本申请保护的范围。[0034]以下公开内容提供了许多不同的实施例或实例以实现本申请的不同特征。下面将描述元件和布置的特定实例以简化本申请。当然这些仅是实例并不旨在限定。例如,元件的尺寸不限于所公开的范围或值,但可能依赖于工艺条件和/或器件所需的性能。此外,在以下描述中,在第二部件上方或者上形成第一部件可以包括第一部件和第二部件直接接触形成的实施例,并且也可以包括在第一部件和第二部件之间可以形成附加的部件,从而使得第一部件和第二部件可以不直接接触的实施例。为了简化和清楚,可以以不同的尺寸任意地绘制各个部件。[0035]此外,为便于描述,空间相对术语如“在...之下(beneath)”、“在...下方(below)”、“下部(lower)”、“在...之上(above)”、“上部(upper)”等在本文可用于描述附图中示出的一个元件或部件与另一个(或另一些)元件或部件的关系。空间相对术语旨在包括除了附图中所示的方位之外,在使用中或操作中的器件的不同方位。装置可以其他方式定向(旋转90度或在其他方位上),本文使用的空间相对描述符可同样地作相应解释。另外,术语“由...制成”可以意为“包括”或者“由...组成”。[0036]根据本申请提供了一种mems结构的制造方法,该mems结构可以应用于麦克风。[0037]如图1所示,根据本申请实施例的mems结构的制造方法包括:[0038]参见图1,步骤s101:提供衬底10。在一些实施例中,衬底10的材料选自柔性材料、玻璃、塑料、半导体材料中的一种或多种。[0039]在一些实施例中,柔性材料包括但不限于聚乙烯(pe)、聚丙烯(pp)、聚苯乙烯(ps)、聚对苯二甲酸乙二醇酯(pet)、聚萘二甲酸乙二醇酯的(pen)、聚酰亚胺(pi)等。在采用柔性材料或玻璃或塑料的情况下,降低了mems结构的制造成本,还为广泛应用于可穿戴设备等提供了可能。[0040]在一些实施例中,半导体材料包括硅或任何合适的硅基化合物或衍生物(例如硅晶片、soi、sio2/si上的多晶硅)。[0041]步骤s102:在衬底10内形成贯穿衬底10的空腔11。[0042]步骤s103:将振膜24转移至衬底10的正面上方。此种情况下,振膜24覆盖空腔11。振膜24的材料包括二维材料。振膜24的二维材料包括氮化硼、单层或多层石墨烯、云母中的一种或多种。由于振膜24采用的是二维材料,使得该振膜24能通过范德华力附接至衬底10上。该振膜24可以利用气压或其他方式平整紧密地贴在衬底10的正面上方,有效地避免了转移覆盖不紧密、不能紧密贴附的弊端。而且,可以转移并贴附以下所讨论的各种二维材料。或者可以使用其他热处理的方法使得振膜24紧密贴附在衬底10上方。而且,以下所讨论的各种二维材料也可以通过热处理的方式实现各个层的紧密堆叠。[0043]值得注意的是,转移振膜24的步骤也可以省略或跳过,并不影响本申请的主旨。[0044]参见图2,步骤s104:在衬底10的正面上方形成第一电极层21,第一电极层21覆盖空腔11。其中,第一电极层21的材料包括单层或多层二维材料。该单层或多层二维材料包括单层或多层石墨烯或其他导电材料。单层或多层石墨烯仍然可以采用转移的方式附接至衬底10的正面上方。[0045]值得注意的是,在制造方法含有转移振膜24的步骤的情况下,作为第一电极层21的单层或多层石墨烯与作为振膜24的氮化硼或云母构成了范德华异质结(由于二维层状材料表面无悬挂键,不同二维原子层可以通过弱范德华力按特定顺序依次堆叠,形成具有原子级平整界面的异质结构,这种异质结构通常被称为范德华异质结)。当制造方法不含有转移振膜24的步骤的情况下,第一电极层21形成在衬底10上方,该第一电极层21包括二维材料,使得第一电极层21与衬底10之间构成了范德华异质结。[0046]与传统半导体异质结相比,范德华异质结不受相邻原子层之间必须晶格匹配的限制,理论上可以像堆积木一样将多个原子层以任意形式(包括但不限于不同种类、角度、顺序、层数等)堆叠。由于二维层状材料种类多样、性质各异,因此范德华异质结任意搭配的特性可以把这些材料结合到一起,并仍保持超薄的厚度。[0047]步骤s105:在衬底10的背面共形沉积第一支撑层25,第一支撑层25形成在空腔11的顶部和侧壁。[0048]在含有振膜24的实施例中,第一支撑层25与在空腔11顶部的振膜24接触。在不含有振膜24的实施例中,第一支撑层25与在空腔11顶部的第一电极层21接触。第一支撑层25的材料包括金属材料。在一些实施例中,第一支撑层25的材料包括铝,用于为在第一支撑层25上方的各层材料提供支撑,提高后续工艺的可靠性。此外,可以在形成振膜24之后再形成第一支撑层25,然后在振膜24上方形成第一电极层21。[0049]值得注意的是,形成第一支撑层25的步骤也可以省略或跳过,不影响本申请的主旨。[0050]参见图3和图4,步骤s106:在第一电极层21上方依次形成第一压电层22和第二电极层23。第一压电层22的材料包括具有压电特性的二维材料、氧化物、氮化物、三五族半导体材料或压电陶瓷中的一种或多种。[0051]在一些实施例中,具有压电特性的二维材料包括二硫化钼(mos2)、二硒化钼(mose2)、二碲化钼(mote2)二硫化钨(ws2)、二硒化钨(wse2)、二碲化钨(wte2)、氮化硼(bn)中的一种或多种。氧化物包括氧化镉(cdo)、氧化锌(zno)、氧化钙(cao)、氧化镁(mgo)、氧化镓(gao)中的一种或多种;氮化物包括氮化镓(gan)、氮化铝中的一种或多种;三五族半导体材料包括砷化铟(inas)、磷化铟(inp)、砷化铝(alas)、砷化镓(gaas)中的一种或多种;压电陶瓷包括有机压电膜、钙钛矿型压电膜(例如pzt)或驰豫型压电膜(例如铌镁酸铅-钛酸铅pmn-pt)的一种或多种。[0052]在一些实施例中,第二电极层23的材料包括单层或多层石墨烯或其他导电材料。[0053]步骤s107:在第二电极层23上方形成掩模层(图中未示出),然后去除第一支撑层25,该掩模层保护第二电极层23不被去除。值得注意的是,在省略或跳过形成第一支撑层25的情况下,可以省略或跳过步骤s107。[0054]步骤s108:在第二电极层23上方依次形成第二压电层(图中未示出)和第三电极层(图中未示出)。此种情况下,所制造的mems结构包括依次层叠的第一电极层21、第一压电层22、第二电极层23、第二压电层和第三电极层,提高了mems结构的压电转换性能。[0055]在一些实施例中,第二压电层的材料与第一压电层22的材料相同或不同。第一电极层21、第二电极层23和第三电极层的材料相同或不同。[0056]值得注意的是,可以省略或跳过步骤s108。[0057]综上,本申请的mems结构的制造方法中,先在衬底10内形成贯穿衬底10的空腔11,然后通过转移贴附的方式在衬底10上方依次形成第一电极层21、第一压电层22和第二电极层23。一方面,与传统的通过先形成振膜24和压电单元而后湿法或干法蚀刻形成背面空腔11的方法相比,本申请可以采用激光穿孔或是其他方式先在衬底10上形成空腔11,从而降低了制造成本,而且降低了传统的背面蚀刻给mems结构造成的损伤或性能退化的几率。另一方面,由于本申请中将厚度薄且弹性强的二维材料应用于振膜24、第一电极层21、第一压电层22、第二电极层23、第二压电层、第三电极层中的一个或多个,使得可以转移并贴附各个超薄厚度层,实现了各个超薄厚度层的堆叠,从而可以减小mems结构的制造成本,可以广泛用于可穿戴设备或其他利用该mems结构的领域。[0058]如图4所示,根据本申请的实施例,还提供了一种mems结构,包括:[0059]衬底10,具有贯穿的空腔11;[0060]第一电极层21,形成在衬底10的正面上方并且覆盖空腔11,其中,第一电极层21的材料包括单层或多层二维材料;[0061]第一压电层22,形成在第一电极层21上方;[0062]第二电极层23,形成在第一压电层22上方。[0063]在一些实施例中,第一支撑层25形成在衬底10的背面、空腔11的顶部和侧壁上。并且第一支撑层25在形成第二电极层23之后被去除。[0064]在一些实施例中,mems结构还包括振膜24,振膜24形成在衬底10和第一电极层21之间。[0065]在一些实施例中,mems结构还包括:第二压电层,形成在第二电极层23上方;第三电极层,形成在第二压电层上方;其中,第二压电层的材料与第一压电层22的材料相同或不同,第一电极层21、第二电极层23和第三电极层的材料相同或不同。[0066]以上的衬底10、振膜24、第一电极层21、第一压电层22、第二电极层23、第二压电层、第三电极层以及第一支撑层25的材料已在上述mems结构的制造方法中进行了说明,在此不再赘述。[0067]以上所述仅为本申请的较佳实施例而已,并不用以限制本申请,凡在本申请的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本申请的保护范围之内。

本文地址:https://www.jishuxx.com/zhuanli/20240726/122312.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

扭矩传感器的制作方法

下一篇

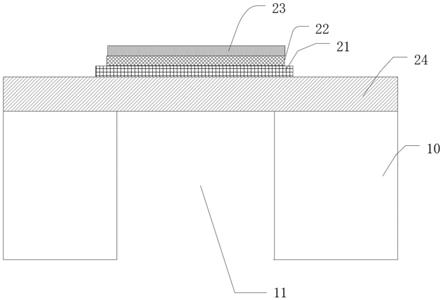

返回列表