半导体结构的制作方法

- 国知局

- 2024-07-27 12:38:48

半导体结构1.本技术涉及用于支撑机械、电气和/或机电部件、装置和/或系统的结构,并且涉及制作此类结构的方法。特别地,本技术涉及用于支撑小型化换能器和/或集成电路的结构,并且涉及用于制作和包装此类结构的技术。2.例如许多小型化部件、装置或系统并入半导体材料,诸如硅、锗和砷化镓。通常,通过晶片处理技术同时制造多个半导体部件和/或装置和/或系统。因此,半导体材料的晶片经受多个处理步骤,以便在晶片上制作多个单独装置或电路。随后切割晶片,因此创建多个单独管芯。3.因此,离散的管芯或“芯片”可包括部件,诸如具有特定功能的换能器部件。另外地或替代地,离散的管芯可包括至少一个电子电路部件。4.在简化电子部件的制造、测试和包装的愿望的推动下,半导体管芯制作和包装技术正在迅速发展。应当了解,在单个操作中处理多个半导体部件(通常称为“批量处理”)是非常有利的。批量处理(可能包括单个晶片处理或多个晶片的处理)可包括晶片级处理技术,所述批量处理具有成本效益并且产生一致且可重复的结果。5.本发明方面和示例涉及用于支撑小型化部件、装置或系统的结构。特别地,但不排他地,本发明方面涉及用于支撑并入半导体材料的小型化部件、装置和/或系统(例如,mems换能器管芯和/或集成电路(ic))的结构。特别地,本发明方面寻求提供特别适合用于晶片和/或批量级处理技术的支撑结构。本发明方面还涉及包装件设计和晶片级包装技术。6.根据第一方面的示例,提供了一种半导体晶片,包括多个主管芯,至少一个主管芯包括从半导体晶片的上表面延伸穿过半导体晶片到半导体晶片的下表面的孔,其中所述孔适合用于接收次管芯。7.在本公开中,术语“孔”可与术语“孔洞”互换使用。在本公开的情境中,认为在半导体晶片中形成的孔或孔洞是完全不存在形成半导体晶片的材料中的任何一者的区域。该孔一直不受阻碍地延伸穿过半导体晶片的平面,并将晶片部分的表面正上方的区域连接到晶片部分的表面正下方的区域。可认为孔是在晶片的平面内形成的平面内不存在的区域。8.根据本发明方面,所述孔适合用于接收次管芯。根据本发明示例中的一个或多个,意在位于孔内的次管芯将具有给定或预定义的长度(x)和宽度(y)。根据至少一个示例,半导体晶片的给定晶片部分的孔表现出大于或等于次管芯的长度和宽度的长度和宽度。9.根据至少一个示例,在晶片的给定主管芯部分的一个所述孔内提供次管芯。可认为次管芯包括一种结构,该结构支撑或限定一个或多个部件,包括电气和/或机械部件。次管芯具有长度和宽度。优选地,半导体晶片的给定晶片部分的孔表现出大于次管芯的长度和宽度的长度和宽度。10.次管芯可包括换能器管芯和/或电路管芯(例如,ic)。次管芯或每个次管芯的横截面积可小于其内提供了次管芯的相应孔的横截面积。根据至少一个示例,可借助于模制、粘合剂或接合类型的材料将次管芯支撑在给定主管芯的孔内。模制材料可提供在次管芯的外周与相应孔的侧壁之间。粘合剂材料可包括例如聚合物或环氧树脂类型的材料,并且优选地是可硬化或可固化的材料,其可以液体形式应用,并且当硬化时,用于通过在次管芯与孔的侧壁之间提供接合材料,将次管芯紧固在孔内。11.可认为次管芯是根据特定的技术工艺和/或技术节点制作而成的,所述技术工艺和/或技术节点可与形成相应主衬底的半导体晶片的技术工艺/节点相同或不同。12.可认为通常将包括半导体材料的次管芯在形式上总体是平面的。次管芯的平面尺寸因此由次管芯的长度和宽度限定。因此,根据至少一个示例,当次管芯被定向时,使得次管芯的平面与相应的半导体主管芯的平面基本对准或基本平行,其中孔被成形并且充分地定大小以适应次管芯的平面尺寸。13.次管芯的示例是半导体管芯。在本公开的情境中,“管芯”或“芯片”应理解成意指半导体材料的个别块。通常,在对晶片进行切割(即切单)之后,会生成管芯。管芯可限定或支撑一个或多个部件。例如,管芯可包括集成电路管芯,所述集成电路管芯包括一个或多个电路部件以提供功能电路。管芯可另外地或替代地包括换能器或传感器,诸如mems换能器。14.根据第一方面的至少一个示例,至少一个主管芯还包括:15.mems换能器,所述换能器提供在所述管芯的换能器区域中,其中所述主管芯的半导体晶片材料形成所述mems换能器的衬底。16.mems换能器可能是例如mems传声器换能器。mems传声器换能器通常包括覆盖空腔的柔性膜。根据本发明方面,给定主管芯的mems换能器的空腔可与主管芯的孔或孔中的至少一个同时形成在主管芯的下表面中。因此,可认为mems传声器换能器是通过涉及处理主管芯的换能器区域的半导体材料的工艺形成的。17.根据第一方面的至少一个示例,主管芯中的每个还包括:18.电路区域,所述电路区域包括在所述电路区域中的至少一个电路部件。19.因此,可认为至少一个电路部件是通过涉及处理主管芯的电路区域的半导体材料以限定至少一个电路部件的工艺形成的。可处理电路区域以限定至少一个电子电路。20.根据第二方面的至少一个示例,提供了一种包括多个主管芯的半导体晶片,至少一个主管芯包括:21.mems换能器,所述换能器提供在主管芯的换能器区域中;以及22.孔,所述孔提供在主管芯的孔区域中,其中所述孔从主管芯的上表面延伸穿过主管芯到半导体晶片的下表面,其中每个孔适合用于接收次管芯。23.根据第三方面的至少一个示例,提供了一种半导体晶片,所述半导体晶片包括多个晶片部分,所述晶片部分中的至少一些限定主管芯并且包括:24.电路区域,所述电路区域包括至少一个电路部件;以及25.至少一个孔,所述至少一个孔从半导体晶片的上表面延伸穿过半导体晶片到半导体晶片的下表面,其中所述孔适合用于接收次管芯。26.根据第四方面的至少一个示例,提供了一种半导体晶片,所述半导体晶片包括多个晶片部分,所述晶片部分中的至少一些包括:27.mems换能器,所述换能器形成在晶片部分的换能器区域中;28.不存在的区域,所述不存在的区域是半导体晶片的材料已经被移除的区域,所述不存在的区域在由晶片的上表面限定的第一平面与由晶片部分的下表面限定的第二平面之间延伸。29.根据第五方面的至少一个示例,提供了一种设备,包括:30.i)半导体晶片,包括多个晶片部分,每个晶片部分限定主衬底并且包括从半导体晶片的上表面延伸穿过半导体晶片到半导体晶片的下表面的至少一个孔;31.ii)次衬底,该次衬底具有长度和宽度;32.其中,半导体晶片的给定晶片部分的孔表现出大于或等于次衬底的长度和宽度的长度和宽度。33.支撑或包括小型化(例如,mems)换能器和/或ic的衬底通常容纳在一种包装件中,所述包装件允许容易处理和组装并用于保护装置免受例如机械损坏、rf噪声和环境污染。该包装件还提供了一种用于将包装件连接到电路板或其他元件的装置。为电子系统创建包装件涉及众多处理步骤和阶段。在常规的包装技术中,完成的晶片被切割成各个芯片,然后将这些芯片接合并电气地连接到包装衬底(诸如例如pcb衬底),并且然后进行封装。晶片级包装涉及在管芯仍然是管芯晶片的一部分的同时并且在切割成接合的管芯之前以及将帽晶片切割成各个包装的部件之前,将包括管芯的晶片(即,管芯晶片)与另一合适的处理过的帽晶片(即,帽晶片)一起包装34.根据第六方面的至少一个示例,提供了一种根据本发明方面中的任何一个的示例并且还包括至少一个盖或帽结构的半导体晶片,所述盖结构被提供用于至少一个主管芯。35.因此,每个盖结构可包括金属(例如,锡)盖,所述盖被支撑在相应主管芯的上表面上。根据另一示例,每个盖结构可包括pcb(印刷电路板),该pcb提供在覆盖相应主管芯的平面的平面中。在这种情况下,每个主管芯可设置有间隔物结构,该间隔物结构安装在主管芯的上表面上并且用于相对于主管芯间隔和支撑pcb盖结构。36.应当了解,能够提供相对于多个主管芯的包装件或盖结构作为晶片级包装工艺的一部分是有利的。因此,根据第七方面的至少一个示例,提供了一种包括第一晶片和第二晶片的晶片包装件,所述第一晶片包括根据本发明方面的示例的半导体晶片,而所述第二晶片包括帽晶片,所述帽晶片限定多个帽结构,每个帽结构被提供用于半导体晶片的对应晶片部分。37.根据第八方面的至少一个示例,提供了一种通过切割根据第一方面至第六方面的示例的半导体晶片而形成的主管芯。38.根据第九方面的至少一个示例,提供了一种mems换能器,包括39.衬底,所述衬底中形成有空腔40.膜,所述膜覆盖所述空腔41.其中,所述衬底包括横向延伸部分,并且其中在所述横向延伸部分中形成孔,所述孔从所述衬底的上表面延伸穿过所述衬底到所述衬底的下表面。42.根据至少一个示例,次管芯固定地提供在穿过主管芯部分形成的一个或多个孔内。43.因此,本发明方面涵盖半导体结构,该半导体结构除了至少一个孔之外,还包括空白或未处理的半导体材料,或者包括已处理半导体材料的至少一个区域。例如,可处理半导体材料的给定区域以提供电子电路。替代地或另外地,可处理半导体材料的给定区域以提供换能器,诸如mems传声器换能器。44.为了更好地理解本发明,并且为了示出可如何实施本发明,现在将仅通过举例的方式参考附图,其中:45.图1示出了半导体晶片和相应的单个管芯;46.图2示出了半导体晶片和相应的单个管芯。47.图3示出了mems传声器包装件;48.图4示出了另一种类型的换能器包装件;49.图5示出了根据第一示例的半导体晶片和主管芯;50.图6示出了根据第二示例的半导体晶片和主管芯;51.图7示出了根据另一示例的半导体晶片和对应的主管芯的各种视图;52.图8和图9示出了制作与图7d中示出的支撑结构相似的支撑结构的工艺;53.图10示出了根据另一示例的半导体晶片和对应的主管芯;54.图11示出了根据另一示例的半导体晶片和对应的衬底管芯;55.图12、图13、图14和图15示出了根据更多示例的各种不同结构;56.图16示出了根据一个示例的帽晶片;并且57.图17示出了包括与图7d中示出的主管芯相似的主管芯的换能器包装件。具体实施方式58.贯穿本描述,与其他图中的特征相同或相似的任何特征都被赋予相同的附图标记。59.本发明示例总体上涉及用于支撑电子和/或机电部件和/或系统的支撑结构。此类支撑结构通常由半导体材料的晶片制作而成。60.图1示出了半导体晶片和相应的单个管芯。具体地,图1a示意性地示出了包括多个晶片部分100的半导体晶片10。每个晶片部分100限定管芯并且被处理以形成诸如mems电容式换能器等换能器200。图1b示出了在切割晶片之后形成并且包括换能器200的单个或离散的换能器管芯100。图1c提供了穿过图1b中示出的离散或单片管芯100的线a‑a的说明性横截面视图。61.图2示出了半导体晶片和相应的单个管芯。62.具体地,图2a示意性地示出了包括多个晶片部分100'的半导体晶片10。在该示例中,每个晶片部分100'限定包括换能器部件200和电子电路部件的管芯。电子电路可被提供用于换能器200的操作和/或与换能器一起操作,并且将被电气地和可操作地耦合至换能器。图2b示出了包括两者集成在同一衬底上的换能器200和电路300的单个管芯100。如图2c中所示,提供了通过图2b中示出的管芯的线a‑a的说明性横截面视图,电路部分300通常制作在管芯100的上表面处,延伸到管芯的上表面中。63.包括mems装置和/或电子电路的半导体部件通常容纳在一种包装件中,所述包装件允许容易处理和组装并用于保护装置免受例如机械损坏、rf噪声和环境污染。该包装件还提供了一种用于将包装件电气地和机械地连接到电路板或其他元件的装置。64.各种先前提出的包装配置是已知的。例如,用于mems换能器的包装件通常包括:包装衬底,所述包装衬底可由印刷电路板(pcb)形成;以及罩盖部分,所述罩盖部分在覆盖包装衬底的上表面的由侧壁支撑的平面中延伸。罩盖部分和侧壁可由附接到包装衬底的上表面的金属盖提供。替代地,罩盖部分和侧壁可由另外两个pcb形成。三个pcb接合在一起,其中中间pcb包括限定包装件的腔室的开口。一个或多个管芯被堆积到包装衬底的上表面在腔室内,例如mems换能器管芯和电路管芯(ic)。65.用于电子系统的包装件的制作涉及众多阶段。创建包装的芯片所涉及的制造步骤统称为“包装”。66.图3示出了先前提出的mems传声器包装件400a,包括包装衬底450和罩盖401。包括mems换能器200的半导体衬底100容纳在包装件内部。罩盖401位于换能器芯片100上方并且附接到包装衬底的第一表面。罩盖401可能是金属盖。换能器200可能是mems传声器,并且罩盖401中的孔402提供声音端口以便允许声学信号进入包装件并刺激换能器。在该示例中,换能器200经由换能器和包装衬底的上表面上的接合焊盘以及接合引线电气地耦合至包装衬底450。67.在替代布置(未示出)中,包装件可容纳芯片100',该芯片包括与图2b和图2c中示出的示例相似的换能器和集成电路。68.图4示出了先前提出的另一种类型的换能器包装件400b。在该示例中,包装件容纳换能器芯片100(该换能器芯片包括换能器200)和离散的集成电路(ic)350。因此,在该示例中,换能器100和ic 350被共同包装。ic 350电气地连接到换能器200并且还电气地接合到包装衬底450。ic 300经由引线接合而接合到换能器和包装衬底。罩盖410位于包装衬底450上,以便包围换能器200和ic 350。在该包装件中,罩盖410包括上部部分或盖部分410a和侧壁410b,它们通常都由pcb(即,fr4)形成。在该示例中,换能器是传声器换能器,而罩盖410在上部部分410a中具有声音端口402,该声音端口允许声学信号进入包装件。69.应当了解,根据以上示例,换能器管芯和/或电路管芯是安装在包装衬底的第一上表面上的离散部件。芯片的通常通过自动“取放”循环的放置需要高度的准确性和可重复性,这可能很难达成。70.图5示出了第一示例。具体地,图5a示出了根据第一示例的半导体晶片50的平面视图。半导体晶片50包括多个晶片部分,并且可认为晶片部分中的至少一些限定了主管芯。每个主管芯500包括晶片材料中的孔洞或孔501,所述孔洞或孔从晶片衬底的上表面一直延伸穿过晶片部分到晶片衬底的下表面。可认为孔洞是晶片的半导体材料已经被移除或不存在的区域。此外,可认为孔洞或孔将相应晶片部分的上表面正上方的区域连接到晶片部分的下表面正下方的区域。因此,可认为孔暴露了半导体晶片部分的上表面和下表面两者中的开口。应当注意,在已经完成晶片半导体化工艺步骤之后,孔洞或孔具有通向光、流体等的不受阻碍的路径。多个孔洞可形成为诸如蚀刻等晶片级处理步骤的一部分。可认为图5a中示出的结构是半导体晶片晶格。71.在对半导体晶片进行切割之后,并且如图5b中所示,多个晶片部分将各自限定离散的或单片的主管芯500。应当了解,当晶片处于图5a中示出的状态时,可能会发生切割晶片的步骤。替代地,晶片的切割可在一个或多个进一步的“晶片级”处理阶段—即晶片作为整体在晶片上执行并且在晶片被切割之前的处理阶段—完成之后发生。额外的晶片级处理阶段可例如包括:在孔501内提供和紧固一个或多个次管芯;沉积一个或多个层(诸如,再分布层)到晶片的上表面和/或下表面;或者用于遮盖多个晶片部分的晶片级包装工艺。因此,应当了解,根据本发明方面的一个或多个示例的工艺可生成多个中间产品。72.图5c提供了沿图5b的线a‑a'截取的离散主管芯500的说明性截面视图。可认为主管芯500是主衬底或空白管芯衬底(bds),并且可例如在包装结构中形成衬底。虽然未在图5中示出,但是主管芯500可设置有一个或多个硅通孔(tsv)和作为晶片级处理的一部分创建的相关联的接合焊盘。如本领域中所理解的,tsv是完全穿过硅管芯的竖直电气连接,并且可与相关联的接合焊盘结合使用,作为到下一级互连的电气互连。因此,在主管芯充当衬底(例如,换能器包装衬底)的布置中,tsv和相关联的接合焊盘有益地促进了穿过衬底的平面形成的电气连接。如图5c中所示,每个孔洞或孔501限定在第一上平面x与第二下平面y之间的管芯内形成的晶片材料不存在区域。上平面x由主管芯(或晶片衬底)的第一上表面限定(即,与其重合),而下平面y由主管芯(或晶片衬底)的第二下表面限定(即,与其重合)。73.根据本发明示例,在晶片材料中提供的孔洞或孔501适合用于接收离散管芯或ic。因此,孔洞被充分地定大小,以至少部分地适应离散的衬底部分。根据本发明示例,可认为限定管芯500的晶片部分是主管芯或母管芯,同时可认为意在接收在孔洞501内的离散管芯是次管芯或子管芯。也可认为次管芯是次衬底。在本发明示例中,孔洞的形状为矩形,并且由长度x、宽度y和深度z限定。然而,应当了解,孔洞可能是任何其他形状,包括但不限于:圆形;六边形;正方形;矩形;“l”形;或“c”形,前提是适合用于接收次半导体管芯。特别地,孔洞可被充分地定大小,以适应预期的次管芯的平面尺寸—即x(宽度)尺寸和y(长度)尺寸。优选地,孔洞的平面尺寸略大于预期的次管芯的平面尺寸。因此,次管芯配合在孔内,当被定向时,使得次管芯的平面与晶片的平面基本对准或平行。74.根据本发明示例中的一个或多个,每个晶片部分或半导体化主管芯可包括多个孔,每个孔从晶片部分或衬底管芯的上表面延伸穿过晶片部分或衬底管芯到晶片部分或衬底管芯的下表面。每个孔都适合用于接收至少一个次管芯。图12示出了包括一个或多个非限制性示例孔的各种不同的衬底结构。应当了解,根据本发明示例的主衬底或bds提供了一种通用结构,用于支撑多个和/或一系列机械、电气和/或机电部件、装置和/或系统,包括例如ic和/或mems换能器。特别地,根据本发明示例中的一个或多个,设想单个主管芯或bds可设置有至少两种不同类型的机械、电气和/或机电部件,因此促进系统的各种不同的部件集成到单个(即,单片)管芯的衬底内。这为节省大量空间和包装制造处理步骤、包装成本等提供了潜力。75.图6示出了包括一行晶片部分的晶片的一部分的放大视图,晶片部分中的每个限定一个主管芯500。图6a以平面视图示出了该行晶片部分,而图6b提供了横截面视图。次或“子”管芯550提供在形成于晶片部分500中的孔501中的每个中。在该示例中,次管芯中的每个都借助于填充物或支撑材料520支撑在相应的孔内。如本领域技术人员将理解的,通过包覆成型将粘合剂或接合材料520引入主管芯与次管芯之间的空间中。76.次管芯可能是例如换能器管芯或电路管芯。应当了解,提供在至少一行晶片部分的孔内或整个晶片的孔内的次管芯可能都共享相同的功能,并且它们本身可作为批量(例如,晶片级)制作工艺的一部分制作而成。因此,就提供在晶片或晶片行的孔内的次芯片的类型、功能性或类别而言,可认为晶片是同质的。替代地,就次管芯的功能而言,次管芯中的一个或多个可不同于同一行或不同行中的一个或多个其他次管芯。因此,就提供在晶片或晶片行的孔内的次芯片的类别类型而言,可认为晶片是异质的。根据特定示例,孔中的一个或多个设置有离散的mems换能器管芯,诸如mems传声器换能器管芯。根据另一特定示例,孔中的一个或多个设置有离散的电路管芯,诸如ic。77.在晶片的非半导体处理期间,包括在将次管芯550放置在多个晶片部分500的孔501内期间,如本领域中已知的,可将晶片支撑在载体530上。因此,多个次管芯可放置在孔内,以便在次管芯的外周表面与限定相应孔501的边界形状的晶片材料的表面之间留下横向缝隙或间隙。因此,次管芯被有益地支撑,同时可供应流体填充物或支撑材料520(诸如,例如环氧树脂),以便填充横向缝隙。一旦填充物材料已经硬化或凝固,可在稍后的阶段移除通常呈片材形式的载体,并且因此将次管芯紧固或固定地支撑在孔内。78.图6c示出了可被认为是主管芯或母管芯的单个晶片部分500。主管芯500包括支撑(例如,嵌入或封装)在孔50内的次管芯或子管芯。可认为孔501是半导体晶片材料不存在的区域。因此,即使如图6c中所示,已经用次管芯和填充物材料填充孔或孔洞,但是仍然有晶片材料不存在的区域501。如图6c中所示,可认为离散的次管芯集成在由晶片部分500限定的硅衬底或主管芯内。特别地,次管芯集成在主管芯的平面内。主管芯可设置有tsv和相关联的接合焊盘(未示出)。79.应当了解,进一步的非半导体晶片级处理可在切割晶片发生之前发生,例如以便为主管芯与次管芯之间的一个或多个电气连接提供一个或多个再分布层。如本领域普通技术人员将理解的,此类再分布层以批量处理方式应用于整个晶片。80.在另一示例中,每个晶片部分包括两个以上的孔洞或孔,每个孔适合用于接收离散的次管芯。因此,孔洞中的每个被充分地定大小,以接收另一离散的管芯部分。可借助于填充物材料将离散的管芯支撑在晶片部分的给定孔内。因此,孔可被充分地定大小,以使得给定的孔或孔洞的平面尺寸大于预期芯片的平面尺寸。81.根据本发明实施方案的特定示例,给定主管芯的第一孔洞可包括换能器管芯,诸如mems传声器换能器管芯,而所述主管芯的第二孔洞可包括电路管芯,诸如用于从换能器芯片接收输出信号的ic。因此,主管芯包括两个嵌入式次管芯,可认为所述两个嵌入式次管芯集成在同一主管芯衬底内。可有利地使用一个或多个金属层或再分布层和/或至少一个tsv在嵌入式次管芯之间形成电气连接。82.图7示出了包括mems换能器和孔的半导体晶片和对应的主管芯的各种视图。83.因此,图7a示出了半导体晶片70的平面视图,该半导体晶片70包括根据第二示例的多个晶片部分,晶片部分中的至少一些限定了主管芯700。已经在主管芯的第一换能器区域t中处理了每个主管芯700,以提供mems换能器702。在该特定示例中,mems换能器包括mems传声器换能器。然而,应当了解,可在主管芯区域中的每个的换能器区域t中制作和/或提供其他类型的换能器,诸如加速度计、陀螺仪等。还设想了其中每个主管芯可设置有一个以上换能器的示例。此外,已经在晶片部分的第二孔区域a中处理了每个主管芯700,以在晶片材料中形成孔洞或孔701。84.如图7b中所示,在切割半导体晶片之后,晶片部分中的至少一些将限定主管芯700。因此,产物结构是主管芯或主衬底,包括形成在管芯的换能器区域t中的mems换能器和形成在管芯的孔区域a中的孔。85.应当了解,切割晶片的步骤可在晶片处于图7a中示出的状态时发生,但是也可在额外的晶片级处理阶段之后发生。因此,应当了解,在制作工艺的中间步骤期间形成了多个中间产品。86.图7c提供了沿图7b的线a‑a'截取的离散主管芯700的横截面视图。如图7c中所示,孔洞701限定的在第一上平面x与第二下平面y之间的衬底700内形成的晶片材料不存在区域。上平面x由主管芯的第一上表面限定(即,与其重合),而下平面y由主管芯的第二下表面限定(即,与其重合)。mems传声器换能器包括柔性膜710,所述柔性膜覆盖形成在晶片部分700的下表面中的空腔708。与提供在主管芯的换能器区域中的mems换能器的膜下面的空腔708相比,提供在主管芯的孔区域中的孔洞或孔701从晶片衬底的上表面中的第一开口完全延伸穿过晶片部分700到晶片衬底的下表面中的第二开口。特别地,由孔限定的主管芯的上表面中的开口允许次管芯从晶片正上方的区域经由第一开口位于所述孔内。87.晶片材料中的孔洞701适合用于接收离散管芯或芯片。因此,孔洞被充分地定大小,以至少部分地适应另一离散管芯。根据本发明示例,可认为衬底700是主管芯或母管芯,同时可认为意在接收在孔洞701内的管芯是次管芯或子管芯。在本发明示例中,孔洞的形状为矩形,并且由长度x、宽度y和深度z限定。然而,应当了解,孔洞可能是任何其他形状,前提是它适合用于接收次管芯。特别地,孔洞可被充分地定大小,以适应次管芯的平面尺寸——即x尺寸和y尺寸。优选地,孔洞的平面尺寸略大于预期的次管芯的平面尺寸。88.可认为本发明示例中的一个或多个包括次管芯,该次管芯可能是位于主管芯的孔内的装置或电路管芯。因此,如图7d中所示,主管芯700包括半导体衬底和形成在衬底的换能器区域中的mems换能器702。次管芯720位于mems换能器衬底内在孔区域中。因此,次管芯包括支撑在衬底的上平坦表面与下平坦表面之间的离散管芯。在这个意义上,可认为次管芯提供在主管芯的平面内。由于次管芯通常在载体片材的帮助下位于孔内,次管芯的下平坦表面将与由主管芯的下表面限定的平面基本齐平(即,与其重合)。mems换能器可借助于引线接合或有利地通过应用于主管芯的上表面和/或下表面的一个或多个再分布层(未示出)电气地连接到次管芯720。89.根据本发明示例中的一个或多个,限定主管芯的每个晶片部分可包括多个孔,每个孔从晶片部分或衬底管芯的上表面延伸穿过晶片部分或衬底管芯到晶片部分或衬底管芯的下表面。每个孔都适合用于接收至少一个次管芯。图13示出了图7b中示出的主管芯的若干变型或修改。在图13中示出的示例中的每个中,可被认为是主管芯的管芯700设置有单个mems换能器。主管芯还设置有一个或多个孔洞或孔701a……h,每个孔适合用于接收至少一个离散的次管芯或半导体管芯。90.现在将参考图8和图9描述制作与图7d中示出的支撑结构相似的支撑结构的工艺。91.图8a示出了半导体晶片80。晶片部分的晶片部分中的一个或多个限定主管芯800,并且被处理以提供mems传声器换能器802和孔801,所述孔从晶片部分的上表面延伸穿过晶片部分的半导体材料到晶片部分的下表面。92.便利地,在先前工艺期间,晶片被处理以在每个晶片部分上提供mems传声器换能器结构。然后,在根据本发明示例的后续处理阶段中,在主管芯800的下表面(背面)中在mems传声器换能器结构802下面的区域中形成换能器空腔(未示出)。空腔可以允许声压波入射到mems传声器换能器802的柔性膜上,或者为换能器802提供后容积。有利地,根据本发明示例,形成孔801的至少一部分的工艺可与例如通过蚀刻工艺形成换能器空腔同时发生。然而,应当了解,因为换能器空腔不一直延伸穿过管芯,所以形成孔的蚀刻工艺的开始时间可早于形成空腔的蚀刻工艺的开始时间。93.图8b示出了另一晶片85。晶片85包括多个晶片部分,所述多个晶片部分中的一个或多个限定电路管芯区域。晶片85被切割以形成多个电路管芯850。每个电路管芯可能是例如用于处理换能器装置802的输出的ic94.图9a至图9d示出了用于处理图8a中示出的晶片80的晶片级处理流程中的一系列阶段。图9a至图9e中的每个示出了晶片80'的一部分的俯视平面视图和横截面视图。95.在图9a中,晶片被提供在载体层830上,该载体层用于支撑晶片的孔801的区域,而包括如图8b中示出的ic的次管芯850定位在孔内。如图8a中所示,次管芯850的平面尺寸小于孔801的平面尺寸,并且在次管芯850的周边与孔801的侧壁之间存在缝隙或间隙。如图9b中所示,模制步骤涉及供应例如注射模制材料840,诸如环氧树脂模制材料。一旦模制材料已经凝固从而将次管芯850紧固在孔内,就如图9c中所示移除载体层830。可认为图9c中示出的产物结构是复合或混合结构,包括半导体晶片材料的平面框架或晶格以及至少部分地埋入或封装在晶片的平面内的多个离散次管芯。根据示出的示例,离散的次管芯的下平坦表面与晶片的下平坦表面齐平。96.图9d示出了通过rdl工艺施加再分布层的工艺。如本领域普通技术人员将理解的,rdl或再分布工艺通常涉及在处理过的晶片的顶表面上提供金属(例如,铜)镀层,以便再分布或再定位电气连接。出于说明的目的,rdl工艺通常涉及:97.施加第一层绝缘体,例如电介质材料,该第一层绝缘体仅暴露相应管芯上的接合焊盘接口;98.施加铜图案化,以确保用于焊接的相应接合焊盘接口之间的适当电气连接(诸如,在使用金属盖的情况下,i/o焊盘和盖轨道);以及99.施加第二电介质,该第二电介质将保护电气连接的铜表面免受氧化。100.图10示出了半导体晶片和对应的衬底管芯,包括电路和孔。101.因此,图10a示出了根据另一示例的半导体晶片90的平面视图。根据另一示例,晶片90包括多个晶片部分900。已经在晶片部分的电路区域c中处理了每个晶片部分900,以提供电子电路。此外,已经在晶片部分的孔区域a中处理了每个晶片部分900,以形成穿过晶片材料的孔洞或孔901。孔洞或孔901从晶片衬底的上表面中的开口延伸穿过晶片部分900到晶片衬底的下表面中的开口。102.如图10b中所示,在切割半导体晶片之后,每个晶片部分将限定离散的衬底900。因此,产物结构是衬底部分或衬底管芯,包括提供在管芯的电路区域c中的电路和形成在管芯的孔区域a中的孔。103.图14示出了根据图10b中示出的衬底管芯的变型的若干不同的衬底管芯。在图14中示出的示例中的每个中,可被认为是主管芯的管芯900设置有包括电子电路920的电路区域。主管芯还设置有一个或多个孔洞或孔901a……h,每个孔适合用于接收至少一个离散的次管芯。104.图11示出了半导体晶片和对应的主管芯,包括mems换能器、电路和孔。105.因此,图11a示出了根据另一示例的包括多个晶片部分600的半导体晶片60的平面视图。已经在晶片部分(即,管芯)的电路区域c中处理了每个晶片部分600,以提供集成电子电路。也已在晶片部分的换能器区域t中处理了每个晶片部分600,以提供mems换能器602。然而,应当了解,可在晶片部分中的每个的换能器区域t中制作和/或提供其他类型的换能器或装置。此外,已经在晶片部分的孔区域a中处理了每个晶片部分600,以在晶片材料中形成孔洞或孔601。孔洞或孔601从晶片衬底的上表面中的开口延伸穿过晶片部分900到晶片衬底的下表面中的开口。106.如图11b中所示,在切割半导体晶片之后,每个晶片部分将限定离散的衬底600。107.图15示出了根据图11b中示出的衬底管芯的变型的若干不同的衬底管芯。在图15中示出的示例中的每个中,可被认为是主管芯的管芯1000设置有单个电路区域和单个换能器区域702。主管芯还设置有一个或多个孔洞或孔h1……h6,每个孔都适合用于接收至少一个离散的次衬底管芯。108.根据本发明示例中的一个或多个,晶片的管芯或晶片部分设置有mems传声器换能器,可认为该换能器是输入换能器。使用mems制作工艺形成的传声器装置通常包括一个或多个膜,所述一个或多个膜具有沉积在膜和/或衬底上的用于读出/驱动的电极。在mems压力传感器和传声器的情况下,通常是通过测量电极之间的电容来完成读出。在输出换能器(诸如,例如mems扬声器)的情况下,通过静电力移动膜,所述静电力是通过改变跨电极应用的电位差而生成的。109.根据本发明方面的示例的单个主管芯将优选地容纳在一种包装件中,所述包装件允许容易处理和组装并用于保护主管芯和由此支撑的部件(例如,次管芯)免受例如机械损坏、rf噪声和环境污染。包装件还提供了一种用于将包装件连接到电路板或其他元件的装置,例如外部传导触点。为电子系统创建包装件涉及众多处理步骤和阶段。在常规的包装技术中,完成的晶片被切割成各个芯片,然后将这些芯片接合至包装衬底并进行封装。晶片级包装涉及在芯片仍然是晶片的一部分的同时以及在切割成各个包装件之前包装芯片。110.图16示出了包括多个帽晶片部分1010的帽晶片1100。帽晶片部分1010中的至少一些被处理成包括凹入区域1020。凹入区域可任选地镀有金属材料,以便充当rf噪声和干扰的屏障。可认为晶片是帽晶片,因为帽晶片部分中的每个限定了用于主管芯晶片的相应晶片部分的帽部分(或盖)。因此,根据本发明方面的工艺,可相对于根据本发明方面的示例的半导体晶片布置如图16中示出的帽晶片,以便限定包装件。因此,给定帽晶片部分的凹入区域限定侧壁,所述侧壁在称为晶片到晶片接合的工艺中安装到主衬底晶片部分的上表面。因此,帽部分与主管芯一起限定了包装腔室。有利地,根据本发明示例中的一个或多个,主管芯形成包装衬底,其中盖结构安装在主管芯上,并且因此不需要单独的包装衬底。因此,并入有根据一个或多个本发明示例的充当包装衬底的主管芯的包装件有益地达成了总体包装件高度的降低。111.容纳传声器换能器的包装件通常具有声音端口,以允许声波往返包装件内的换能器传输,并且换能器可被配置成使得柔性膜位于第一与第二容积(即,空间/空腔)之间,所述容积可能填充有空气(或适合用于传输声波的某一其他气体),并且被充分地定大小以使得换能器提供期望的声学响应。声音端口声学地耦合至换能器膜的一侧上的第一容积,所述第一容积有时可被称为前容积。通常需要在一个或多个膜的另一侧上的第二容积,有时称为后容积,以允许膜响应于入射的声音或压力波自由移动,并且该后容积可基本上是密封的(虽然本领域技术人员将了解,对于mems传声器等,第一容积和第二容积可通过一个或多个流动路径(诸如膜中的小孔洞)连接,所述流动路径被配置以便以期望的声学频率呈现相对较高的声学阻抗,但允许两个容积之间的低频压力均衡,以解决由于温度变化等引起的压差。)112.根据至少一个示例,其中主管芯包括mems传声器换能器,并且其中mems传声器换能器的空腔形成在主管芯的下侧中,也可认为空腔形成了包装件的声音端口。113.图17示出了包括与图7d中示出的主管芯相似的主管芯700的换能器包装件。因此,主管芯包括形成在衬底的换能器区域中的mems换能器702。次管芯720嵌入在主管芯(其形成mems换能器衬底)的孔内,所述孔限定在主管芯的上平坦表面与下平坦表面之间。主管芯还包括多个tsv 703,它们从内部接合焊盘704延伸穿过衬底的平面到外部接合焊盘705。rdl层706提供在主管芯的上表面上。帽部分1010安装在主管芯的上表面上,以限定mems传声器换能器702的后容积。114.在以上示例中的任何一个中,应当了解,虽然孔的平面尺寸(x尺寸和y尺寸)必须足以适应预期的次管芯的平面尺寸,但是次管芯可表现出小于、等于或大于孔的深度(z尺寸)的深度。因此,虽然可能有益的是能够在由给定晶片部分的孔限定的空腔内完全适应预期的次管芯,以使得次管芯不会突出到主管芯的上表面或下表面之上,但这不是必需的。实际上,在要例如借助于包装件盖结构等在主管芯的上表面的正上方区域中限定腔室并且该腔室的容积对已包装装置的性能具有影响的示例中,减少或最小化次管芯突出到主管芯的表面上方的量可能特别有利。例如,在主管芯包括具有相对于主管芯的上表面形成并覆盖从主管芯的下表面提供的空腔的柔性膜的mems传声器换能器的情况下,腔室将形成传声器换能器的后容积。因此,根据本发明示例中的一个或多个,可能够将asic嵌入主管芯的孔内,换言之在形成换能器的空腔的同一衬底内,并相较于先前提出的传声器换能器达成腔室内净空的获得和/或包装件高度的降低。115.在本发明示例和各方面的情境中设想,主管芯的孔可设置有次管芯,该次管芯是根据不同于主管芯的工艺节点的工艺节点或技术规模制作而成的。例如,可根据例如55nm技术节点工艺制作半导体晶片,同时可能已经通过80nm、22nm或甚至7nm技术处理节点制作次芯片。116.应当理解,如本文使用的术语“半导体材料”包括但不限于任何和所有:iv族元素/化合物半导体;vi族元素半导体;iii‑v族、ii‑vi族、i‑vii族、iv‑vi族、v‑vi族、ii‑v族、i‑iii‑vi族2半导体;氧化物;层状、磁性和/或有机半导体。117.本发明方面的示例特别适用于用于支撑mems传感器换能器的结构,尤其是诸如mems传声器等电容换能器。还应当了解,可实现其他类型的mems电容传感器,例如加速度计、压力传感器、接近度传感器或流量计。118.本发明方面的示例可在主机装置尤其是便携式和/或电池供电的主机装置中实现,所述主机装置诸如移动电话,以及音频播放器、视频播放器、pda、移动计算平台诸如例如笔记本计算机或平板电脑和/或游戏装置,或在附件装置(诸如耳机、耳塞(可能是降噪耳塞)或传声器组合件)中实现,所述附件装置被设计用于与此类主机装置进行有线或无线连接,可能经由多引线电缆、多极插孔或光纤和连接器。119.应当注意,上面提及的实施方案说明而非限制本发明,并且本领域技术人员将能够在不脱离所附权利要求的范围的情况下设计许多替代实施方案。词语“包括”不排除除了在权利要求中列出的要素或步骤之外的要素或步骤的存在,“一(a)”或“一(an)”不排除多个,并且单个特征或其他单元可履行在权利要求中叙述的几个单元的功能。权利要求中的任何附图标记或标签不应被解释为限制它们的范围。120.本技术包括以下陈述:121.陈述1a.一种半导体晶片,其包括多个晶片部分,每个晶片部分限定主衬底并且包括从半导体晶片的上表面延伸穿过半导体晶片到半导体晶片的下表面的至少一个孔,其中所述孔适合用于接收次衬底。122.陈述1b.一种半导体晶片,其包括多个管芯,至少一个管芯包括在管芯的上表面与下表面之间延伸穿过管芯的孔,其中所述孔适合用于接收半导体管芯。123.陈述1ba.一种半导体晶片,其包括多个第一管芯,至少一个第一管芯包括在管芯的上表面与下表面之间延伸穿过管芯的孔,其中所述孔适合用于接收半导体第二管芯。124.陈述1c.一种半导体晶片,其包括多个管芯,其中多个管芯的子集各自包括在管芯的上表面与下表面之间延伸穿过管芯的孔,其中所述孔适合用于接收半导体管芯。125.陈述1d.一种半导体晶片,其包括多个管芯,每个管芯包括在管芯的上表面与下表面之间延伸穿过管芯的孔,其中所述孔适合用于接收半导体管芯。126.陈述2a.一种第一半导体管芯,其包括在其上表面与下表面之间延伸的孔,其中所述孔适合用于接收第二半导体管芯。127.陈述3a.一种半导体晶片,其包括多个管芯,至少一个管芯包括:在换能器区域中的mems换能器;以及在孔区域中在管芯的上表面与下表面之间延伸穿过管芯的孔,其中所述孔适合用于接收半导体管芯。128.陈述3b.一种半导体晶片,其包括多个第一管芯,至少一个第一管芯包括:在换能器区域中的mems换能器;以及在孔区域中在至少一个第一管芯的上表面与下表面之间延伸穿过至少一个第一管芯的孔,其中所述孔适合用于接收半导体第二管芯。129.陈述4a.一种第一半导体管芯,其包括:在换能器区域中的mems换能器;以及在孔区域中在其上表面与下表面之间延伸的孔,其中所述孔适合用于接收第二半导体管芯。130.陈述5a.一种半导体晶片,其包括多个管芯,至少一个管芯包括:在电路区域中的电子电路;以及在孔区域中在管芯的上表面与下表面之间延伸穿过管芯的孔,其中所述孔适合用于接收半导体管芯。131.陈述5b.一种半导体晶片,其包括多个第一管芯,至少一个第一管芯包括:在电路区域中的电子电路;以及在孔区域中在至少一个第一管芯的上表面与下表面之间延伸穿过至少一个第一管芯的孔,其中所述孔适合用于接收半导体第二管芯。132.陈述6a.一种第一半导体管芯,其包括:在电路区域中的电子电路;以及在孔区域中在其上表面与下表面之间延伸的孔,其中所述孔适合用于接收第二半导体管芯。133.陈述7a.一种半导体晶片,其包括多个管芯,至少一个管芯包括:在换能器区域中的mems换能器;在电路区域中的电子电路;以及在孔区域中在管芯的上表面与下表面之间延伸穿过管芯的孔,其中所述孔适合用于接收半导体管芯。134.陈述8.一种第一半导体管芯,其包括:在换能器区域中的mems换能器;在电路区域中的电子电路;以及在孔区域中在其上表面与下表面之间延伸的孔,其中所述孔适合用于接收第二半导体管芯。

本文地址:https://www.jishuxx.com/zhuanli/20240726/122909.html

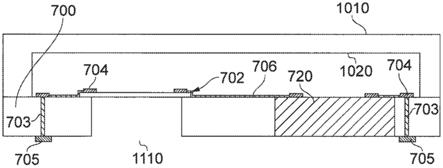

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。