晶片级封装的制作方法

- 国知局

- 2024-07-27 12:44:36

晶片级封装1.用于需要空腔的器件的晶片级封装技术被称为tfap(薄膜声学封装)。所有封装层都按顺序依次沉积和结构化,并且具有源自过程误差的安全距离,例如,叠加、过程偏移偏差和其他过程波动。这些安全距离确保各层以适当方式围合或重叠下面的层,以确保例如最终器件的功能。如果需要为封装层考虑更多的安全距离,则芯片上的功能结构会损失更多的区域。2.首先,生产牺牲层并且对其进行结构化,使得在结构化之后剩余的牺牲材料的结构对应于随后形成的空腔。在沉积刚性覆盖层(第一封装层)之后,可以通过第一封装层的释放孔蚀刻或溶解牺牲材料的结构。第一封装层在每个空腔上方形成圆顶。然后,再次关闭释放孔,并且在顶部上沉积一个或多个加固层。3.当前晶片级封装由于需要许多安全距离而受到空间使用次优的影响,这是由于互连和封装制造所采用的各种过程(以屏蔽声学免受外部影响)。这些导致“排除”区域不能用作有源滤波器和互连区域。4.本公开的一个目的是提供一种晶片级封装,该晶片级封装比目前使用的封装需要更少的空间,并且对敏感器件结构提供良好保护。5.一种晶片级封装包括具有顶部功能层的衬底,也就是说,作为顶部层的功能层。电气器件结构(例如,电极)在该功能层中、上或下实现。连接这些器件结构的焊盘被布置在衬底上,并且被连接到器件结构。第一封装层被施加在顶部表面上,并且限定保留在衬底与第一封装层之间的空腔。放置空腔以围合器件结构的至少一部分,使得它们被布置在其中。6.第二封装层被施加在第一封装层的整个表面上,并且可以覆盖部分或整个表面。从第一封装层和第二封装层暴露的是每个焊盘的部分区域。这些暴露的部分区域用作接触区域。在每个接触区域上,形成并布置互连结构,该互连结构在表面上方延伸到高于封装层的高度的高度。7.该晶片级封装可以用作需要最小衬底表面量的tfap封装。封装可以被直接整体形成在衬底上。另一优点是,由互连结构制成的互连可以根据器件结构的要求被单独放置在表面上,即,需要互连的地方以及焊盘可以有利地被放置在衬底的表面上的地方。8.晶片级封装也可以被形成在管芯级上。然而,所有封装结构都可以被形成在晶片级上。9.第二封装层用作晶片级封装的加强部分。同时,它可以用来定义接触区域。然后,可以专门在如此定义的接触区域上形成互连结构。10.第一封装层是介电层,并且可以是刚性无机层。它用于形成在其下围合空腔的圆顶。第二封装层可以是光敏聚合物层,例如,光敏抗蚀剂。然后,可以通过简单地将抗蚀剂暴露于扫描光源或通过借助光掩模将其暴露于光源来执行对第二封装层的结构化。曝光后,聚合物层被显影以使用溶剂或蚀刻方法去除非期望表面部分。如果使用正性光刻胶,则仅去除曝光区域,而如果使用负性光刻胶,则在显影过程期间仅可以去除未曝光区域。11.第一封装层可以由例如sio2或sin或任何其他合适介电材料形成。12.第二封装层不需要完全覆盖衬底表面和下面的第一封装层,并且可以让沿着衬底的所有边沿的边缘未被覆盖。然而,第二封装层也可以完全覆盖衬底表面和/或下面的第一封装层。13.根据一个实施例,接触区域中的一些接触区域和布置在其上的相应互连结构被第二封装层横向完全围合。这表明互连结构位于形成在第二封装层中的开口中并且互连完全占据这些开口。其他接触区域可以被布置在第二封装层的边沿处,使得它们仅部分被第二封装层围合。进一步地,梯形接触区域中的至少一些梯形接触区域可以被布置在衬底的边沿处。14.如已经提及的,第一封装层和第二封装层中的选定封装层中的开口或切口可以限定接触区域的形状。限定封装层可以选自第一封装层和第二封装层以及施加在第二封装层上的附加抗蚀剂层。开口可以被形成在第一封装层和第二封装层中,使得第一封装层和第二封装层形成开口的齐平结构边沿。15.可选附加抗蚀剂层并非封装的密封性或电阻所必需的层。然而,它可以被称为第三封装层。因此,与第一封装层和第二封装层的厚度相比,第三封装层可以是相对较薄的层。进一步地,它需要是电绝缘层,并且可以是介电层。16.在存在第三封装层的情况下,其结构边沿可以与第二封装层的结构边沿一致。17.根据一个实施例,因为器件结构对任何机械冲击敏感并且需要不受干扰地振动,所以它们是被封装在空腔内部的声学谐振器。18.互连结构可以包括cu柱。然而,其他材料也是可能的,并且可以实现互连结构,例如,作为焊料凸块。在任何情况下,互连结构的高度都延伸到所有其他封装层上,以允许它们接合到例如另一衬底或pcb的平面表面。为了接合的目的,cu柱的顶部可以涂覆有焊料层的焊料帽。19.第二封装层可以具有基本平行于衬底的表面延伸的平坦表面,并且可以包括可以容易地以平坦化方式施加的聚合物,例如,作为可以以液体形式应用的低粘度聚合物。20.然而,第二封装层的平坦化可以通过一种在施加机械压力和/或热量下的层压过程或通过飞切来完成。通过层压过程,可以使第二封装层软化、变形和平坦化。21.互连结构可以位于衬底上的任意位置处。大多数互连结构可以由第二封装层包围。然而,根据示例,互连结构中的至少一些互连结构尽可能靠近衬底边沿而在其间没有任何其他层。22.根据一个实施例,第一封装层和第二封装层以及第二封装层的顶部上的可选附加抗蚀剂层具有重合的结构边沿。第一封装层的整个表面由第二封装层和/或附加抗蚀剂层覆盖。然而,第二封装层可以被结构化为使得其叠加第一封装层的一些或全部结构边沿。23.第一封装层的结构边沿与互连结构之间可以保持安全距离。然而,第二封装层与互连结构之间几乎不需要或不需要保持安全边缘。24.以下,参考具体实施例和附图对晶片级封装进行更详细的解释。附图仅是示意性的并且可能不示出所有元件,只要这些省略的元件在本领域中已知,并且技术人员容易补充这些元件。而且,这些图并非按比例绘制,并且出于清楚的原因和更好的理解,一些细节可能被放大。25.图1以示意性横截面示出了根据第一实施例的晶片级封装,26.图2以示意性横截面示出了根据第二实施例的晶片级封装,27.图3以示意性横截面示出了根据第三实施例的晶片级封装,28.图4以示意性横截面示出了晶片级封装的更大描绘,29.图5示出了可以通过新晶片级封装胶封的滤波器器件的示意性框图,30.图6示出了新晶片级封装的示意性截面俯视图,31.图7示出了新晶片级封装的变体的示意性俯视图,32.图8示出了新晶片级封装的另一变体的示意性俯视图。33.图1以示意性横截面示出了根据第一实施例的晶片级封装。该封装仅被部分描绘并且通常示出了互连结构周围的区域。以下解释制造过程。34.封装被形成在包括功能材料或具有至少一个功能层作为顶部层的衬底su上。功能层包括对形成在其中或在其上的电子器件起作用的材料。功能材料是例如压电材料,并且该器件是微声学器件,例如,saw滤波器或baw器件。滤波器器件通过将器件结构ds(如图4所示)施加在衬底的顶部表面上或功能层上而形成。saw器件的器件结构包括叉指换能器、反射器和用于电接触器件的焊盘pd。baw器件的器件结构包括应用在功能层下方的顶部电极和底部电极。该图仅示出了连接到器件结构的焊盘。35.声学有源器件结构(该图中未示出)通常是机械的,并且也可以通过封装进行密封保护。施加在器件结构上方的第一封装层pl1在机械敏感器件结构上形成圆顶,该机械敏感器件结构位于示例声学有源器件结构。为此,例如由电介质形成的第一封装层的刚性足以在一定距离内自由跨越器件结构,从而形成圆顶并且在其下方保持空腔围合。sio2或sin是示例性的有用材料。选取第一封装层的厚度以为圆顶提供足够的稳定性并且取决于围合空腔的直径。空腔可以被预先形成在第一封装层中,或可以通过在沉积(多个)封装层之后必须被去除的牺牲材料结构来产生。36.然而,如mems器件或传感器之类的其他电子器件可以通过所提出的晶片级封装来封装。37.在被施加到整个表面之后,第一封装层被结构化为使得它至少围绕圆顶的周边搁置在衬底上并且密封到衬底上。进一步地,在对第一封装层进行结构化之后,焊盘pd的接触区域被暴露。38.在下一步骤中,第二封装层pl2例如以平面方式被沉积在第一封装层pl1上的整个表面上。在一个变体中,可以让衬底的边沿处的边缘未被覆盖。聚合物可以是光敏聚合物,如光致抗蚀剂用作增强第一封装层pl1所需的第二封装层pl2。聚合物可以作为箔或以液体或粘性形式而被应用。顶部表面在沉积之后可能已经是平坦的,并且平坦化不需要压力。39.在下一步骤中,第二封装层pl2通过去除需要暴露底层结构的层来结构化。在所描绘的实施例中,第二封装层的结构边沿在焊盘pd的边沿处叠加第一封装层的相应边沿。在朝向衬底su的边沿的外边沿处,第一封装层和第二封装层的结构边沿可以适形。本文中,在所描绘的示例中,第二封装层覆盖比第一封装层更大的区域。40.在焊盘pd的区域中,从两个封装层暴露的接触区域本文中完全由第二封装层pl2的周围边沿限定。41.然后,在下一步骤中,选择性地在暴露的接触区域上形成互连结构is。选择性金属沉积可以在化学金属沉积浴中以电流方式或无电流方式被执行。材料可以是cu。然而,由焊料形成互连也是可能的。42.互连结构is生长到比两个封装层pl1、pl2的组合高度hp高的高度hi。然后,封装作为一个整体可以例如通过互连结构is被容易地安装到pcb上。43.在互连结构是铜柱的情况下,焊料帽sc被施加在其顶部上。例如由ni形成的中间层可以被布置在焊料帽与cu柱之间。44.由于完全覆盖管芯,所以安全距离中的一些安全距离无需考虑间距。所使用的示例性距离采用的互连半径ri与封装距离dip的比例为1.4。在切割道区域中,互连结构is的半径与互连结构is的中心与切割道处最外层边沿之间的距离的比例目前约为2比3。对于所提出的晶片级封装,这两个比例可以减为一。45.整个有源管芯区域被第二封装层pl2的聚合物覆盖。在该区域内,可以自由放置互连。46.完全围合互连的可能性允许将互连放置得更为靠近敏感的有源结构,例如,靠近滤波器电路的谐振器。改进了热管理以及封装中器件的电气性能。而且,在两个封装层下方的嵌入增强了最终器件的机械稳定性,该最终器件是在切割通常形成在衬底晶片上的大面积封装之后的管芯。47.图2以示意性横截面示出了根据第二实施例的晶片级封装的特征。48.与图1所示的实施例相似,互连结构is本文中通过借助于第二封装层pl2的结构边沿在焊盘pd上限定接触区域来形成。然而,在靠近衬底的外边沿布置的焊盘处,第二封装层的结构边沿不完全围绕后面的接触区域。在其余周边上,焊盘的未覆盖边沿终止接触区域。因此,第一封装层或第二封装层没有完全包围和界定互连结构is。本文中,互连结构is的半径与互连结构is的中心与切割道处的最外层边沿之间的距离的比例仅为1,因此被最小化。49.当沉积或生长互连结构is时,该结构可能会生长在焊盘pd的暴露的外边沿上,该外边沿为图2中的右边沿。50.在晶片级封装中,可能同时存在不同互连。在焊盘位于封装的中心附近的情况下,这些焊盘通过根据图1所示的第一实施例的互连结构互连。位于衬底的边沿附近或稍后的切割道附近的焊盘通过根据如图2所示的第二实施例的互连结构互连。图2示出了在焊盘pd的左边沿处与第一封装层的边沿重叠的第二封装层。然而,两个封装层的边沿可能彼此适形。51.图3示出了如何根据现有技术形成接触区域和互连。本文中,仅在第二封装层pl2上施加附加封装层ar以加强第二封装层并且限定接触区域。当这样做时,必须把需要高容差的每个层形成步骤的叠加误差和过程偏差考虑在内,这些高容差扩大了所需的衬底区域。52.在图3的横截面中,示出了接触区域的两个不同边沿。在右侧上,第一封装层pl1的边沿位于焊盘上。本文中,附加封装层ar被施加在第一封装层pl1的进一步限制面积小于焊盘的接触区域的段上。在图的左侧上,接触区域同样由第一封装层的边沿和附加封装层的叠加段界定。第二封装层pl2的段被示为位于第一封装层与附加封装层之间,但不直接位于接触区域的边界处。在右侧上,示出的衬底的边沿符合切割道,带有单个电子器件的管芯沿着该切割道被单体化。53.图4示出了晶片级封装的更大横截面,该晶片级封装包括位于其中布置有器件结构ds的第一封装层pl1下的空腔cv。所描绘的互连结构is例如根据图1所示的第一实施例而被形成。54.与加强封装并且还提供平坦表面的第二封装层pl2相比较,第一封装层pl1相对较薄。第一封装层或第二封装层的结构边沿可以用于界定接触区域并且限定互连结构的区域。梯子部形成为铜柱,并且该梯子的顶部覆盖有焊料帽sc。55.图5示出了可以与所提出的封装一起封装的示例性滤波器电路的框图。该滤波器电路包括若干个(例如,四个)串联谐振器rs,这些串联谐振器rs被布置在输入端子与输出端子之间的串联信号线ssl中。每两个相邻的串联谐振器之间的相应节点经由并联支路被连接到接地,在该并联支路中,可以布置并联谐振器rp或另一阻抗元件。可以在并联谐振器与接地之间连接电感(未示出)。一对串联谐振器rs和并联谐振器rp或阻抗元件一起形成滤波器电路的基本段bs。还可以存在从电感、电容或其他无源元件中选取的其他串联元件。滤波器电路可以具有或多或少的基本段,这取决于滤波器的期望选择性。更多的基本段可被用于进一步调谐滤波器功能。56.谐振器可以体现为saw谐振器。然而,baw谐振器和gbaw谐振器也可以与所提出的封装一起被封装。57.图6是新晶片级封装上的示意性截面俯视图,以示出封装层pl在衬底su上的延伸。可以看出,互连结构is可以被任意放置在芯片/衬底su上正好需要例如沿着边沿接触有源器件结构的地方。所有互连结构由第二封装层pl2中的相应切口限定,使得每个切口完全被封装层的剩余区域包围。例如,这些互连对应于图1所示的互连。本文中,第二封装层pl2没有完全覆盖衬底su,而是使其边缘暴露。58.图7是新晶片级封装的相似示意性截面俯视图。本文中,互连结构的两个不同位置并行存在。中心互连isc如图6所示体现。其他互连结构ise直接位于封装层的边沿上,使得边沿与接触区域和形成在其上的互连相交。该实施例具有的优点如下:互连可以被放置在更为靠近衬底su或管芯的边沿,并且节省管芯上的空间。59.在图6和图7所示的两种情况下,封装层epl的边沿没有延伸到管芯或衬底su的边沿,但保持衬底的安全边缘未被覆盖。60.图8与图7相似,唯一区别在于,第二封装层pl完全覆盖衬底su。因此,边沿epl2与衬底的边沿适形。由于没有边缘,所以可以节省衬底上的表面区域,而不会违背用于实现高产量和可靠部件的安全要求。61.本发明已经关于一些实施例和附图进行了解释,但可能不限于根据实施例的特征的精确组合。已被描述为向晶片级封装提供优点的任何特征都应被视为独立于其他附带特征,这些附带特征在共同附图上进行描绘或在同一实施例中一起进行描述。62.所使用的术语和附图标记列表63.ar附加抗蚀剂封装层bs梯形滤波器电路的基本段ca由每个焊盘的部分区域形成的接触区域cv空腔die互连的中心与衬底的边沿之间的芯片距离dip互连的中心与封装层边沿之间的距离ds电气器件结构fl功能层hi衬底上互连结构的高度hp衬底上封装层的高度is互连结构pl1第一封装层pl2第二封装层ri互连半径rp并联谐振器rs串联谐振器ssl串联信号线su衬底

本文地址:https://www.jishuxx.com/zhuanli/20240726/123344.html

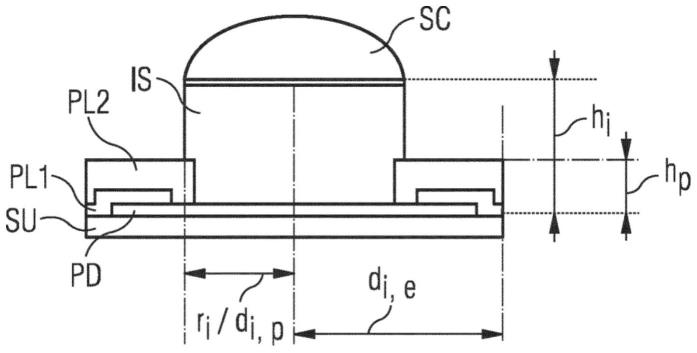

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。