MEMS器件的制造方法与流程

- 国知局

- 2024-07-27 12:49:51

mems器件的制造方法技术领域1.本发明涉及半导体技术领域,特别涉及一种mems器件的制造方法。背景技术:2.基于mems(micro-electro-mechanical system,微机电系统)技术制作的mems器件,由于其具有结构简单、与微电子制作工艺兼容性好、可大批量制造、体积小等优点而受到广泛关注。mems器件中通常包括梳齿结构,用以实现驱动等功能。3.现有技术所形成的mems器件中,梳齿结构的精度较低,从而影响整个mems器件的功能和可靠性。技术实现要素:4.本发明的目的在于提供一种mems器件的制造方法,以解决现有技术中mems器件中梳齿结构的精度较低的问题。5.为了解决上述技术问题,本发明提供了一种mems器件的制造方法,所述mems器件的制造方法包括:6.提供半导体基底,对所述半导体基底执行p型离子注入工艺,以在所述半导体基底中形成p型注入区;7.形成图形化的掩膜层,所述图形化的掩膜层覆盖所述p型注入区和所述半导体基底;8.利用所述图形化的掩膜层对所述p型注入区和所述p型注入区底部的所述半导体基底执行刻蚀工艺,以在所述半导体基底中形成梳齿结构;以及,9.去除所述图形化的掩膜层以及所述p型注入区,以在所述半导体基底中形成凹槽;10.其中,在去除所述p型注入区之前,对所述p型注入区执行疏松处理,以使得所述p型注入区中形成多孔。11.可选的,在所述的mems器件的制造方法中,在形成图形化的掩膜层之前,对所述p型注入区执行疏松处理;或者,在去除所述图形化的掩膜层之后,去除所述p型注入区之前,对所述p型注入区执行疏松处理。12.可选的,在所述的mems器件的制造方法中,在形成图形化的掩膜层之前,对所述p型注入区执行疏松处理,并且,在对所述p型注入区执行疏松处理之前,所述mems器件的制造方法还包括:在所述p型注入区上形成网格结构;其中,执行所述疏松处理时,所述p型注入区中较所述网格结构中易于形成多孔。13.可选的,在所述的mems器件的制造方法中,在所述p型注入区上形成网格结构包括:对所述p型注入区执行n型离子注入工艺,以在所述p型注入区上形成所述网格结构。14.可选的,在所述的mems器件的制造方法中,所述n型离子注入工艺的掺杂浓度大于1×1016cm-3。15.可选的,在所述的mems器件的制造方法中,在所述p型注入区上形成网格结构包括:16.形成氮化硅层,所述氮化硅层覆盖所述p型注入区和所述半导体基底;以及,17.对所述氮化硅层执行刻蚀工艺,以形成所述网格结构。18.可选的,在所述的mems器件的制造方法中,所述氮化硅层的厚度为19.可选的,在所述的mems器件的制造方法中,对所述p型注入区执行疏松处理包括:在hf溶液中,对所述p型注入区施加正压以执行所述疏松处理。20.可选的,在所述的mems器件的制造方法中,形成图形化的掩膜层包括:21.形成硬掩膜层,所述硬掩膜层覆盖所述p型注入区和所述半导体基底;22.形成光阻层,所述光阻层覆盖所述硬掩膜层;23.对所述光阻层执行曝光和显影工艺,以形成图形化的光阻层;以及,24.利用所述图形化的光阻层对所述硬掩膜层执行刻蚀工艺,以形成图形化的硬掩膜层,所述图形化的掩膜层包括所述图形化的硬掩膜层和所述图形化的光阻层。25.可选的,在所述的mems器件的制造方法中,所述硬掩膜层的厚度为可选的,在所述的mems器件的制造方法中,所述硬掩膜层的厚度为所述光阻层的厚度为500nm~2μm。26.可选的,在所述的mems器件的制造方法中,利用所述图形化的掩膜层对所述p型注入区和所述p型注入区底部的所述半导体基底执行刻蚀工艺包括:利用所述图形化的掩膜层对所述p型注入区和所述p型注入区底部的所述半导体基底执行干法刻蚀工艺。27.可选的,在所述的mems器件的制造方法中,去除所述图形化的掩膜层以及所述p型注入区包括:通过剥离工艺去除所述图形化的掩膜层以及通过湿法腐蚀工艺去除所述p型注入区。28.可选的,在所述的mems器件的制造方法中,提供半导体基底包括:29.提供第一半导体基底,所述第一半导体基底中形成有空腔;以及,30.在所述第一半导体基底上键合第二半导体基底,所述半导体基底包括所述第一半导体基底和所述第二半导体基底。31.发明人研究发现,造成现有技术中mems器件中梳齿结构的精度较低的一个主要原因在于,现有技术中,梳齿结构的形成过程主要包括:在半导体基底中形成凹槽;形成光阻层以覆盖所述半导体基底表面和所述凹槽,并对所述光阻层执行曝光和显影工艺以形成图形化的光阻层;利用所述图形化的光阻层刻蚀所述凹槽底部的半导体基底以形成梳齿结构,其中,凹槽的深度通常介于2μm~3μm。由于所述凹槽的存在,所述光阻层形成在不平整的表面上,从而对所述光阻层执行曝光和显影工艺以形成图形化的光阻层过程中,将降低曝光和显影的精度,使得所述图形化的光阻层的精度较差,相应的,使得现有技术中mems器件中梳齿结构的精度较低。32.基此,在本发明提供的mems器件的制造方法中,在半导体基底中形成p型注入区,对所述p型注入区执行疏松处理,以使得所述p型注入区中形成多孔,从而便于后续去除所述p型注入区。由此,在刻蚀形成梳齿结构的过程中,所采用的图形化的掩膜层可以形成在平整的表面,相应的提高了图形化的掩膜层的精度以及由此刻蚀而成的梳齿结构的精度,同时,由于对所述p型注入区执行了疏松处理以使得所述p型注入区中形成多孔,也能够方便地去除所述p型注入区而形成凹槽。附图说明33.图1是本发明实施例一的mems器件的制造方法的流程示意图。34.图2是本发明实施例一的mems器件的制造方法之提供半导体基底的器件剖面示意图。35.图3是本发明实施例一的mems器件的制造方法之形成p型注入区的器件剖面示意图。36.图4是本发明实施例一的mems器件的制造方法之对p型注入区执行疏松处理的器件剖面示意图。37.图5是本发明实施例一的mems器件的制造方法之形成图形化的掩膜层的器件剖面示意图。38.图6是本发明实施例一的mems器件的制造方法之形成梳齿结构的器件剖面示意图。39.图7是本发明实施例一的mems器件的制造方法之去除图形化的掩膜层以及p型注入区的器件剖面示意图。40.图8是本发明实施例二的mems器件的制造方法的流程示意图。41.图9是本发明实施例二的mems器件的制造方法之提供半导体基底的器件剖面示意图。42.图10是本发明实施例二的mems器件的制造方法之形成p型注入区的器件剖面示意图。43.图11是本发明实施例二的mems器件的制造方法之形成网格结构的器件剖面示意图。44.图12是本发明实施例二的mems器件的制造方法之对p型注入区执行疏松处理的器件剖面示意图。45.图13是本发明实施例二的mems器件的制造方法之形成图形化的掩膜层的器件剖面示意图。46.图14是本发明实施例二的mems器件的制造方法之形成梳齿结构的器件剖面示意图。47.图15是本发明实施例二的mems器件的制造方法之去除图形化的掩膜层以及p型注入区的器件剖面示意图。48.图16是本发明实施例三的mems器件的制造方法的流程示意图。49.图17是本发明实施例三的mems器件的制造方法之提供半导体基底的器件剖面示意图。50.图18是本发明实施例三的mems器件的制造方法之形成p型注入区的器件剖面示意图。51.图19是本发明实施例三的mems器件的制造方法之形成图形化的掩膜层的器件剖面示意图。52.图20是本发明实施例三的mems器件的制造方法之形成梳齿结构的器件剖面示意图。53.图21是本发明实施例三的mems器件的制造方法之去除图形化的掩膜层的器件剖面示意图。54.图22是本发明实施例三的mems器件的制造方法之对p型注入区执行疏松处理的器件剖面示意图。55.图23是本发明实施例三的mems器件的制造方法之去除p型注入区的器件剖面示意图。56.其中,附图标记说明如下:57.100-半导体基底;101-第一半导体基底;1010-空腔;102-第二半导体基底;110-p型注入区;111-多孔;120-图形化的掩膜层;121-图形化的光阻层;122-图形化的硬掩膜层;130-梳齿结构;140-凹槽;150-凸台结构。58.200-半导体基底;201-第一半导体基底;2010-空腔;202-第二半导体基底;210-p型注入区;211-多孔;212-网格结构;220-图形化的掩膜层;221-图形化的光阻层;222-图形化的硬掩膜层;230-梳齿结构;240-凹槽;250-凸台结构。59.300-半导体基底;301-第一半导体基底;3010-空腔;302-第二半导体基底;310-p型注入区;311-多孔;320-图形化的掩膜层;321-图形化的光阻层;322-图形化的硬掩膜层;330-梳齿结构;340-凹槽;350-凸台结构。具体实施方式60.以下结合附图和具体实施例对本发明提出的mems器件的制造方法作进一步详细说明。根据下面说明和权利要求书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。61.本发明使用的术语仅仅是出于描述特定实施方式的目的,而非旨在限制本发明。除非本技术文件中另作定义,本发明使用的技术术语或者科学术语应当为本发明所属领域内具有一般技能的人士所理解的通常意义。本发明说明书以及权利要求书中使用的“第一”、“第二”以及类似的词语并不表示任何顺序、数量或者重要性,而只是用来区分不同的组成部分。同样,“一个”或者“一”等类似词语也不表示数量限制,而是表示存在至少一个。“多个”或者“若干”表示两个及两个以上。除非另行指出,“前部”、“后部”、“下部”和/或“上部”等类似词语只是为了便于说明,而并非限于一个位置或者一种空间定向。“包括”或者“包含”等类似词语意指出现在“包括”或者“包含”前面的元件或者物件涵盖出现在“包括”或者“包含”后面列举的元件或者物件及其等同,并不排除其他元件或者物件。“连接”或者“相连”等类似的词语并非限定于物理的或者机械的连接,而且可以包括电性的连接,不管是直接的还是间接的。在本发明说明书和所附权利要求书中所使用的单数形式的“一种”、“所述”和“该”也旨在包括多数形式,除非上下文清楚地表示其他含义。还应当理解,本文中使用的术语“和/或”是指并包含一个或多个相关联的列出项目的任何或所有可能组合。62.现有技术所形成的mems器件中,梳齿结构的精度较低,从而影响整个mems器件的功能和可靠性。发明人作了深入的研究,发现造成现有技术中mems器件中梳齿结构的精度较低的一个主要原因在于,现有技术中,梳齿结构的形成过程主要包括:在半导体基底中形成凹槽;形成光阻层以覆盖所述半导体基底表面和所述凹槽,并对所述光阻层执行曝光和显影工艺以形成图形化的光阻层;利用所述图形化的光阻层刻蚀所述凹槽底部的半导体基底以形成梳齿结构,其中,凹槽的深度通常介于2μm~3μm。由于所述凹槽的存在,所述光阻层形成在不平整的表面上,从而对所述光阻层执行曝光和显影工艺以形成图形化的光阻层过程中,将降低曝光和显影的精度,使得所述图形化的光阻层的精度较差,相应的,使得现有技术中mems器件中梳齿结构的精度较低。63.此外,发明人发现,现有技术中在刻蚀形成梳齿结构的过程中,所采用的光阻层的厚度比较大,通常需要4μm~5μm,这样大的厚度也一定程度上造成了对所述光阻层执行曝光和显影工艺以形成图形化的光阻层的工艺精度,相应的,降低了所形成的梳齿结构的精度。64.基此,本发明的核心思想提供一种mems器件的制造方法,在半导体基底中形成p型注入区,对所述p型注入区执行疏松处理,以使得所述p型注入区中形成多孔,从而便于后续去除所述p型注入区。由此,在刻蚀形成梳齿结构的过程中,所采用的图形化的掩膜层可以形成在平整的表面,相应的提高了图形化的掩膜层的精度以及由此刻蚀而成的梳齿结构的精度,同时,由于对所述p型注入区执行了疏松处理以使得所述p型注入区中形成多孔,也能够方便地去除所述p型注入区而形成凹槽。65.进一步的,所采用的图形化的掩膜层包括图形化的硬掩膜层和图形化的光阻层,优选的,所述硬掩膜层的厚度为所述光阻层的厚度为500nm~2μm。在此,采用硬掩膜层和光阻层的双层结构,可以减少光阻层的使用,降低光阻层的厚度,并且,还降低了所采用的图形化的掩膜层的整体厚度,从而可以进一步提高所形成的图形化的掩膜层的精度以及由此刻蚀而成的梳齿结构的精度。66.接下去将结合图1至图23以及如下三个实施例对本发明提出的mems器件的制造方法作进一步详细说明。67.【实施例一】68.请参考图1至图7,其中,图1是本发明实施例一的mems器件的制造方法的流程示意图,图2至图7是本发明实施例一的mems器件的制造方法的器件剖面示意图。69.如图1所示,在本实施例一中,所述mems器件的制造方法具体包括如下步骤:70.步骤s10:提供半导体基底,对所述半导体基底执行p型离子注入工艺,以在所述半导体基底中形成p型注入区;71.步骤s11:对所述p型注入区执行疏松处理,以使得所述p型注入区中形成多孔;72.步骤s12:形成图形化的掩膜层,所述图形化的掩膜层覆盖所述p型注入区和所述半导体基底;73.步骤s13:利用所述图形化的掩膜层对所述p型注入区和所述p型注入区底部的所述半导体基底执行刻蚀工艺,以在所述半导体基底中形成梳齿结构;以及,74.步骤s14:去除所述图形化的掩膜层以及所述p型注入区,以在所述半导体基底中形成凹槽。75.请参考图2,提供半导体基底100。在本技术实施例中,具体包括:提供第一半导体基底101,所述第一半导体基底101中形成有空腔1010,所述第一半导体基底101的材质例如为硅;在所述第一半导体基底101上键合第二半导体基底102。所述第二半导体基底102的材质例如为硅,进一步的,所述第二半导体基底102的材质可以是未经掺杂的多晶硅或者经过n型掺杂的多晶硅。所述半导体基底100包括所述第一半导体基底101和所述第二半导体基底102。76.接着,请参考图3,对所述半导体基底100执行p型离子注入工艺,以在所述半导体基底100中形成p型注入区110。在此,具体对所述第二半导体基底102执行p型离子注入工艺,以在所述第二半导体基底102中形成p型注入区110,所述p型注入区110自所述第二半导体基底102的表面延伸至所述第二半导体基底102中。77.进一步的,所述p型注入区110对准所述空腔1010。如图3所示,图示中示出了两个空腔1010以及两个p型注入区110,其中,两个所述p型注入区110分别对准两个所述空腔1010。在此,各所述p型注入区110分别位于对应的所述空腔1010的正上方。78.请参考图4,在本技术实施例中,接着,对所述p型注入区110执行疏松处理,以使得所述p型注入区110中形成多孔111。由于对所述p型注入区110执行了疏松处理,由此后续去除所述p型注入区110以形成凹槽时,能够非常方便、高效地实现,也保证了所形成的凹槽的质量。在此,在所述p型注入区110中形成多个孔洞,也即变成多孔硅,从而使得所述p型注入区110变得疏松。较佳的,所述多孔111在所述p型注入区110中的体积占比大于50%。具体的,可以将所述半导体基底100置于hf(氢氟酸)溶液中,并对所述p型注入区110施加正压,所施加的正压例如为0.1v~10v,从而在所述p型注入区110中形成多孔111。79.接着,如图5所示,形成图形化的掩膜层120,所述图形化的掩膜层120覆盖所述p型注入区110和所述半导体基底100。在此,先形成掩膜层(图5中未示出),接着对掩膜层执行光刻和刻蚀工艺,从而形成所述图形化的掩膜层120。在本技术实施例中,所述半导体基底100中尚未形成凹槽,其表面平坦,相应的,所述掩膜层形成在平坦的表面上,可以得到膜厚均匀的掩膜层,从而对所述掩膜层执行光刻和刻蚀工艺时,能够形成高精度、高可靠性的图形化的掩膜层120,从而提高了由此刻蚀而成的梳齿结构的精度。80.在本技术实施例中,所述图形化的掩膜层120为双层结构,包括图形化的硬掩膜层和图形化的光阻层。在此,采用硬掩膜层和光阻层的双层结构,可以减少光阻层的使用,降低光阻层的厚度,并且,还降低了所采用的图形化的掩膜层的整体厚度,从而可以进一步提高所形成的图形化的掩膜层的精度以及由此刻蚀而成的梳齿结构的精度。81.具体的,形成所述图形化的掩膜层120包括:形成硬掩膜层(图5中未示出),所述硬掩膜层覆盖所述p型注入区110和所述半导体基底100;形成光阻层(图5中未示出),所述光阻层覆盖所述硬掩膜层;对所述光阻层执行曝光和显影工艺,以形成图形化的光阻层121;以及,利用所述图形化的光阻层121对所述硬掩膜层执行刻蚀工艺,以形成图形化的硬掩膜层122。其中,所述硬掩膜层的材质例如可以为正硅酸乙酯(teos)等。优选的,所述硬掩膜层的厚度为所述光阻层的厚度为500nm~2μm。82.接着,如图6所示,利用所述图形化的掩膜层120对所述p型注入区110和所述p型注入区110底部的所述半导体基底100执行刻蚀工艺,以在所述半导体基底100中形成梳齿结构130。具体的,以所述图形化的掩膜层120为掩膜,对所述p型注入区110执行干法刻蚀工艺,并延伸刻蚀所述第二半导体基底102至贯穿所述第二半导体基底102,从而形成梳齿结构130。所述梳齿结构130对准所述空腔1010,如图6所示,两个所述梳齿结构130分别对准两个所述空腔1010。在本技术实施例中,提高了所形成的图形化的掩膜层120的精度与可靠性,相应的,提高了由此所形成的梳齿结构130的精度与可靠性。83.进一步的,请参考图7,去除所述图形化的掩膜层120以及所述p型注入区110。具体的,可以通过剥离工艺去除所述图形化的掩膜层120以暴露出所述p型注入区110和所述半导体基底100。更进一步的,可以通过剥离工艺和/或干法刻蚀工艺去除所述图形化的光阻层121以及所述图形化的硬掩膜层122。在本技术实施例中,通过湿法腐蚀工艺去除所述p型注入区110以在所述半导体基底100中形成凹槽140并暴露出所述梳齿结构130。即在本技术实施例中,所述梳齿结构130的表面低于所述半导体基底100的表面,所述梳齿结构130两侧形成了凸台结构150,由此可以提高所形成的mems器件的性能,例如提高其驱动性能等。84.具体的,可以采用dhf(稀释的氢氟酸)溶液对所述p型注入区110执行湿法腐蚀工艺。例如,可以采用质量百分比浓度为49%的氢氟酸(hf)和质量百分比浓度为30%的双氧水(h2o2)的混合溶液,其中,氢氟酸和双氧水的比例例如为1:5;或者,可以采用质量百分比浓度为49%的氢氟酸(hf)、质量百分比浓度为70%的硝酸(hno3)和乙酸(ch3cooh)的混合溶液,其中,氢氟酸、硝酸和乙酸的比例例如为3:16:1。所述dhf溶液对于所述p型注入区110和所述半导体基底100具有很高的刻蚀选择比,从而能够高效、可靠地去除所述p型注入区110。特别的,本技术实施例在前述工艺步骤中,对所述p型注入区110执行了疏松处理,以使得所述p型注入区110中形成多孔111,由此在本步骤中对所述p型注入区110执行湿法腐蚀工艺时,能够高效、可靠地去除所述p型注入区110,并使得所形成的凹槽形貌佳。85.【实施例二】86.请参考图8至图15,其中,图8是本发明实施例二的mems器件的制造方法的流程示意图,图9至图15是本发明实施例二的mems器件的制造方法的器件剖面示意图。87.如图8所示,在本实施例二中,所述mems器件的制造方法具体包括如下步骤:88.步骤s20:提供半导体基底,对所述半导体基底执行p型离子注入工艺,以在所述半导体基底中形成p型注入区;89.步骤s21:在所述p型注入区上形成网格结构;90.步骤s22:对所述p型注入区执行疏松处理,以使得所述p型注入区中形成多孔;91.步骤s23:形成图形化的掩膜层,所述图形化的掩膜层覆盖所述p型注入区和所述半导体基底;92.步骤s24:利用所述图形化的掩膜层对所述p型注入区和所述p型注入区底部的所述半导体基底执行刻蚀工艺,以在所述半导体基底中形成梳齿结构;以及,93.步骤s25:去除所述图形化的掩膜层、所述网格结构以及所述p型注入区,以在所述半导体基底中形成凹槽。94.请参考图9,提供半导体基底200。在本技术实施例中,具体包括:提供第一半导体基底201,所述第一半导体基底201中形成有空腔2010,所述第一半导体基底201的材质例如为硅;在所述第一半导体基底201上键合第二半导体基底202。所述第二半导体基底202的材质例如为硅,进一步的,所述第二半导体基底202的材质可以是未经掺杂的多晶硅或者经过n型掺杂的多晶硅。所述半导体基底200包括所述第一半导体基底201和所述第二半导体基底202。95.接着,请参考图10,对所述半导体基底200执行p型离子注入工艺,以在所述半导体基底200中形成p型注入区210。在此,具体对所述第二半导体基底202执行p型离子注入工艺,以在所述第二半导体基底202中形成p型注入区210,所述p型注入区210自所述第二半导体基底202的表面延伸至所述第二半导体基底202中。96.进一步的,所述p型注入区210对准所述空腔2010。如图10所示,图示中示出了两个空腔2010以及两个p型注入区210,其中,两个所述p型注入区210分别对准两个所述空腔2010。在此,各所述p型注入区210分别位于对应的所述空腔2010的正上方。97.请参考图11,在本技术实施例中,接着,在所述p型注入区210上形成网格结构212,其中,后续执行疏松处理时,所述p型注入区210中较所述网格结构212中易于形成多孔,即,后续经过疏松处理后,所述p型注入区210较所述网格结构212疏松。在本技术实施例中,后续所形成的图形化的掩膜层位于所述网格结构212之上,由此,通过所述网格结构212可以支撑所述图形化的掩膜层,保护经过疏松处理的所述p型注入区210,由此,也进一步提高了工艺质量与可靠性,并进而提高了所形成的mems器件的质量与可靠性。98.在本技术的一个实施例中,在所述p型注入区210上形成网格结构包括:对所述p型注入区210执行n型离子注入工艺,以在所述p型注入区210上形成所述网格结构212。例如,分别在所述p型注入区210的第一方向和第二方向执行n型离子注入工艺,所述第一方向和所述第二方向相交,以在所述第一方向形成第一数量个n型注入条,在所述第二方向形成第二数量个n型注入条,第一方向的n型注入条和第二方向的n型注入条相交叉,从而形成所述网格结构212。优选的,所述n型离子注入工艺的掺杂浓度大于1×1016cm-3,更优的所述n型离子注入工艺的掺杂浓度介于1×1016cm-3~1×1018cm-3之间。99.在本技术的另一个实施例中,在所述p型注入区210上形成网格结构包括:形成氮化硅层(图11中未示出),所述氮化硅层覆盖所述p型注入区210和所述半导体基底200;以及,对所述氮化硅层执行刻蚀工艺,以形成所述网格结构212。优选的,所述氮化硅层的厚度为100.请参考图12,在本技术实施例中,接着,对所述p型注入区210执行疏松处理,以使得所述p型注入区210中形成多孔211。由于对所述p型注入区210执行了疏松处理,由此后续去除所述p型注入区210以形成凹槽时,能够非常方便、高效地实现,也保证了所形成的凹槽的质量。在此,指在所述p型注入区210中形成多个孔洞,也即变成多孔硅,从而使得所述p型注入区210变得疏松。较佳的,所述多孔211在所述p型注入区210中的体积占比大于50%。具体的,可以将所述半导体基底200置于hf(氢氟酸)溶液中,并对所述p型注入区210施加正压,所施加的正压例如为0.1v~10v,从而在所述p型注入区210中形成多孔211。在本技术实施例中,所述网格结构212没有疏松化或者疏松化程度小于所述p型注入区210,即执行疏松处理时,所述网格结构212中没有对应形成多孔或者形成的多孔少于所述p型注入区210。101.接着,如图13所示,形成图形化的掩膜层220,所述图形化的掩膜层220覆盖所述网格结构212、所述p型注入区210和所述半导体基底200。在此,先形成掩膜层(图13中未示出),接着对掩膜层执行光刻和刻蚀工艺,从而形成所述图形化的掩膜层220。在本技术实施例中,所述半导体基底200中尚未形成凹槽,其表面平坦,相应的,所述掩膜层形成在平坦的表面上,可以得到膜厚均匀的掩膜层,从而对所述掩膜层执行光刻和刻蚀工艺时,能够形成高精度、高可靠性的图形化的掩膜层220,从而提高了由此刻蚀而成的梳齿结构的精度。102.在本技术实施例中,所述图形化的掩膜层220为双层结构,包括图形化的硬掩膜层和图形化的光阻层。在此,采用硬掩膜层和光阻层的双层结构,可以减少光阻层的使用,降低光阻层的厚度,并且,还降低了所采用的图形化的掩膜层的整体厚度,从而可以进一步提高所形成的图形化的掩膜层的精度以及由此刻蚀而成的梳齿结构的精度。103.具体的,形成所述图形化的掩膜层220包括:形成硬掩膜层(图13中未示出),所述硬掩膜层覆盖所述网格结构212、所述p型注入区210和所述半导体基底200;形成光阻层(图13中未示出),所述光阻层覆盖所述硬掩膜层;对所述光阻层执行曝光和显影工艺,以形成图形化的光阻层221;以及,利用所述图形化的光阻层221对所述硬掩膜层执行刻蚀工艺,以形成图形化的硬掩膜层222。其中,所述硬掩膜层的材质例如可以为正硅酸乙酯(teos)等。优选的,所述硬掩膜层的厚度为所述光阻层的厚度为500nm~2μm。104.接着,如图14所示,利用所述图形化的掩膜层220对所述网格结构212、所述p型注入区210和所述p型注入区210底部的所述半导体基底200执行刻蚀工艺,以在所述半导体基底200中形成梳齿结构230。具体的,以所述图形化的掩膜层220为掩膜,对所述网格结构212、所述p型注入区210执行干法刻蚀工艺,并延伸刻蚀所述第二半导体基底202至贯穿所述第二半导体基底202,从而形成梳齿结构230。所述梳齿结构230对准所述空腔2010,如图14所示,两个所述梳齿结构230分别对准两个所述空腔2010。在本技术实施例中,提高了所形成的图形化的掩膜层220的精度与可靠性,相应的,提高了由此所形成的梳齿结构230的精度与可靠性。105.进一步的,请参考图15,去除所述图形化的掩膜层220、所述网格结构212以及所述p型注入区210。具体的,可以通过剥离工艺去除所述图形化的掩膜层220以暴露出所述网格结构212、所述p型注入区210和所述半导体基底200。更进一步的,可以通过剥离工艺和/或干法刻蚀工艺去除所述图形化的光阻层221以及所述图形化的硬掩膜层222,在此,可同时通过所述干法刻蚀工艺去除所述网格结构212。在本技术实施例中,通过湿法腐蚀工艺去除所述p型注入区210以在所述半导体基底200中形成凹槽240并暴露出所述梳齿结构230。即在本技术实施例中,所述梳齿结构230的表面低于所述半导体基底200的表面,所述梳齿结构230两侧形成了凸台结构250,由此可以提高所形成的mems器件的性能,例如提高其驱动性能等。106.具体的,可以采用dhf(稀释的氢氟酸)溶液对所述p型注入区210执行湿法腐蚀工艺。例如,可以采用质量百分比浓度为49%的氢氟酸(hf)和质量百分比浓度为30%的双氧水(h2o2)的混合溶液,其中,氢氟酸和双氧水的比例例如为1:5;或者,可以采用质量百分比浓度为49%的氢氟酸(hf)、质量百分比浓度为70%的硝酸(hno3)和乙酸(ch3cooh)的混合溶液,其中,氢氟酸、硝酸和乙酸的比例例如为3:16:1。所述dhf溶液对于所述p型注入区210和所述半导体基底200具有很高的刻蚀选择比,从而能够高效、可靠地去除所述p型注入区210。特别的,本技术实施例在前述工艺步骤中,对所述p型注入区210执行了疏松处理,以使得所述p型注入区210中形成多孔211,由此在本步骤中对所述p型注入区210执行湿法腐蚀工艺时,能够高效、可靠地去除所述p型注入区210,并使得所形成的凹槽形貌佳。107.【实施例三】108.请参考图16至图23,其中,图16是本发明实施例三的mems器件的制造方法的流程示意图,图17至图23是本发明实施例三的mems器件的制造方法的器件剖面示意图。109.如图16所示,在本实施例三中,所述mems器件的制造方法具体包括如下步骤:110.步骤s30:提供半导体基底,对所述半导体基底执行p型离子注入工艺,以在所述半导体基底中形成p型注入区;111.步骤s31:形成图形化的掩膜层,所述图形化的掩膜层覆盖所述p型注入区和所述半导体基底;112.步骤s32:利用所述图形化的掩膜层对所述p型注入区和所述p型注入区底部的所述半导体基底执行刻蚀工艺,以在所述半导体基底中形成梳齿结构;113.步骤s33:去除所述图形化的掩膜层;114.步骤s34:对所述p型注入区执行疏松处理,以使得所述p型注入区中形成多孔;以及,115.步骤s35:去除所述p型注入区,以在所述半导体基底中形成凹槽。116.请参考图17,提供半导体基底300。在本技术实施例中,具体包括:提供第一半导体基底301,所述第一半导体基底301中形成有空腔3010,所述第一半导体基底301的材质例如为硅;在所述第一半导体基底301上键合第二半导体基底302。所述第二半导体基底302的材质例如为硅,进一步的,所述第二半导体基底302的材质可以是未经掺杂的多晶硅或者经过n型掺杂的多晶硅。所述半导体基底300包括所述第一半导体基底301和所述第二半导体基底302。117.接着,请参考图18,对所述半导体基底300执行p型离子注入工艺,以在所述半导体基底300中形成p型注入区310。在此,具体对所述第二半导体基底302执行p型离子注入工艺,以在所述第二半导体基底302中形成p型注入区310,所述p型注入区310自所述第二半导体基底302的表面延伸至所述第二半导体基底302中。118.进一步的,所述p型注入区310对准所述空腔3010。如图18所示,图示中示出了两个空腔3010以及两个p型注入区310,其中,两个所述p型注入区310分别对准两个所述空腔3010。在此,各所述p型注入区310分别位于对应的所述空腔3010的正上方。119.接着,如图19所示,形成图形化的掩膜层320,所述图形化的掩膜层320覆盖所述p型注入区310和所述半导体基底300。在此,先形成掩膜层(图19中未示出),接着对掩膜层执行光刻和刻蚀工艺,从而形成所述图形化的掩膜层320。在本技术实施例中,所述半导体基底300中尚未形成凹槽,其表面平坦,相应的,所述掩膜层形成在平坦的表面上,可以得到膜厚均匀的掩膜层,从而对所述掩膜层执行光刻和刻蚀工艺时,能够形成高精度、高可靠性的图形化的掩膜层320,从而提高了由此刻蚀而成的梳齿结构的精度。120.在本技术实施例中,所述图形化的掩膜层320为双层结构,包括图形化的硬掩膜层和图形化的光阻层。在此,采用硬掩膜层和光阻层的双层结构,可以减少光阻层的使用,降低光阻层的厚度,并且,还降低了所采用的图形化的掩膜层的整体厚度,从而可以进一步提高所形成的图形化的掩膜层的精度以及由此刻蚀而成的梳齿结构的精度。121.具体的,形成所述图形化的掩膜层320包括:形成硬掩膜层(图19中未示出),所述硬掩膜层覆盖所述p型注入区310和所述半导体基底300;形成光阻层(图19中未示出),所述光阻层覆盖所述硬掩膜层;对所述光阻层执行曝光和显影工艺,以形成图形化的光阻层321;以及,利用所述图形化的光阻层321对所述硬掩膜层执行刻蚀工艺,以形成图形化的硬掩膜层322。其中,所述硬掩膜层的材质例如可以为正硅酸乙酯(teos)等。优选的,所述硬掩膜层的厚度为所述光阻层的厚度为500nm~2μm。122.接着,如图20所示,利用所述图形化的掩膜层320对所述p型注入区310和所述p型注入区310底部的所述半导体基底300执行刻蚀工艺,以在所述半导体基底300中形成梳齿结构330。具体的,以所述图形化的掩膜层320为掩膜,对所述p型注入区310执行干法刻蚀工艺,并延伸刻蚀所述第二半导体基底302至贯穿所述第二半导体基底302,从而形成梳齿结构330。所述梳齿结构330对准所述空腔3010,如图20所示,两个所述梳齿结构330分别对准两个所述空腔3010。在本技术实施例中,提高了所形成的图形化的掩膜层320的精度与可靠性,相应的,提高了由此所形成的梳齿结构330的精度与可靠性。123.进一步的,请参考图21,去除所述图形化的掩膜层320,暴露出所述p型注入区310以及所述半导体基底300。具体的,可以通过剥离工艺去除所述图形化的掩膜层320以暴露出所述p型注入区310和所述半导体基底300。更进一步的,可以通过剥离工艺和/或干法刻蚀工艺去除所述图形化的光阻层321以及所述图形化的硬掩膜层322。124.请参考图22,在本技术实施例中,接着,对所述p型注入区310执行疏松处理,以使得所述p型注入区310中形成多孔311。由于对所述p型注入区310执行了疏松处理,由此接下去去除所述p型注入区310以形成凹槽时,能够非常方便、高效地实现,也保证了所形成的凹槽的质量。在此,指在所述p型注入区310中形成多个孔洞,也即变成多孔硅,从而使得所述p型注入区310变得疏松。较佳的,所述多孔311在所述p型注入区310中的体积占比大于50%。具体的,可以将所述半导体基底300置于hf(氢氟酸)溶液中,并对所述p型注入区310施加正压,所施加的正压例如为0.1v~10v,从而在所述p型注入区310中形成多孔311。125.接着,请参考图23,去除所述p型注入区310。在本技术实施例中,通过湿法腐蚀工艺去除所述p型注入区310以在所述半导体基底300中形成凹槽340并暴露出所述梳齿结构330。即在本技术实施例中,所述梳齿结构330的表面低于所述半导体基底300的表面,所述梳齿结构330两侧形成了凸台结构350,由此可以提高所形成的mems器件的性能,例如提高其驱动性能等。126.具体的,可以采用dhf(稀释的氢氟酸)溶液对所述p型注入区310执行湿法腐蚀工艺。例如,可以采用质量百分比浓度为49%的氢氟酸(hf)和质量百分比浓度为30%的双氧水(h2o2)的混合溶液,其中,氢氟酸和双氧水的比例例如为1:5;或者,可以采用质量百分比浓度为49%的氢氟酸(hf)、质量百分比浓度为70%的硝酸(hno3)和乙酸(ch3cooh)的混合溶液,其中,氢氟酸、硝酸和乙酸的比例例如为3:16:1。所述dhf溶液对于所述p型注入区310和所述半导体基底300具有很高的刻蚀选择比,从而能够高效、可靠地去除所述p型注入区310。特别的,本技术实施例在前述工艺步骤中,对所述p型注入区310执行了疏松处理,以使得所述p型注入区310中形成多孔311,由此在本步骤中对所述p型注入区310执行湿法腐蚀工艺时,能够高效、可靠地去除所述p型注入区310,并使得所形成的凹槽形貌佳。127.综上可见,在本发明提供的mems器件的制造方法中,在半导体基底中形成p型注入区,对所述p型注入区执行疏松处理,以使得所述p型注入区中形成多孔,从而便于后续去除所述p型注入区。由此,在刻蚀形成梳齿结构的过程中,所采用的图形化的掩膜层可以形成在平整的表面,相应的提高了图形化的掩膜层的精度以及由此刻蚀而成的梳齿结构的精度,同时,由于对所述p型注入区执行了疏松处理以使得所述p型注入区中形成多孔,也能够方便地去除所述p型注入区而形成凹槽。128.上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

本文地址:https://www.jishuxx.com/zhuanli/20240726/123717.html

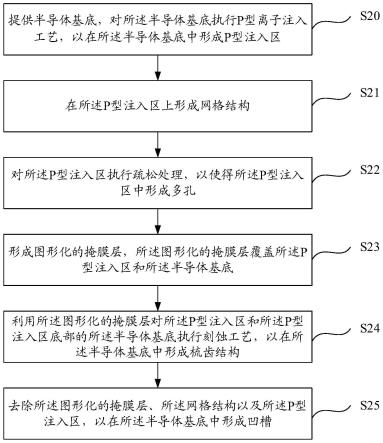

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。