半导体封装结构的制作方法

- 国知局

- 2024-07-27 12:51:47

1.本技术涉及半导体技术领域,具体涉及半导体封装结构。背景技术:2.随着封装技术的演进,各式各样的封装结构亦推陈出新。以玻璃在晶片上(glass on chip,goc)的封装结构为例,通常采用玻璃保护晶片,同时还利用模封物(mold compound)保护晶片和相关导线。玻璃和晶片之间需要有胶体固定并定义腔室厚度。模封物有可能会渗入玻璃与晶片之间,导致玻璃下形成多种材料介面。由于材料间的热膨胀系数不同而增加分层或掉盖的风险。技术实现要素:3.本技术提供了一种半导体封装结构,包括:4.承载体;5.盖体,设于所述承载体的上方;6.封装层,包覆所述盖体与所述承载体;7.缓冲层,设于所述盖体和所述封装层之间。8.在一些可选的实施方式中,所述盖体与所述封装层之间通过所述缓冲层隔开。9.在一些可选的实施方式中,所述缓冲层在所述承载体的竖直投影区域与所述盖体在所述承载体的竖直投影区域不重叠。10.在一些可选的实施方式中,所述缓冲层的厚度大于所述盖体的厚度。11.在一些可选的实施方式中,所述缓冲层包覆所述盖体的侧面。12.在一些可选的实施方式中,所述半导体封装结构还包括:13.基板,所述承载体设于所述基板的上方;14.导线,电连接所述基板和所述承载体,所述缓冲层包覆所述导线。15.在一些可选的实施方式中,所述封装层包覆所述导线。16.在一些可选的实施方式中,所述半导体封装结构还包括:17.支撑部,设于所述盖体和所述承载体的之间。18.在一些可选的实施方式中,所述缓冲层包覆所述支撑部。19.在一些可选的实施方式中,所述支撑部包覆所述盖体的侧面。20.在一些可选的实施方式中,所述盖体和所述承载体之间具有一空腔,所述支撑部用于定义所述空腔。21.在一些可选的实施方式中,所述缓冲层的弹性模量小于所述盖体的弹性模量和所述封装层的弹性模量。22.在一些可选的实施方式中,所述缓冲层的弹性模量小于所述支撑部的弹性模量。23.在一些可选的实施方式中,所述缓冲层的弹性模量小于所述承载体的弹性模量。24.本技术提供了一种半导体封装结构,通过在封装层与盖体之间设置缓冲层,防止封装层渗入盖体与承载体之间使得盖体底部接触多种材料,从而降低材料间热膨胀系数不匹配导致分层或掉盖的风险。可选地,利用缓冲层包覆盖体的侧表面,可有效避免封装层的应力施加于盖体上导致盖体破裂。可选地,利用缓冲层包覆导线,可起到保护导线的作用。附图说明25.通过阅读参照以下附图所作的对非限制性实施例所作的详细描述,本技术的其它特征、目的和优点将会变得更明显:26.图1是根据本技术的半导体封装结构的一个实施例的结构示意图;27.图1a是根据本技术的半导体封装结构的一个实施例的局部截面扫描电子显微镜(sem)图;28.图2至图6是根据本技术的半导体封装结构的一个实施例的制造过程中的结构示意图。29.符号说明:30.1-承载体,2-盖体,3-封装层,4-缓冲层,5-支撑部,6-基板,7-导线,8-空腔,9-胶材,10-缝隙。具体实施方式31.下面结合附图和实施例对说明本技术的具体实施方式,通过本说明书记载的内容本领域技术人员可以轻易了解本技术所解决的技术问题以及所产生的技术效果。可以理解的是,此处所描述的具体实施例仅仅用于解释相关实用新型,而非对该实用新型的限定。另外,为了便于描述,附图中仅示出了与有关实用新型相关的部分。32.需要说明的是,说明书附图中所绘示的结构、比例、大小等,仅用于配合说明书所记载的内容,以供本领域技术人员的了解与阅读,并非用以限定本技术可实施的限定条件,故不具技术上的实质意义,任何结构的修饰、比例关系的改变或大小的调整,在不影响本技术所能产生的功效及所能达成的目的下,均应仍落在本技术所揭示的技术内容得能涵盖的范围内。同时,本说明书中所引用的如“上”、“第一”、“第二”及“一”等用语,也仅为便于叙述的明了,而非用以限定本技术可实施的范围,其相对关系的改变或调整,在无实质变更技术内容下,当也视为本技术可实施的范畴。33.还需要说明的是,本技术的实施例对应的纵向截面可以为对应前视图方向截面,横向截面可以为对应右视图方向截面,而水平截面可以为对应上视图方向截面。34.应容易理解,本技术中的“在...上”、“在...之上”和“在...上面”的含义应该以最广义的方式解释,使得“在...上”不仅意味着“直接在某物上”,而且还意味着包括存在两者之间的中间部件或层的“在某物上”。35.此外,为了便于描述,本技术中可能使用诸如“在...下面”、“在...之下”、“下部”、“在...之上”、“上部”等空间相对术语来描述一个元件或部件与附图中所示的另一元件或部件的关系。除了在图中描述的方位之外,空间相对术语还意图涵盖装置在使用或操作中的不同方位。设备可以以其他方式定向(旋转90°或以其他定向),并且在本技术中使用的空间相对描述语可以被同样地相应地解释。36.另外,在不冲突的情况下,本技术中的实施例及实施例中的特征可以相互组合。下面将参考附图并结合实施例来详细说明本技术。37.图1是根据本技术的半导体封装结构的一个实施例的结构示意图。如图1所示,该半导体封装结构可以包括承载体1,设于承载体1上方的盖体2,包覆盖体2和承载体1的封装层3,以及设于盖体2和封装层3之间的缓冲层4。38.在本实施例中,承载体1可以提供承载功能。承载体1可以包括微机电系统(mems,micro-electro-mechanical system,mems)元件,例如光学传感器、湿度传感器等。承载体1还可以包括专用集成电路(application specific integrated circuit,asic)芯片。39.在本实施例中,盖体2起到保护承载体1的作用,例如可以采用玻璃、金属、硅、陶瓷等材质。40.在本实施例中,封装层3可以由各种模封材料(molding compound)形成。模封材料可包括环氧树脂(epoxy resin)、填充物(filler)、催化剂(catalyst)、颜料(pigment)、脱模剂(release agent)、阻燃剂(flame retardant)、耦合剂(coupling agent)、硬化剂(hardener)、低应力吸收剂(low stress absorber)、粘合促进剂(adhesion promoter)、离子捕获剂(ion trapping agent)等。41.在本实施例中,缓冲层4可以起到阻挡封装层3的作用,例如可以采用软性胶体等材质。通过设置缓冲层4,防止封装层3渗入盖体2与承载体1之间使得盖体2底部接触多种材料,从而降低材料间热膨胀系数不匹配导致分层或掉盖的风险。42.在一个实施例中,缓冲层4也可以为可吸收光的胶体,例如黑胶。43.在一个实施例中,盖体2与封装层3之间可以通过缓冲层4隔开,使得盖体2底部无需接触封装层3,降低了材料间热膨胀系数不匹配的风险,进而降低分层或掉盖的风险。44.进一步地,缓冲层4可以在承载体1的竖直投影区域与盖体2在承载体1的竖直投影区域不重叠,使得盖体2底部无需接触缓冲层4,降低了材料间热膨胀系数不匹配的风险,进而降低分层或掉盖的风险。45.在一个实施例中,缓冲层4的厚度可以大于盖体2的厚度。缓冲层4可以包覆盖体2的侧面。缓冲层4可有效隔绝封装层3释放的应力施加于盖体2导致盖体2破裂。46.在一个实施例中,该半导体封装结构还可以包括基板6、电连接基板6和承载体1的导线7。其中,承载体1可以设于基板6的上方。缓冲层4可以包覆导线7,起到保护导线7的作用。47.进一步地,封装层3可以包覆导线7,起到保护导线7的作用。48.在一个实施例中,该半导体封装结构还可以包括设于盖体2和承载体1的之间的支撑部5。缓冲层4可以包覆支撑部5。支撑部5例如可以采用uv胶。盖体2和承载体1之间可以具有一空腔8。支撑部5可以用于定义该空腔8。49.在一个实施例中,支撑部5可以包覆盖体2的侧面。从而可以避免封装层3和缓冲层4渗入盖体2的底部,使得盖体2底部无需接触封装层3和缓冲层4,降低了材料间热膨胀系数不匹配的风险,进而降低分层或掉盖的风险。50.在一个实施例中,缓冲层4的弹性模量可以小于盖体2的弹性模和封装层3的弹性模量。缓冲层4的弹性模量可以小于支撑部5的弹性模量。缓冲层4的弹性模量可以小于承载体1的弹性模量。从而可以利用缓冲层4吸收其他结构释放的应力,隔绝其他结构之间的应力,有效降低结构断裂的风险。51.在一个实施例中,该半导体封装结构还可以包括设于基板6与承载体1之间的胶材9。利用胶材9将承载体1固定于基板6上。这里,胶材9可以是芯片粘接薄膜(die attach film,daf)。52.图1a是根据本技术的半导体封装结构的一个实施例的局部截面扫描电子显微镜(sem)图。如图1a所示,盖体2底部只接触支撑部5,无接触缓冲层4和封装层3。封装层3和缓冲层4之间包括缝隙10。53.当半导体封装结构应用于光学传感器时,光线不仅会经过模封层和缓冲层4,还会经过缝隙10(空气),从而发生多次折射,导致能量损耗,进而降低了光的穿透力。另外,由于封装层3和缓冲层4之间的缝隙10与盖体2有一定的距离,且封装层3压在缓冲层4的上方,因此可以确保不会出现掉盖的现象。54.图2至图6是根据本技术的半导体封装结构的一个实施例的制造过程中的结构示意图。55.如图2所示,提供基板6。然后在载体上依次设置胶材9和承载体1。再利用导线7电连接基板6和承载体1。56.如图3所示,在承载体1上形成支撑部5。由于uv胶材的胶型易控制,所以支撑部5可以选用uv胶,从而可以通过控制胶型来提供更大的打线空间。57.如图4所示,在支撑部5上放置盖体2,利用支撑部5定义出盖体2与承载之间的空腔8。58.如图5所示,形成包覆导线7的缓冲层4。59.如图6所示,形成包覆缓冲层4的封装层3,得到半导体封装结构。60.本技术提供的制造半导体封装结构的方法能够实现与前述半导体封装结构类似的技术效果,这里不再赘述。61.尽管已参考本技术的特定实施例描述并说明本技术,但这些描述和说明并不限制本技术。所属领域的技术人员可清楚地理解,可进行各种改变,且可在实施例内替代等效元件而不脱离如由所附权利要求书限定的本技术的真实精神和范围。图示可能未必按比例绘制。归因于制造过程中的变量等等,本技术中的技术再现与实际设备之间可能存在区别。可存在未特定说明的本技术的其它实施例。应将说明书和图式视为说明性的,而非限制性的。可作出修改,以使特定情况、材料、物质组成、方法或过程适应于本技术的目标、精神以及范围。所有此些修改都落入在此所附权利要求书的范围内。虽然已参考按特定次序执行的特定操作描述本技术中所公开的方法,但应理解,可在不脱离本技术的教示的情况下组合、细分或重新排序这些操作以形成等效方法。因此,除非本技术中特别指示,否则操作的次序和分组并不限制本技术。

本文地址:https://www.jishuxx.com/zhuanli/20240726/123814.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

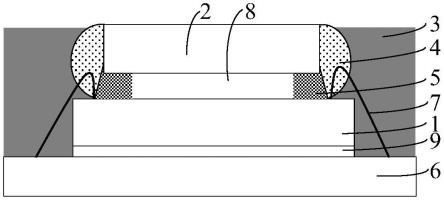

返回列表