半导体装置的制作方法

- 国知局

- 2024-07-27 12:47:07

1.本技术涉及半导体技术领域,具体涉及半导体装置。背景技术:2.目前部分mems(micro-electro-mechanical system,微机电系统)相关产品包括外露的mems晶片,mems晶片包括外露在产品外的感测区,用于接收来自外界的信号,例如声音、振动和气体等。除了mems晶片的感测区以外,mems晶片的其它部分、产品中的其它芯片和打线区域等仍需要被封装保护,而点胶封盖是较为常用的封装方式。3.参考图1和图2,一种点胶封盖封装的mems相关产品80包括底座81、封盖82和mems晶片83,mems晶片83上表面具有感测区831和非感测区832。考虑到mems晶片83要曝露在产品80外,必须在封盖82上设计开孔821,然后将mems晶片83设置于开孔821的下方,利用此开孔821曝露出mems晶片83的感测区831,利用此开孔821的边缘和mems晶片83的非感测区832做接触,来完成点胶封盖制程。制程上会先点胶,分别在底座81和mems晶片83的非感测区832设置胶体84,再压合封盖82,使封盖82与底座81粘合、mems晶片83与封盖82粘合,然后进行对胶体84进行固化,完成点胶封盖制程,实现对产品80的整体保护。4.通常,为了提升晶圆使用率,mems晶片83的上表面大部分被感测区831占据,非感测区832的尺寸有限。一些mems晶片83,其非感测区832的最小可碰触宽度d1不足200μm。5.由于非感测区832的尺寸有限,没有预留多余的空间进行点胶和溢胶,因此要做到点胶密封以及溢胶控制将变得极其困难,基于现行点胶封盖能力,会有溢胶流至感测区831造成产品失效的风险。技术实现要素:6.本技术提出了一种半导体装置,用于降低溢胶流至感测区的风险。7.第一方面,本技术提供一种半导体装置,包括:载板;封盖,设置于所述载板上,具有开口;半导体晶片,设置于所述载板上,并位于所述开口内;其中,所述开口大于所述半导体晶片,所述半导体晶片和所述封盖于垂直方向上不重叠。8.在一些可选的实施方式中,所述半导体晶片是用于感测外界环境的电子元件。9.在一些可选的实施方式中,所述半导体装置还包括:专用集成芯片(application specific integrated circuit,asic),设置于所述载板上,用于接收所述电子元件的感测信号。10.在一些可选的实施方式中,所述半导体装置还包括:胶体,设置于所述半导体晶片和所述封盖之间以固定所述半导体晶片。11.在一些可选的实施方式中,所述胶体和所述半导体晶片于垂直方向上不重叠。12.在一些可选的实施方式中,所述胶体接触所述半导体晶片的侧壁。13.在一些可选的实施方式中,所述半导体晶片的上表面具有感测区域,所述胶体不接触所述感测区。14.在一些可选的实施方式中,所述封盖设置有容纳所述胶体的槽体。15.在一些可选的实施方式中,所述半导体晶片和所述封盖之间具有位于所述槽体下方的缝隙,所述胶体延伸于所述缝隙内。16.在一些可选的实施方式中,所述半导体装置还包括:还包括:支撑体,设置于所述载板上,用于支撑所述半导体晶片。17.在一些可选的实施方式中,所述半导体晶片的上表面低于所述封盖的上表面。18.为了解决mems相关产品会有溢胶流至感测区造成产品失效的问题,本技术提出了一种半导体装置,通过将封盖上的开口设计成大于半导体晶片,并将半导体晶片设置于开口内而不是开口下方,且半导体晶片和封盖于垂直方向上不重叠,实现了将半导体晶片与封盖的粘合处从半导体晶片的上表面更改成半导体晶片的侧壁,以此,胶体设置于半导体晶片的侧壁,沿着半导体晶片的侧壁与封盖之间的缝隙利用张力支撑于两者之间。由于半导体晶片的感测区位于其上表面,而胶体不再设置于上表面,以此可以避免溢胶流至感测区而造成产品失效的风险,提升了产品的可靠性和可作业性。本技术方案适用于各种具有裸露晶片设计的半导体装置,尤其针对表面有不可触碰的感测区域的产品,可以有效控制溢胶。附图说明19.通过阅读参照以下附图所作的对非限制性实施例所作的详细描述,本技术的其它特征、目的和优点将会变得更明显:20.图1是现有的一种mems相关产品的纵向截面结构示意图;21.图2是现有的一种半导体晶片的俯视结构示意图;22.图3a是根据本技术的半导体装置的一个实施例3a的纵向截面结构示意图;23.图3b是根据本技术的半导体装置的一个实施例3a的俯视结构示意图;24.图4是根据本技术的半导体装置的一个实施例4a的纵向截面结构示意图;25.图5是根据本技术的半导体装置的一个实施例5a的纵向截面结构示意图;26.图6是根据本技术的半导体装置的一个实施例6a的纵向截面结构示意图。27.符号说明:28.1-载板;101-电连接件;2-封盖;21-上盖;22-侧盖;201-开口;202-槽体;203-支撑部;3-半导体晶片;301-感测区;302-侧壁;303-非感测区;4-芯片;5-胶体;6-缝隙;7-支撑体;81-底座;82-封盖;821-开孔;83-mems晶片;831-感测区;832-非感测区;84-胶体;d1-最小可碰触宽度。具体实施方式29.下面结合附图和实施例对说明本技术的具体实施方式,通过本说明书记载的内容本领域技术人员可以轻易了解本技术所解决的技术问题以及所产生的技术效果。可以理解的是,此处所描述的具体实施例仅仅用于解释相关发明,而非对该发明的限定。另外,为了便于描述,附图中仅示出了与有关发明相关的部分。30.应容易理解,本技术中的“在...上”、“在...之上”和“在...上面”的含义应该以最广义的方式解释,使得“在...上”不仅意味着“直接在某物上”,而且还意味着包括存在两者之间的中间部件或层的“在某物上”。31.此外,为了便于描述,本文中可能使用诸如“在...下面”、“在...之下”、“下部”、“在...之上”、“上部”等空间相对术语来描述一个元件或部件与附图中所示的另一元件或部件的关系。除了在图中描述的方位之外,空间相对术语还意图涵盖装置在使用或操作中的不同方位。设备可以以其他方式定向(旋转90°或以其他定向),并且在本文中使用的空间相对描述语可以被同样地相应地解释。32.本文中所使用的术语“层”是指包括具有一定厚度的区域的材料部分。层可以在整个下层或上层结构上延伸,或者可以具有小于下层或上层结构的范围的程度。此外,层可以是均质或不均质连续结构的区域,其厚度小于连续结构的厚度。例如,层可以位于连续结构的顶表面和底表面之间或在其之间的任何一对水平平面之间。层可以水平地、垂直地和/或沿着锥形表面延伸。基板(substrate)可以是一层,可以在其中包括一个或多个层,和/或可以在其上、之上和/或之下具有一个或多个层。一层可以包括多层。例如,半导体层可以包括一个或多个掺杂或未掺杂的半导体层,并且可以具有相同或不同的材料。33.本文中使用的术语“基板(substrate)”是指在其上添加后续材料层的材料。基板本身可以被图案化。添加到基板顶部的材料可以被图案化或可以保持未图案化。此外,基板可以包括各种各样的半导体材料,诸如硅、碳化硅、氮化镓、锗、砷化镓、磷化铟等。可替选地,基板可以由非导电材料制成,诸如玻璃、塑料或蓝宝石晶片等。进一步可替选地,基板可以具有在其中形成的半导体装置或电路。34.需要说明的是,说明书附图中所绘示的结构、比例、大小等,仅用于配合说明书所记载的内容,以供本领域技术人员的了解与阅读,并非用以限定本技术可实施的限定条件,故不具技术上的实质意义,任何结构的修饰、比例关系的改变或大小的调整,在不影响本技术所能产生的功效及所能达成的目的下,均应仍落在本技术所揭示的技术内容得能涵盖的范围内。同时,本说明书中所引用的如“上”、“第一”、“第二”及“一”等用语,也仅为便于叙述的明了,而非用以限定本技术可实施的范围,其相对关系的改变或调整,在无实质变更技术内容下,当也视为本技术可实施的范畴。35.还需要说明的是,本技术的实施例对应的纵向截面可以为对应前视图方向截面,横向截面可以为对应右视图方向截面,水平截面可以为对应上视图方向截面。36.另外,在不冲突的情况下,本技术中的实施例及实施例中的特征可以相互组合。下面将参考附图并结合实施例来详细说明本技术。37.参考图3a和3b,图3a和3b分别是根据本技术的半导体装置的一个实施例3a的纵向截面结构示意图和俯视结构示意图。如图3a和3b所示,本技术实施例的半导体装置3a包括:38.载板1;39.封盖2,设置于载板1上,具有开口201;40.半导体晶片3,设置于载板1上,并位于开口201内;41.其中,开口201大于半导体晶片3,且半导体晶片3和封盖2于垂直方向上不重叠。42.这里,载板1是半导体装置3a的底座,用来承载封盖2和半导体晶片3等。可选的,载板1是具有线路结构的板材,例如可以是基板(substrate)或者印制电路板(pcb,printed circuit board)等。可选的,载板1的底面,还可以设置有电连接件101,以便于与其它装置电性连接。43.这里,封盖(lid或cover)2是用于封装保护半导体装置3a的器件,它与载板1围合形成容纳腔,它的材质可以是金属或者塑料或者其它非金属材料或者混合材料等等。可选的,封盖2包括上盖21和侧盖22。侧盖22围合成一圈,其端部与上盖21连接,开口201可以开设在上盖21上。封盖2与载板1围合形成容纳腔。44.这里,半导体晶片3可以是一种mems(micro-electro-mechanical system,微机电系统)晶片(或称为mems芯片)。mems是用半导体技术在硅片上制造的电子机械系统,它是微米纳米级的机械系统。mems晶片可以把外界的物理、化学信号转换成电信号,通常用作感测外界环境的电子元件。举例来说,该mems晶片可以是mems麦克风晶片、mems扬声器晶片、mems加速度计晶片、mems陀螺仪晶片、mems磁传感器晶片、mems压力晶片、mems化学传感器晶片、mems可见光传感器晶片,或mems不可见光传感器晶片(例如用于感测红外光、紫外光、x射线)等等。45.在一些可选的实施方式中,半导体装置3a还包括胶体5。胶体5设置于半导体晶片3和封盖2之间以固定半导体晶片3。胶体5是一种粘结材料,用来将半导体晶片3与封盖2粘结固定在一起。在制程上,可以是通过点胶将液态的胶水设置在晶片3和封盖2之间,固化后呈现为胶体5。46.在一些可选的实施方式中,半导体晶片3具有侧壁302和上表面,上表面包括中央的感测区301和四周的非感测区303。可选的,胶体5接触半导体晶片3的侧壁302,不接触半导体晶片3上表面的感测区301和非感测区303,即,胶体5和半导体晶片3于垂直方向上不重叠,或者说,胶体5位于半导体晶片3的垂直投影区以外。47.在一些可选的实施方式中,部分胶体5还设置于载板1的上表面和封盖2的下表面之间,以便将封盖2贴合固定在载板1上。48.目前采用点胶封盖封装的mems相关产品,将半导体晶片3上表面的非感测区303作为点胶区和粘结处。由于半导体晶片3的上表面大部分面积被感测区301占据,非感测区303面积有限,没有预留多余的空间进行点胶和溢胶,导致压合封盖2后,会有溢胶流至感测区301的风险。另外,目前的mems相关产品,产品内除了半导体晶片3以外,还可能设计有其它芯片且可能采用堆叠结构,在设计时需要考虑芯片堆叠的公差来设计封盖2的高度,当芯片有多层时,封盖高度设计上要预留给累计公差的部分就随之变大,在有限的区域内点胶意味着需要选择高宽比大的胶体,不仅限制住胶种本身的选择性也增加溢胶至感测区301的风险。49.而本实施例的半导体装置3a,通过将封盖2上的开口201设计成大于半导体晶片3,并将半导体晶片3设置于开口201内而不是开口201下方,且半导体晶片3和封盖2于垂直方向上不重叠,实现了将半导体晶片3与封盖2的粘合处从半导体晶片3的上表面更改成半导体晶片3的侧壁302。半导体装置3a的制程相应的更改为:先对封盖2进行点胶固定,将封盖2贴合至载板1;再对半导体晶片3进行点胶固定,将半导体晶片3固定于封盖2的开口201内;其中,点胶形成的胶体5设置于半导体晶片3的侧壁302,沿着侧壁302与封盖2之间的缝隙利用张力支撑于两者之间。50.由于半导体晶片3的感测区301位于其上表面,而胶体5不再设置于上表面,以此可以避免胶体5碰触感测区301以及溢胶流至感测区301,减少了产品失效的风险,提升了产品的可靠性和可作业性。另外,通过将半导体晶片3与封盖2的粘合处从半导体晶片3上表面的非感测区303更改成半导体晶片3的侧壁302,降低了封盖2的设计高度,还避开了内部堆叠芯片的设计公差,有利于产品封装整合,提升产品的应用性。另外,在制程上是先贴合封盖2再对半导体晶片3进行点胶固定,不同于目前的先点胶再贴合封盖2,从而避开了封盖2压合会挤压胶体5而导致溢胶流至感测区301的风险。另外,在制程上将对载板1点胶和对半导体晶片3点胶这两个制程分离,增加了两者胶体种类的选择,可以更多元化地提供不同机械特性的材料,以解决不同产品的应力需求。另外,通过将半导体晶片3与封盖2的粘合处更改成半导体晶片3的侧壁302,可以更加自由的控制半导体晶片3的倾斜角度。51.在一些可选的实施方式中,封盖2设置有容纳胶体5的槽体202。且可选的,槽体202设置于开口201边缘,环绕开口201设置有一圈。点胶作业时,向槽体202内设置胶体5,置入的胶体5接触半导体晶片3的侧壁302,将半导体晶片3与封盖2粘结在一起。这里,槽体202可以起到溢胶槽的作用。52.在一些可选的实施方式中,槽体202的宽度大于非感测区303的最小可碰触宽度。示例性的,一种半导体晶片3的尺寸为1.9mm×1.9mm,感测区301(圆形)的直径为1.5mm,非感测区303的最小可碰触宽度d1为200μm;槽体202的宽度可以设计成在300μm到400微米之间,例如350μm。53.通过设置槽体202,使得封盖2和半导体晶片3之间有充足的点胶空间,降低了对点胶头的要求,在适合的点胶头大小下可以有更多胶种的选择,并改善了点胶头过小胶材颗粒堵塞后无法出胶的问题。另外,槽体202的设置,使得点胶平面设计上比半导体晶片3的表面更低,有利于下胶也同时确保落胶点比半导体晶片3的上表面更低,点胶制程中,通过适当调整出胶速度和胶针移动速度,即可以轻易地控制溢胶流动,防止胶体碰触半导体晶片3的上表面;并且,点胶作业宽度变成封装端可以设计控制的参数,有利于产品封装整合,应用性更高。54.在一些可选的实施方式中,开口201内的半导体晶片3与封盖2之间具有缝隙6,且该缝隙6位于槽体202下方。胶体5设置于槽体202后,可向下延伸至缝隙6内,以更好地将半导体晶片3与封盖2粘结在一起。55.在一些可选的实施方式中,半导体晶片3的上表面低于封盖2的上表面,以便封盖2可以起到更好地保护作用,减少半导体晶片3被外部损坏的可能。例如,由于封盖2设计高度略高于半导体晶片3,在半导体装置3a倒置时仍有保护产品的功能。56.在一些可选的实施方式中,半导体装置3a还包括至少一个芯片4,至少一个芯片4设置于载板1上,并位于封盖2与载板1围合形成的容纳腔内。至少一个芯片4可包括专用集成芯片(asic)。asic设置于载板1上,并与半导体晶片3通信连接,用于接收半导体晶片3的感测信号。asic是应特定用户要求和特定电子系统的需要而设计、制造的集成电路,它可以将接收到的感测信号进行转换和放大后输出。用cpld(复杂可编程逻辑器件)和fpga(现场可编程逻辑门阵列)来进行asic设计是较为流行的方式。57.参考图4,图4是根据本技术的半导体装置的一个实施例4a的纵向截面结构示意图。图4所示的半导体装置4a类似于图3a所示的半导体装置3a,不同之处在于:58.半导体装置4a还包括:支撑体7,设置于载板1上,并位于半导体晶片3的下方,用于支撑半导体晶片3。59.支撑体7可以设计成一个或多个,形状上没有限制,材料上可以采用金属材料,也可以采用非金属材料例如塑料等,例如可以采用与封盖2一样的材料。60.可选的,支撑体7的硬度大于普通的芯片例如asic芯片的硬度。61.可选的,支撑体7的上表面大于半导体晶片3的底面。62.这里,通过设置专用的支撑体7来支撑半导体晶片3,可以更好地固定半导体晶片3,避免半导体晶片3移位、脱落,同时也有利于制程。63.参考图5,图5是根据本技术的半导体装置的一个实施例5a的纵向截面结构示意图。图5所示的半导体装置5a类似于图3a所示的半导体装置3a,不同之处在于:64.半导体装置5a中,具有堆叠芯片结构,即,至少一个芯片4设置在半导体晶片3的下方,用于支撑半导体晶片3。例如可以有两个芯片4相堆叠,且用于支撑半导体晶片3。这里,通过堆叠芯片来支撑半导体晶片3,不需要设置专用的支撑体7(见图4)。65.参考图6,图6是根据本技术的半导体装置的一个实施例6a的纵向截面结构示意图。图6所示的半导体装置6a类似于图3a所示的半导体装置3a,不同之处在于:66.半导体装置6a中,封盖2具有向开口201内凸出的支撑部203,且支撑部203位于开口201的底部。半导体晶片3位于开口201内,且位于支撑部203上方,被支撑部203所支撑。胶体5可设置于半导体晶片3与支撑部203相接触的区域,胶体5不接触半导体晶片3的上表面。67.这里,利用支撑部203来支撑半导体晶片3,同样可以防止溢胶,避免溢胶流至感测区而造成产品失效的风险,并且,可以更好地固定半导体晶片3,避免半导体晶片3移位、脱落,同时也有利于制程。68.这里,半导体晶片3与下方的其它芯片相分离,与其它芯片位于封盖2与载板1围合形成的容纳腔内不同,半导体晶片3位于容纳腔之外,以此有利于制程。69.尽管已参考本技术的特定实施例描述并说明本技术,但这些描述和说明并不限制本技术。所属领域的技术人员可清楚地理解,可进行各种改变,且可在实施例内替代等效元件而不脱离如由所附权利要求书限定的本技术的真实精神和范围。图示可能未必按比例绘制。归因于制造过程中的变量等等,本技术中的技术再现与实际实施之间可能存在区别。可存在未特定说明的本技术的其它实施例。应将说明书和图示视为说明性的,而非限制性的。可作出修改,以使特定情况、材料、物质组成、方法或过程适应于本技术的目标、精神以及范围。所有此些修改都落入在此所附权利要求书的范围内。虽然已参考按特定次序执行的特定操作描述本文中所公开的方法,但应理解,可在不脱离本技术的教示的情况下组合、细分或重新排序这些操作以形成等效方法。因此,除非本文中特别指示,否则操作的次序和分组并不限制本技术。

本文地址:https://www.jishuxx.com/zhuanli/20240726/123575.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

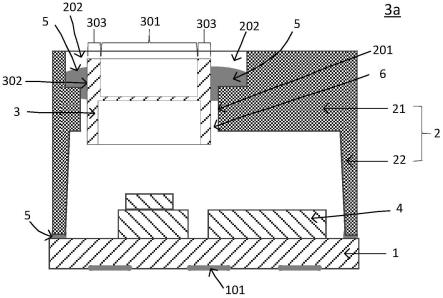

返回列表