半导体结构及其形成方法与流程

- 国知局

- 2024-07-27 12:45:03

1.本技术涉及半导体技术领域,具体涉及一种半导体结构及其形成方法。背景技术:2.目前常用的mems器件,通常包括mems结构以及读取电路,所述读取电路用于获取所述mems结构产生的电信号。3.现有技术中,形成mems器件的一种方式是,单独形成mems结构芯片和读取电路芯片,然后通过打线键合工艺形成两个芯片之间的电连接,但是打线键合会引入较大的信号噪声,加大了mems结构和读取电路的设计难度,同时两片芯片键合也使得mems器件芯片的体积较大。4.为了进一步提高mems器件性能并减小芯片体积,现有技术还采用另一种方式,具体包括:在同一片芯片上同时集成mems结构以及读取电路,通过金属互连制程实现mems结构与读取电路之间的电连接。该过程中,mems结构以及读取电路,均可以采用cmos工艺制成,但是需要同时兼顾mems结构以及读取电路内器件的性能,工艺开发难度大,周期长。并且,其中最为突出的问题是,由于mems结构的性能要求,通常其核心膜层会采用硅、多晶硅等膜层,需要采用高温制程工艺形成,因此必须在金属制程之前完成,以避免影响金属互连结构的电连接可靠性,这就限制了读取电路的工艺,增大了采用coms工艺在单芯片上同时集成读取电路和mems结构的难度。5.如何降低在单芯片上集成mems结构和读取电路的难度,是目前亟待解决的问题。技术实现要素:6.鉴于此,本技术提供一种半导体结构及其形成方法,以降低现有的单芯片器件集成的难度。7.本技术提供的一种半导体结构,包括:第一基底;位于所述第一基底表面的应用电路层;键合于所述应用电路层上的功能膜层,所述功能膜层的形成过程中采用的制备工艺条件对所述应用电路层内的至少部分结构具有负面影响。8.所述功能膜层的形成过程中采用的工艺包括高温制程,所述高温制程的温度在450℃以上。9.可选的,所述应用电路层包括应用电路以及连接所述应用电路的第一互连结构。10.可选的,所述功能膜层内形成有功能结构,以及连接所述功能结构与所述第一互连结构的第二互连结构。11.可选的,所述功能膜层表面直接键合于所述应用电路层表面。12.可选的,所述功能膜层通过一键合层键合于所述应用电路层表面。13.可选的,所述功能膜层为单层结构。14.可选的,所述功能膜层为多层结构,相邻层之间为键合界面或沉积界面。15.可选的,所述功能膜层包括单晶硅层、多晶硅层、碳化硅层、锗层、锗硅层、掺杂半导体层中的至少一种。16.可选的,所述功能结构包括mems结构。17.可选的,所述mesm结构包括:热偶结构、压感结构、加速度传感结构或硅麦克风结构中的至少一种。18.本技术还提供一种半导体结构的形成方法,包括:提供第一基底,在所述第一基底上形成应用电路层;提供第二基底,所述第二基底表面形成有功能膜层,所述功能膜层的形成过程中采用的制备工艺条件对所述应用电路层内的至少部分结构具有负面影响;将所述第二基底与所述第一基底相对键合固定,其中,所述功能膜层朝向所述应用电路层;去除所述第二基底。19.可选的,所述功能膜层的形成过程中采用的工艺包括高温制程,所述高温制程的温度在450℃以上。20.可选的,形成所述应用电路层的方法包括:形成应用电路以及连接所述应用电路的第一互连结构。21.可选的,去除所述第二基底之后,还包括:至少对所述功能膜层进行处理,形成功能结构;形成连接所述功能结构与所述第一互连结构的第二互连结构。22.可选的,对所述功能膜层进行处理包括离子注入、刻蚀或图形化中的至少一种。23.可选的,将所述第二基底与所述第一基底相对键合固定的方法包括:将所述功能膜层表面直接键合于所述应用电路层表面。24.可选的,将所述第二基底与所述第一基底相对键合固定的方法包括:将所述功能膜层通过一键合层键合于所述应用电路层表面。25.可选的,所述功能膜层为单层结构或多层结构。26.可选的,所述功能膜层包括单晶硅层、多晶硅层、碳化硅层、锗层、锗硅层、掺杂半导体层中的至少一种。27.可选的,所述功能结构包括mems结构。28.可选的,所述第一互连结构的材料至少包括金属。29.可选的,包括:提供soi衬底,所述soi衬底包括体硅层、顶层单晶硅层,以及位于所述顶层单晶硅层与所述体硅层之间的氧化硅层;以所述单晶硅层作为所述功能膜层,所述体硅层和所述氧化硅层作为所述第二基底。30.本技术的半导体结构的形成方法,将与应用电路层的制程有工艺冲突的功能膜层单独形成在独立的第二基底上,而后通过键合工艺键合至应用电路层上,并去除第二基底,完成所述功能膜层的转移,将功能膜层与应用电路层集成在同一芯片内。功能膜层与应用电路的制作过程相互独立,可以避免相互影响,降低了单芯片集成应用电路与功能膜层的难度。附图说明31.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。32.图1是本技术一实施例的半导体结构的形成方法的流程示意图;33.图2至图7是本技术一实施例的半导体结构的形成过程的结构示意图。具体实施方式34.如背景技术中所述,现有技术在单芯片上集成mems结构和读取电路存在高温制程和金属制程的工艺兼容性问题,导致单芯片集成难度较高。如果在金属制程之后,再进行高温制程,会导致金属融化、电迁移加剧等问题,导致金属的互连可靠性降低。在其他情况下,在集成功能结构与读取电路的工艺中,还会存在其他存在负面影响的情况,例如:在对功能结构中需要进行掺杂等处理时,需要对读取电路区域形成保护层等,导致工艺步骤复杂。35.下面结合附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅是本技术一部分实施例,而非全部实施例。基于本技术中的实施例,本领域技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。在不冲突的情况下,下述各个实施例及其技术特征可以相互组合。36.请参考图1,为本发明一实施例的半导体结构的形成过程的流程示意图。37.所述半导体结构的形成过程包括如下步骤:38.步骤s101:提供第一基底,在所述第一基底上形成应用电路层。39.步骤s102:提供第二基底,所述第二基底表面形成有功能膜层,所述功能膜层的形成过程中采用的制备工艺条件对所述应用电路层内的至少部分结构具有负面影响。40.所述负面影响包括使得性能变差、可靠性减低、良率下降、工艺制备难度提高、工艺参数冲突等多种不利于集成的情况。41.在一些实施例中,所述功能膜层的形成过程中采用的工艺包括高温制程。所述高温制程的温度在450℃以上。高温制程会对所述应用电路层内的电互连结构的可靠性造成负面影响。42.步骤s103:将所述第二基底与所述第一基底相对键合固定,其中,所述功能膜层朝向所述应用电路层。43.步骤s104:去除所述第二基底。44.通过上述方法,可以将所述功能膜层从第二基底转移至第一基底上的应用电路层上,如此,所述功能膜层与所述应用电路层可以分别形成,两者的工艺制程之间不会相互干扰。功能膜层的形成工艺中的高温制程不会对应用电路层内的结构造成影响。后续可以在步骤s104的基础上,对所述功能膜层进行处理,形成功能结构,例如mems结构,从而实现mems结构与读取电路的单芯片集成。45.以下结合附图对所述半导体结构的形成方法进行具体描述。46.请参考图2,提供第一基底100,在所述第一基底100上形成应用电路层110。47.所述第一基底100可以为半导体衬底,例如单晶硅衬底、锗硅衬底、碳化硅衬底等。所述应用电路层110的形成过程包括形成mos晶体管、层间介质层、导电柱以及互连线等结构。48.在所述第一基底100上形成所述应用电路层110,所述应用电路层110包括读取电路111,第一互连结构112以及填充于读取电路111的元件之间并且覆盖所述读取电路111和第一互连结构112的隔离介质层113。49.所述读取电路111为专用集成电路(asic),本领域技术人员,可以根据待形成的半导体结构的需求,设计合适的asic电路,在此不作限定。所述读取电路111内至少包括mos晶体管以及晶体管之间的互连结构,以形成cmos电路。50.所述第一互连结构112至少包括底部连接层1121、顶部连接层1123以及连接所述底部连接层1121和顶部连接层1123之间的层间互连柱1122。图2中所述第一互连结构112仅为示意,可以包括多层互连,根据需求对第一互连结构112的具体结构及布线方式进行设计,在此不作限定。所述第一互连结构112与所述读取电路111之间形成有电连接,用于将所述读取电路111电性引出,通过所述顶层连接层1123与外部结构形成电连接。51.所述第一互连结构112的材料至少包括金属,例如w、au、al、cu、ag等任意一种或几种。所述第一互连结构111还可以包括多晶硅、掺杂多晶硅或金属硅化物等非金属导电材料。52.所述隔离介质层113的材料包括氧化硅、氮氧化硅、碳氧化硅等介电材料。所述隔离介质层113通常为多层结构。53.所述隔离介质层113内还可以形成有空腔、空隙等结构。54.请参考图3,提供第二基底200,所述第二基底200表面形成有功能膜层210。55.该实施例中,所述功能膜层210为soi衬底表层的单晶硅层。所述第二基底200包括soi衬底中的体硅层201以及位于所述体硅层201以及所述功能膜层210之间的氧化硅层202。56.在其他实施例中,所述第二基底200还可以为单一材料层,例如硅层、玻璃等,作为载板,再在所述第二基底200表面通过一定工艺形成所述功能膜层210。57.所述功能膜层210用于通过cmos工艺形成特定的功能结构,例如mems结构。所述功能膜层210包括单晶硅层、多晶硅层、碳化硅层、锗层、锗硅层、掺杂半导体层中的至少一种。所述功能膜层210的形成过程中采用的工艺包括高温制程,所述高温制程的温度在450℃以上。所述高温制程包括沉积工艺、热退火工艺等。在一个实施例中,所述功能膜层210为单晶硅层,采用气相外延在第二基底表面外延生长单晶硅层,温度在700℃至1500℃范围内,或采用化学气相沉积工艺在第二基底200表面沉积形成所述单晶硅层,所述化学气相沉积工艺的温度通常在600℃至1500℃范围内。在另一实施例中,所述功能膜层210还可以为掺杂半导体层,在采用高温下的沉积工艺形成半导体层后,对所述半导体层进行离子掺杂并退火激活,此时,沉积工艺以及退火过程均为cmos工艺中的高温制程。在其他实施例中,也可以仅通过对所述第二基底200进行离子注入并退火处理,形成所述功能膜层210。58.该实施例中,所述功能膜层210为单层结构,在其他实施例中,所述功能膜层210为多层结构,例如si/sio2/si、si/si3n4/si、si/poly等各种材料层的组合。各个材料层可以通过沉积工艺依次堆叠形成。根据最终需要形成的功能结构的需求,合理设置所述功能膜层210的材料与结构。59.所述第二基底200与所述功能膜层210之间具有较高的刻蚀选择性,便于后续去除所述第二基底200。60.请参考图4,将所述第二基底200与所述第一基底100相对键合固定,其中,所述功能膜层210朝向所述应用电路层110。61.将所述第二基底200与所述第一基底100相对键合固定的方法包括:将所述功能膜层210表面直接键合于所述应用电路层110表面。所述功能膜层210表面与所述应用电路层110表面直接接触,在一定的压力和温度下,在所述功能膜层210与所述应用电路层110之间形成键合界面。62.该实施例中,所述功能膜层210为多晶硅层,所述应用电路层110的表面包括隔离介质层113和顶层互连层1123的表面。所述隔离介质层113的材料为sio2,所述顶层互连层1123的材料为cu,所述功能膜层210与所述应用电路层110之间的键合包括si-sio2键合,以及si-cu键合。在其他实施例中,所述功能膜层210与所述应用电路层110之间的键合界面还可以为其他键合类型,可以根据具体的键合类型,设置合适的键合压力和温度等参数。63.在其他实施例中,还可以将所述功能膜层210通过一键合层键合于所述应用电路层110表面。所述键合层可以为单层或多层结构,包括金属层、介质层中的至少一种。可以在功能膜层210表面形成键合层之后,将所述键合层表面与所述应用电路层110表面键合;或者,在所述应用电路层110表面形成键合层,然后将所述功能膜层210表面与所述键合层表面键合;或者,所述键合层包括两个键合子层,在所述功能膜层210和所述应用电路层110表面分别形成一键合子层,然后将两个键合子层相对键合。本领域技术人员可以根据需求,在所述功能膜层210与所述应用电路层110之间设置合适材料的键合层。64.请参考图5,去除所述第二基底200。65.可以通过干法或施法刻蚀工艺去除所述第二基底200,仅保留所述功能膜层210位于所述应用电路层110表面,至此,将所述功能膜层210从所述第二基底200上转移至所述应用电路层110表面。66.由于所述功能膜层210并非在所述应用电路层110表面直接形成,因此,所述功能膜层210的形成过程对所述应用电路层110内以及所述第一基底100内的器件不会造成影响,两者的工艺制程之间不会存在相互制约的问题,从而可以降低所述应用电路层110与所述功能膜层210的形成难度。并且,所述功能膜层210堆叠于所述应用电路层110上,可以降低芯片面积,提高集成度。67.在其他实施例中,还可以采用转移所述功能膜层210至应用电路层210上的方式,通过多次键合堆叠,在所述功能膜层210表面再键合其他的膜层,形成堆叠结构。68.请参考图6,对所述功能膜层210(请参考图5)进行处理,形成功能结构220。69.该实施例中,所述功能结构220为热偶结构,具体包括:通过掺杂以及图形化工艺,对所述功能膜层210进行处理,形成第一热偶条221和所述第二热偶条222,所述第一热偶条221和所述第二热偶条222的材料为不同类型掺杂的多晶硅,具体的,所述第一热偶条221为n型掺杂多晶硅,所述第二热偶条222为p型掺杂多晶硅。所述第一热偶条221和所述第二热偶条222可以为长条直线形、弧线形或各种合适的形状。70.请参考图7,形成连接所述功能结构220与所述第一互连结构112的第二互连结构240。71.形成覆盖所述功能结构220的介质层230后,刻蚀所述介质层230,形成通孔,再所述通孔内填充导电材料,形成互连柱241,以及在所述介质层230表面形成互连线242,部分互连柱241形成于所述第一所述第一热偶条221与第二热偶条222上,通过所述互连柱241和互连线242,实现第一热偶条221、第二热偶条222之间的串联连接,形成热电堆。所述第二互连结构240还与所述应用电路层110内的第一互连结构112连接,用于实现功能结构220与所述读取电路111之间的电连接,所述功能结构220产生的电信号通过所述第二互连结构240、第一互连结构112传输至所述读取电路111。72.在其他实施例中,所述功能结构220还可以包括其他结构,例如mems结构,所述mems结构包括但不限于热偶结构、压感结构、加速度传感结构或硅麦克风结构中的至少一种,在此不作限定。可以通过离子注入、刻蚀或图形化中的至少一种方式对所述功能膜层210进行处理形成。除了对所述功能膜层210进行处理之外,还可以根据需要对所述应用电路层110内的隔离介质层113进行刻蚀等处理,形成空腔等结构,以配合所述功能结构220的功能需求。本领域技术人员可以根据需要,在形成所述隔离介质层113的过程中,在所述隔离介质层113内提前设置牺牲层或其他必要的结构。73.所述第二互连结构240的材料至少包括金属,例如w、au、al、cu、ag等任意一种或几种。采用金属制程形成所述第二互连结构230,温度较低,不会对其他结构造成影响。74.上述半导体结构形成方法,将与应用电路层的形成工艺有冲突的功能膜层单独形成在独立的第二基底上,而后通过键合工艺键合至应用电路层上,并去除第二基底,完成所述功能膜层的转移,将功能膜层与应用电路层集成在同一芯片内。且功能膜层与应用电路的制作过程相互独立,可以避免相互影响,提高芯片的可靠性。75.本发明的实施例还提供一种半导体结构。76.请参考图5,为本发明一实施例半导体结构的结构示意图。77.所述半导体结构包括:第一基底100;位于所述第一基底100表面的应用电路层110;键合固定于所述应用电路层110上的功能膜层210。78.所述第一基底100可以为半导体衬底,例如单晶硅衬底、锗硅衬底、碳化硅衬底等。所述应用电路层110内包括读取电路111,第一互连结构112以及填充于读取电路111的元件之间并且覆盖所述读取电路111和第一互连结构112的隔离介质层113。所述读取电路111为专用集成电路(asic),本领域技术人员可以根据待形成的半导体结构的需求,设计合适的asic电路,在此不作限定。79.所述第一互连结构112至少包括位于底部连接层1121、顶部连接层1123以及连接所述底部连接层1121和顶部连接层1123之间的层间互连柱1122。所述第一互连结构112与所述读取电路111形成有电连接,用于将所述读取电路111电性引出,通过所述顶层连接层1123与外部结构形成电连接。图5中所述第一互连结构112仅为示意,可以包括多层互连,可以根据需求设计具体结构及布线方式,在此不作限定。所述隔离介质层113的材料包括氧化硅、氮氧化硅、碳氧化硅等介电材料。所述隔离介质层113可以为单层或多层结构。根据需要,所述隔离介质层110内还可以形成有其他器件结构,在此不作限定。80.所述功能膜层210包括单晶硅层、多晶硅层、碳化硅层、锗层、锗硅层、掺杂半导体层中的至少一种。所述功能膜层的形成过程中采用的工艺包括高温制程,所述高温制程的温度在450℃以上。81.该实施例中,所述功能膜层210表面直接键合于所述应用电路层110表面。在其他实施例中,所述功能膜层通过键合层键合于所述应用电路层表面。82.在一个实施例中,所述功能膜层210为单层结构。在其他实施例中,所述功能膜层210还可以为多层结构,例如si/sio2/si、si/si3n4/si、si/poly等各种材料层的组合。各个材料层可以通过沉积工艺或键合方式依次堆叠形成。所述功能膜层210内的各材料层之间具有沉积界面或键合界面。83.所述功能膜层210在所述应用电路层110形成之后,通过键合工艺转移至所述应用该电路层110上,所述应用电路层110形成过程中的工艺制程与所述功能膜层210形成过程的工艺制程之间相互独立。在形成所述功能膜层210过程中的高温制程不会对应用电路层110内的器件造成不利影响。并且,所述功能膜层210堆叠于所述应用电路层110上,可以降低芯片面积,提高集成度。84.请参考图6,为本发明另一实施例的半导体结构的示意图。85.该实施例中,在图5所示结构的基础上,所述功能膜层210(请参考图5)被处理为功能结构220。所述功能结构220可以包括mems结构,包括但不限于热偶结构、压感结构、加速度传感结构或硅麦克风结构中的至少一种。可以通过离子注入、刻蚀或图形化等工艺对所述功能膜层210进行处理后形成所述功能结构220。86.所述半导体结构还包括第二互连结构240,所述第二互连结构240连接所述功能结构220与所述第一互连结构112,可以将所述功能结构220产生的电信号通过所述第二互连结构230、第一互连结构112传输至所述读取电路111。87.该实施例中,所述功能结构220为热偶结构,包括第一热偶条221和所述第二热偶条222,所述第一热偶条221为n型掺杂多晶硅,所述第二热偶条222为p型掺杂多晶硅。所述第一热偶条221和所述第二热偶条222可以为长条直线形、弧线形或各种合适的形状。88.所述半导体结构还包括覆盖所述功能结构220的介质层230,所述第二互连结构240包括位于所述介质层230的互连柱241,以及形成于所述介质层240表面,与所述互连柱241连接的互连线242。部分互连柱241形成于所述第一所述第一热偶条221与第二热偶条222上,通过所述互连柱241和互连线242,实现第一热偶条221、第二热偶条222之间的串联连接。部分互连柱241与所述应用电路层110内的顶层互连层1123连接,实现功能结构220与所述读取电路111之间的电连接。89.在其他实施例中,根据所述功能结构220的结构需要,所述应用该电路层110的隔离介质层113内还可以形成有空腔、反射层等结构,再次不作限定,本领域技术人员可以根据需求进行设置。90.所述功能结构220集成于所述应用电路层110上方,且通过互连结构形成电连接,提高了芯片的集成度。91.以上所述仅为本技术的实施例,并非因此限制本技术的专利范围,凡是利用本技术说明书及附图内容所作的等效结构或等效流程变换,例如各实施例之间技术特征的相互结合,或直接或间接运用在其他相关的技术领域,均同理包括在本技术的专利保护范围内。

本文地址:https://www.jishuxx.com/zhuanli/20240726/123388.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

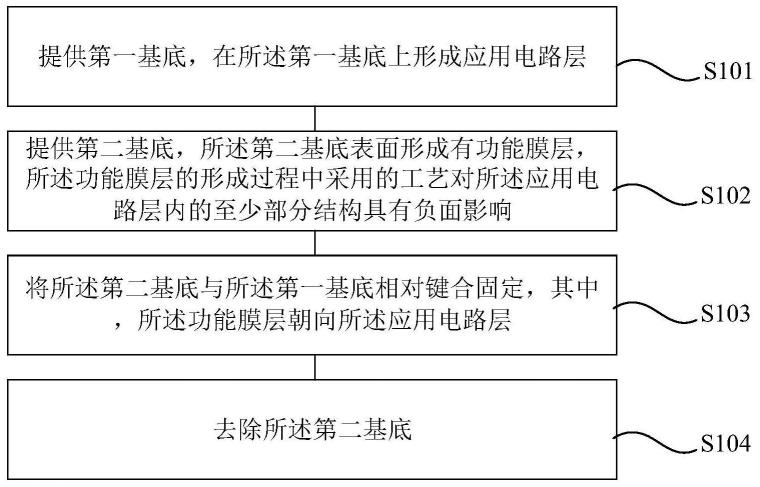

返回列表