半导体结构的制备方法及半导体结构与流程

- 国知局

- 2024-07-27 12:49:52

1.本发明涉及半导体制备技术领域,尤其是涉及一种半导体结构的制备方法及半导体结构。背景技术:2.具有高深宽比、透明的沟槽或柱状结构在mems器件特别是微型光学器件和微流体器件的制备方面有着广泛的应用。3.目前通常使用的制备方式是在硅衬底上热生长或沉积二氧化硅,对二氧化硅直接进行刻蚀形成沟槽。4.这种方法的缺点在于:很难制备出同时具有高深宽比,微小沟槽间隙,和良好陡直度侧壁的沟槽结构,从而使器件的性能大打折扣。技术实现要素:5.本发明的目的在于提供一种半导体结构的制备方法及半导体结构,以缓解现有技术中很难制备出同时具有高深宽比,微小沟槽间隙和良好陡直度侧壁的沟槽结构的技术问题。6.本发明实施例提供的一种半导体结构的制备方法,包括步骤:7.s10.提供一硅基底和一衬底,将硅基底的底面与衬底进行连接;8.s20.按照公式(1)、(2)、(3)和(4),根据待制备的氧化硅沟槽的目标尺寸以及氧化形变率α得到待刻蚀的硅沟槽的初始尺寸;9.其中,所述目标尺寸包括氧化硅沟槽的底面与衬底的上表面的距离d,氧化硅沟槽的宽度s和深度h,用于分离相邻两个氧化硅沟槽的氧化硅柱体的宽度l;所述s小于2微米,氧化硅柱体的宽深比(l/h)大于5;10.其中,所述初始尺寸包括硅沟槽底面与硅基底的下表面之间的距离d,硅沟槽的宽度s,硅柱体的宽度l和高度h;11.l=l/αꢀꢀꢀꢀ(1)12.s=(1-1/α)*l+sꢀꢀꢀꢀ(2)13.d=d/αꢀꢀꢀꢀ(3)14.h=h-(1-1/α)*l/2+dꢀꢀꢀꢀ(4)15.s30.对硅基底的上表面进行刻蚀,从而在硅基底的上表面形成具有初始尺寸的多个硅沟槽;16.s40.在环境为温度为900℃-1100℃的条件下,对硅沟槽进行氧化处理1-15小时,从而获得具有目标尺寸的氧化硅沟槽。17.进一步的,所述方法包括在步骤s30之前进行的,根据硅基底的厚度h0和氧化硅沟槽的深度h,对硅基底的上表面进行研磨减薄处理,以使氧化硅沟槽的底面与衬底的上表面之间的距离d的取值范围为0-1微米。18.进一步的,所述研磨减薄处理具体包括:19.机械研磨。20.进一步的,所述研磨减薄处理具体包括:21.化学机械抛光。22.进一步的,所述衬底为石英衬底。23.进一步的,所述步骤s10中,硅基底的底面与石英衬底通过键合的方式连接。24.进一步的,所述方法包括在步骤将硅基底的底面与衬底进行连接之前进行的步骤:25.步骤s111.利用等离子激活和/或表面化学机械平整工艺分别对硅基底的底面和石英衬底进行处理。26.进一步的,经过所述步骤s111后,硅基底的底面和石英衬底结合后二者之间的间距范围在1埃-9埃。27.第二方面,本发明实施例提供的半导体结构,所述半导体结构由上述的半导体结构的制备方法制备而成。28.本发明实施例提供的半导体结构的制备方法,包括步骤:s10.提供一硅基底和一衬底,将硅基底的底面与衬底进行连接;s20.按照公式(1)、(2)、(3)和(4),根据待制备的氧化硅沟槽的目标尺寸以及氧化形变率α得到待刻蚀的硅沟槽的初始尺寸;其中,所述目标尺寸包括氧化硅沟槽的底面与衬底的上表面之间的距离d,氧化硅沟槽的宽度s和深度h,用于分离相邻两个氧化硅沟槽的氧化硅柱体的宽度l;所述s小于2微米,氧化硅柱体的宽深比(l/h)大于5;其中,所述初始尺寸包括硅沟槽底面与硅基底的下表面之间的距离d,硅沟槽的宽度s,硅柱体的宽度l和高度h;l=l/α(1);s=(1-1/α)*l+s(2);d=d/α(3);h=h-(1-1/α)*l/2+d(4);s30.对硅基底的上表面进行刻蚀,从而在硅基底的上表面形成具有初始尺寸的多个硅沟槽;s40.在环境为温度为900℃-1100℃的条件下,对硅沟槽进行氧化处理1-15小时,从而获得具有目标尺寸的氧化硅沟槽。具有目标尺寸的氧化硅沟槽很容易通过对硅基底的设计及精细的工艺控制实现。与现有技术相比,本技术中并未直接对氧化硅结构进行直接加工;而是,通过氧化硅沟槽的尺寸反推导硅沟槽的尺寸,实现硅沟槽尺寸的精准控制,然后对硅沟槽进行氧化处理从而得到氧化硅沟槽,在上述的制备条件下,可以得到具有高深宽比,微小沟槽间隙和良好陡直度侧壁的氧化硅沟槽。附图说明29.为了更清楚地说明本发明具体实施方式或现有技术中的技术方案,下面将对具体实施方式或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施方式,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。30.图1为本发明实施例提供的半导体结构的制备方法中步骤s10的示意图;31.图2为本发明实施例提供的半导体结构的制备方法中研磨减薄处理的示意图;32.图3为本发明实施例提供的半导体结构的制备方法中步骤s30的示意图;33.图4为本发明实施例提供的半导体结构的制备方法中步骤s40的示意图。34.图标:100-硅基底;110-氧化硅沟槽;120-氧化硅柱体;130-硅沟槽;140-硅柱体;200-石英衬底。具体实施方式35.下面将结合实施例对本发明的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。36.如图1-图4所示,本发明实施例提供的半导体结构的制备方法,包括步骤:37.s10.提供一硅基底100和一衬底,将硅基底100的底面与衬底进行连接。38.本技术采用的制备方法主要区别于现有技术的关键点便在于,本技术处理的对象为硅基底100,而不是氧化硅基底。现有技术中,某些方案中采用直接刻蚀氧化硅基底100形成的沟槽,采用这样手段获得的沟槽的间隙具有明显的上宽下窄的倒梯形结构,侧壁也明显的不垂直,若继续增加沟槽深度,势必造成侧壁陡直进一步变差,因而限制了获得更高的宽深比的沟槽。39.而先对硅基底100进行加工则不会出现上述的问题,可以获得精确尺寸的硅沟槽130。40.s20.按照公式(1)、(2)、(3)和(4),根据待制备的氧化硅沟槽110的目标尺寸以及氧化形变率α得到待刻蚀的硅沟槽130的初始尺寸;其中,所述目标尺寸包括氧化硅沟槽110的底面与衬底的上表面之间的距离d,氧化硅沟槽110的宽度s和深度h,用于分离相邻两个氧化硅沟槽110的氧化硅柱体120的宽度l;所述s小于2微米,氧化硅柱体120的宽深比(l/h)大于5;其中,所述初始尺寸包括硅沟槽130底面与硅基底100的下表面之间的距离d,硅沟槽130的宽度s,硅柱体140的宽度l和高度h;41.l=l/αꢀꢀꢀꢀ(1)42.s=(1-1/α)*l+sꢀꢀꢀꢀ(2)43.d=d/αꢀꢀꢀꢀ(3)44.h=h-(1-1/α)*l/2+dꢀꢀꢀꢀ(4)45.本技术中,通过氧化硅沟槽110的尺寸(目标尺寸)反推导硅沟槽130的尺寸(初始尺寸),实现硅沟槽130尺寸的精准控制,之所以采用上述的方案,而不是采用直接加工氧化硅基底100得到氧化硅沟槽110的主要原因在于,目标尺寸的氧化硅沟槽110中,所述s小于2微米,氧化硅柱体120的宽深比(l/h)大于5,所要得到的氧化硅沟槽110的宽度窄,且宽深比大,传统方案无法实现这类氧化硅沟槽110的制备。目标尺寸为已知量,而在环境为温度为900℃-1100℃的氧化处理时间为1-15小时的条件下,氧化形变率α的取值范围为2.0-2.6之间,该值为实验得到经验系数,属于已知量。然后,通过公式(1)、(2)、(3)和(4)可以的到初始尺寸,初始尺寸的获取方便。46.s30.对硅基底100的上表面进行刻蚀,从而在硅基底100的上表面形成具有初始尺寸的多个硅沟槽130。47.在获得了初始尺寸后,可以按照初始尺寸对硅基底100进行刻蚀,得到符合上述初始尺寸要求的硅沟槽130。硅基底100的图案化加工处理为现有技术,具体的,可以先通过光刻工艺在硅基底100的上表面形成掩模图案,然后,通过掩模图案,对硅基底100施以等离子干法蚀刻,形成硅沟槽130。48.s40.在环境为温度为900℃-1100℃的条件下,对硅沟槽130进行氧化处理1-15小时,从而获得具有目标尺寸的氧化硅沟槽110。49.在符合初始尺寸的硅沟槽130制备完成后,利用高温氧化的手段,将硅沟槽130完全氧化呈氧化硅沟槽110,包括将硅沟槽130的底面和侧壁完全氧化。50.综上,具有目标尺寸的氧化硅沟槽110很容易通过对硅基底100的设计及精细的工艺控制实现。与现有技术相比,本技术中并未直接对氧化硅结构进行直接加工;而是,通过氧化硅沟槽110的尺寸反推导硅沟槽130的尺寸,实现硅沟槽130尺寸的精准控制,然后对硅沟槽130进行氧化处理从而得到氧化硅沟槽110,在上述的制备条件下,可以得到具有高深宽比,宽深比(l/h)大于5,微小沟槽间隙(s小于2微米)和良好陡直度(陡直度小于0.5°)侧壁的氧化硅沟槽110。51.需要说明的,实际中,氧化硅沟槽110侧壁多少都有些倾斜,陡直度是衡量沟槽侧壁与其底面垂直程度的一个量。定义陡直度为沟槽侧壁和一条竖直线间的夹角θ,则这个角度越小侧壁越垂直于沟槽底面,反之侧壁与底面形成斜坡面。52.所述方法包括在步骤s30之前进行的,根据硅基底100的初始厚度h0(即研磨前的厚度)和氧化硅沟槽110的深度h,对硅基底100的上表面进行研磨减薄处理,以使氧化硅沟槽110的底面与衬底的上表面之间的距离d的取值范围为0-1微米。53.将硅基底100的厚度从h0减薄至所需厚度h,这个厚度h的重点在于经过后续的刻蚀和高温氧化后其结构整体是透明的,尤其是氧化硅沟槽110的底面与衬底的上表面之间的部分。由于沟槽结构的尺寸比较小,从亚微米到几十微米不等,并且与下面的石英衬底200紧邻,故需要将通常厚度为几百微米厚的硅基底100减薄到几十微米厚,并在剩余厚度的硅基底100(已与石英衬底200键合)上加工出沟槽。通过上述的尺寸限定,可以保持后续制备的氧化硅沟槽110的透明属性,从而提高了基于此结构制备的器件的性能。54.所述研磨减薄处理具体包括机械研磨,还可以包括化学机械抛光。具体的,减薄处理的第一步可以是通过机械研磨,对硅基底100的上表面进行研磨,将硅基底100厚度减至接近目标厚度h,然后经过化学机械抛光使其表面光滑平整,便于后续工艺的实施。55.衬底为石英衬底200,步骤s10中将硅基底100的底面与石英衬底200进行连接。56.石英衬底200起到支撑的作用,同时,石英衬底200保持了整体结构的透明性能。硅基底100的底面与石英衬底200通过键合的方式连接,两个基底的界面先形成氢键/范德华力,经过高温退火后形成si-o-si共价键,从而把2个基底键合在一起。57.在键合前,可以对硅基底100和石英衬底200进行表面处理,包括:步骤s111.利用等离子激活和/或表面化学机械平整工艺分别对硅基底100的底面和石英衬底200进行处理。等离子激活的机理来自于其产生的多重效应而显著改变材料表面结构。带电粒子可以电离原子,破坏形成晶格的化学键而形成悬空键;等离子体将离子注入材料并产出表面带电粒子,形成电场,从而增加材料表面的化学活性并影响离子移动性,从而可以在两个材料的界面形成较强的键合。化学机械平整(cmp)则是通过材料表面与研磨液的化学反应协同机械研磨将基底表面平整化。经过cmp处理的两个基底的表面硅基底100的底面和石英衬底200结合后二者之间的间距范围在1埃-9埃,接近到几个埃(0.1纳米)的距离,使得两个表面之间更容易产生氢键/范德华力。58.本发明实施例提供的半导体结构,所述半导体结构由上述的半导体结构的制备方法制备而成。通过上述方法制备的半导体结构,具有高深宽比,宽深比(l/h)大于5,微小沟槽间隙(s小于2微米)和良好陡直度(陡直度小于0.5°)侧壁的氧化硅沟槽110的半导体结构。这种具有大的宽深比和良好的透明性能的微型沟槽的半导体结构在mems领域有着广泛的应用前景,特别是微光学器件、微流体器件等的应用。59.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

本文地址:https://www.jishuxx.com/zhuanli/20240726/123718.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

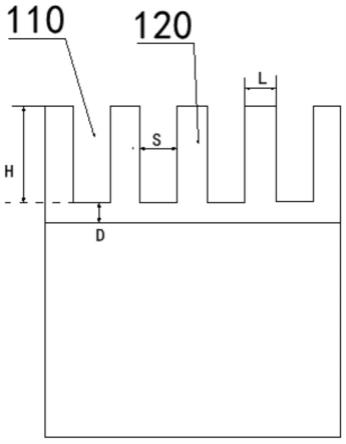

返回列表