塑封空腔结构及其制作方法与流程

- 国知局

- 2024-07-27 12:52:45

1.本技术涉及电子器件封装技术领域,尤其涉及一种塑封空腔结构及其制作方法。背景技术:2.mems(微机电系统)传感器在医疗、汽车、通讯及计算机领域广泛应用,mems传感器包含mems麦克风、mems气压计、mems温湿度计、mems气体传感器等。封装结构主要包含封装基板、mems传感芯片、asic(专用集成电路)芯片、保护外壳以及mems传感芯片实现环境感知的通道,当前电子产品呈现短小轻薄的发展趋势,因此对mems传感封装结构提出了小型化、高密度集成化的需求。3.现有的mems传感器和asic芯片的封装主要是将mems传感芯片和asic芯片贴装于封装基板上,通过wire bond(引线键合)等方式实现mem传感芯片、asic芯片与封装基板的电性连接,然后贴装保护外壳,对封装的器件进行保护,并在基板上或者保护外壳预留通孔,实现mems传感芯片与外部环境交互。因此,现有的塑封空腔结构存在封装体积大,无法满足半导体封装短小轻薄的发展需求;每个传感器单元需要单独施加保护罩,加工效率低且成本高;施加保护罩的方式,加工精密程度差,无法满足高密度封装的发展需求等问题。技术实现要素:4.有鉴于此,本技术的目的在于提出一种塑封空腔结构及其制作方法。5.基于上述目的,本技术提供的塑封空腔结构的制作方法,包括如下步骤:6.(a)准备嵌埋封装框架;所述嵌埋封装框架包括沿高度方向分别贯穿绝缘层的第一空腔和第一导通柱;7.(b)在所述第一空腔的底部嵌埋芯片组;所述芯片组包括层叠设置的第一芯片和第二芯片,且所述第一芯片和所述第二芯片的背面彼此贴合,使得二者的端子面彼此相背;8.(c)在所述芯片组与所述第一空腔的间隙内形成封装层;所述封装层具有暴露所述第二芯片的端子的盲孔;9.(d)在所述嵌埋封装框架的上表面形成第一线路层和第二导通柱,所述第一线路层与所述第二芯片的端子导通连接;10.(e)在所述第一线路层的上表面层压第一介质层;其中,使所述第一介质层的上表面与所述第二导通柱的上表面齐平;11.(f)在所述第一介质层的上表面形成第二线路层,在所述嵌埋封装框架的下表面形成第三线路层,并在所述第三线路层上形成围绕所述第一空腔的支撑柱围墙;12.(g)形成沿高度方向依次贯穿所述第一介质层和所述绝缘层的通孔,其中所述通孔被上述支撑柱围墙围绕;13.(h)在所述嵌埋封装框架的下方沿所述支撑柱围墙的外侧形成塑封层,在所述塑封层与所述嵌埋封装框架之间形成第二空腔。14.10.本技术实施例还提供了一种塑封空腔结构,具有沿高度方向分别贯穿绝缘层的第一空腔和第一导通柱的嵌埋封装框架;设置在所述第一空腔内的芯片组;设置在所述嵌埋封装框架上表面的第一线路层;设置在所述第一线路层上的第一介质层;设置在所述第一介质层上的第二线路层;贯穿所述第一介质层和所述绝缘层的通孔;在所述嵌埋封装框架下表面的第三线路层;在所述第三线路层上的支撑柱围墙;以及沿所述支撑柱围墙外侧形成的塑封层;15.其中在所述塑封层与所述嵌埋封装框架的下表面之间形成有与所述通孔连通的第二空腔,以及所述芯片组包括背靠背层叠设置的第一芯片和第二芯片。16.从上面所述可以看出,本技术实施例提供的塑封空腔结构,通过将层叠设置的第一芯片和第二芯片组成的芯片组堆叠嵌埋封装于封装基板内部,通过封装层的盲孔实现与封装基板的电连接,并在嵌埋封装基板顶部(也即下表面)加工铜柱围墙,封装后可形成第二空腔,通过第二空腔和通孔实现与外部环境的传感;能够实现高密度集成封装,具有高的精密度,且封装体积小型化和封装效率高等优点。附图说明17.为了更清楚地说明本技术或相关技术中的技术方案,下面将对实施例或相关技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。18.图1示出了现有技术中的mems传感器和asic芯片的主流封装方式结构示意图;19.图2示出了本技术实施例提供的塑封空腔结构的剖面图;20.图3a-图3i示出了本技术实施例的塑封空腔结构的制造方法的各个步骤的中间结构的截面示意图。具体实施方式21.为使本技术的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本技术进一步详细说明。22.需要说明的是,除非另外定义,本技术实施例使用的技术术语或者科学术语应当为本技术所属领域内具有一般技能的人士所理解的通常意义。本技术实施例中使用的“第一”、“第二”以及类似的词语并不表示任何顺序、数量或者重要性,而只是用来区分不同的组成部分。“包括”或者“包含”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。“连接”或者“相连”等类似的词语并非限定于物理的或者机械的连接,而是可以包括电性的连接,不管是直接的还是间接的。“上”、“下”、“左”、“右”等仅用于表示相对位置关系,当被描述对象的绝对位置改变后,则该相对位置关系也可能相应地改变。23.图1示出了现有技术中的mems传感器和asic芯片的主流封装方式结构示意图。24.如图1所示,一些mems传感器和asic芯片的主流封装方式中,针对由mem传感芯片和asic芯片与封装基板通过键合引线的电性连接形成的多个单元,需要对每个单元单独施加保护罩,进行保护并形成空腔,从而实现封装。25.可见,现有技术的mems传感器和asic芯片的封装方式中,需要对每个单元单独施加保护罩,这样会存在加工效率低和成本高等问题;且施加保护罩的方式,存在加工精密程度差,无法满足高密度封装的发展需求等问题,还存在封装体积大,无法满足半导体封装短小轻薄的发展需求等问题。26.基于此,本技术实施例提供了塑封空腔结构制作方法,通过在嵌埋封装基板顶部加工铜柱围墙,封装后可形成塑封空腔,能够在一定程度上解决现有的塑封空腔结构需要对每个单元单独施加保护罩,加工效率低和成本高;加工精密程度差,无法满足高密度封装的发展需求等;封装体积大,无法满足半导体封装短小轻薄的发展需求等的问题。27.图2示出了本技术实施例提供的塑封空腔结构的剖面图。28.如图2所示,本技术实施例提供的塑封空腔结构,可以包括嵌埋封装框架、嵌埋在所述嵌埋封装框架内的芯片组和围设在嵌埋封装框架下表面的塑封层300。其中,芯片组包括层叠设置的第一芯片210和第二芯片220,且所述第一芯片210和所述第二芯片220的端子相背设置。29.塑封空腔结构包括沿高度方向分别贯穿形成所述嵌埋封装框架的绝缘层的第一空腔和第一导通柱102。芯片组设置在所述第一空腔内,还包括设置在所述芯片组与所述第一空腔的间隙内的封装层400;设置在所述嵌埋封装框架上表面的第一线路层500和第二导通柱600;设置在所述第一线路层500上的第一介质层700和第二线路层800;还包括依次贯穿所述第一介质层700和所述嵌埋封装框架的绝缘层的通孔103。30.还包括设置在所述嵌埋封装框架下表面的第三线路层和围绕嵌埋封装框架的下表面设置的支撑柱围墙310;其中,第三线路层可以包括功能线路层910和线路围墙920,支撑柱围墙310可以对应设置在线路围墙920上。也即在所述第三线路层上设置支撑柱围墙。设置在所述第三线路层下表面的被动元件250;设置在所述嵌埋封装框架的下表面及所述第三线路层和所述支撑柱围墙310的外侧的塑封层300;也即沿所述支撑柱围墙外侧形成塑封层300。所述塑封层300与所述嵌埋封装框架的下表面之间具有与所述通孔103连通的第二空腔340。31.应当理解的是,芯片组可以设置为多个,根据实际的需求具体确定即可。对应地,第一空腔可以设置为多个,分别用于嵌埋多个芯片组。而塑封层300与封装基板的下表面之间形成的第二空腔340,能够覆盖所有的芯片组,从而实现形成高密度集成封装。32.本技术实施例提供的塑封空腔结构,通过将层叠设置的第一芯片210和第二芯片220组成的芯片组堆叠嵌埋封装于封装基板内部,通过封装层400的盲孔实现与封装基板的电连接,并在嵌埋封装基板顶部(也即下表面)加工铜柱围墙,封装后可形成塑封空腔;能够实现高密度集成封装,具有高的精密度,且封装体积小型化和封装效率高等优点。33.在一些实施例中,嵌埋封装框架为聚合物框架。框架可由作为聚合物片材应用的聚合物或者可以由作为预成型体(prepreg)应用的玻璃纤维增强聚合物构成。它可具有一个或多个层。34.本实施方案提及的导通柱(例如第一导通柱102或第二导通柱600)可以包括至少一个铜通孔柱作为io通道,以实现层与层之间的导通,多个导通柱的尺寸和/或形状可以相同,也可以不同。导通柱可以为实心铜柱,也可以是表面镀铜的空心柱;优选,导通柱包括多个铜通孔柱作为io通道,导通柱的端部可以与包封层平齐。35.在所述芯片组中,第一芯片210可以为传感芯片(例如mems传感芯片),具有多个端子211和一个传感部件212。且第一芯片210的端子面贴装在所述第一空腔的底部。其中,传感部件212的表面外露,也即传感部件的表面并未被第三线路层覆盖。也即,所述第一芯片的传感部件表面暴露于所述第二空腔,通过所述通孔与外界连通。这样,传感芯片可以通过第二空腔340和通孔103感受外界环境载荷,然后输出电信号至第二芯片220。36.第二芯片220与第一芯片210之间可以通过粘性材料230连接。且第二芯片220的尺寸(例如长度)可以小于第一芯片210和粘性材料230,而粘性材料230的尺寸可以与第一芯片210的相同。该粘性材料230的黏度可以大于封装层400的黏度,这样可以避免封装层400太硬导致的压合至粘性材料230时,对芯片造成的损坏等。第二芯片220可以为asic芯片,asic芯片能够将mems芯片输出的电信号放大、调制为所需的标准输出信号。37.在一些实施例中,还包括设置在所述塑封层300与所述第三线路层和所述支撑柱围墙310之间的第二介质层350。也即,所述塑封层300与所述第二空腔之间还包括第二介质层。所述第二介质层350可以为覆型膜。覆型膜可以为聚四氟乙烯(ptfe)膜或者聚酰亚胺(pi)薄膜等。这样,通过覆型膜可以更好地对塑封层300进行覆型,并能够高效释放应力。38.在一些实施例中,所述支撑柱围墙310可以为铜支撑柱围墙,这样可以在支撑的同时起到散热的作用。以嵌埋封装框架所在的面为参考面,所述支撑柱围墙310在所述参考面的正投影与所述线路围墙920在所述参考面的正投影部分重叠。39.在一些实施例中,在嵌埋封装框架与第一线路层500之间可以设置有第二金属种子层,在嵌埋封装框架与第三线路层之间还可以设置有第一金属种子层。这样,可以提高第一导通柱102与第一线路层500导通连接的稳定性和可靠性等,提高第一导通柱102与第三线路层导通连接的稳定性和可靠性等。40.在一些实施例中,在第一介质层700和第二线路层800之间还可以设置有第三金属种子层。这样,可以提高第二导通柱600与第一线路层500和第二线路层800之间导通连接的稳定性和可靠性等。41.参照图3a-图3i,示出本技术实施例的塑封空腔结构的制作方法的各个步骤的中间结构的截面示意图。42.所述制造方法包括如下步骤:准备嵌埋封装框架100,所述嵌埋封装框架100包括沿高度方向分别贯穿所述嵌埋封装框架的第一空腔101和第一导通柱102-步骤(a),如图3a。43.通常,可以设置多个第一空腔101用于后续贴装芯片组,多个第一空腔101的尺寸可以相同,也可以不同,根据需要嵌埋的芯片组的形状和大小确定,在此不做限定。嵌埋封装框架100可由作为聚合物片材应用的聚合物或者可以由作为预成型体(prepreg)应用的玻璃纤维增强聚合物构成。它可具有一个或多个层。44.通常,嵌埋封装框架100的制造可以利用珠海越亚的通孔柱技术,进行图案镀覆或面板镀覆,接着进行选择性蚀刻,可以将通孔制造成导通柱,随后利用介电材料如聚合物膜或为了增加稳定性利用聚合物基质中的织造玻璃纤维束构成的预成型体来层压。在一个实施方案中,介电材料是hitachi 705g。在另一实施方案中,采用mgc832 nxa nsflca。在第三实施方案中,可以采用sumitomo gt-k。在另一实施方案中,采用sumitomo laz-4785系列膜。在另一实施方案中,采用sumitomo laz-6785系列。替代材料包括taiyo的hbi和zaristo-125或ajinomoto的abf gx材料系列。45.利用通孔柱而不是钻填技术制造导通柱具有许多优点。在通孔柱技术中,由于所有通孔可以同时制造,而钻填技术需要单独钻孔,所以通孔柱技术更快。此外,由于钻出的通孔都是圆柱形的,而通孔柱可以具有任意形状。实际上,所有钻填的通孔都具有相同的尺寸(在公差范围内),而通孔柱可以具有不同的形状和尺寸。而且,为了增加强度,优选聚合物基质是纤维增强的,典型地利用玻璃纤维织造束来增强。当聚合物内包含纤维的预成型体被敷设在直立的通孔柱上并固化后,通孔柱的特征是具有平滑且垂直的侧面。然而,在对复合材料进行钻孔时,钻填通孔典型地有所倾斜;典型地具有粗糙表面,其引起杂散电感,导致噪声。46.通常,第一导通柱102具有25微米到500微米范围的宽度。如果为原柱形,如钻填所要求以及如在导通柱中常见的那样,每个导通柱可具有25微米到500微米的直径。47.接着,在所述第一空腔101的底部嵌埋芯片组-步骤(b),如图3b。48.通常,步骤(b)中在所述第一空腔101的底部嵌埋芯片组包括:49.(b1)在所述嵌埋封装框架100的下表面上施加粘合层240。通常,粘合层240可以为单面胶带,通常单面胶带为市售的可热分解或可在紫外线照射下分解的透明膜;粘合层240能够对芯片组进行临时支撑和固定。50.(b2)将所述芯片组的第二芯片220的端子面附着在所述第一空腔101内暴露的粘合层240上,以在所述第一空腔101的底部贴装芯片组。其中,所述芯片组包括层叠设置的第一芯片210和所述第二芯片220,且所述第一芯片210和所述第二芯片220的端子面相背设置,且第一芯片210的端子面贴装在第一空腔的底部。通常所述芯片组的高度可以小于所述第一空腔的高度,这样可以通过后续工艺在芯片组上形成封装层400,可以承接在嵌埋封装框架表面制造其他层级结构时,对芯片组施加的负荷,进而避免芯片组的破损等。通常,第一芯片210与第二芯片220的背面可以通过粘性材料230粘结。51.然后,在所述芯片组与所述第一空腔101的间隙内形成封装层400-步骤(c),如图3d所示。通常,该步骤可以包括:52.(c1)在所述芯片组与所述第一空腔101的间隙内及所述嵌埋支撑框架100的上表面上形成封装层400,如图3c。通常,封装层400可以选自纯树脂。53.(c2)减薄所述封装层400暴露所述嵌埋支撑框架100的第一导通柱102的上表面和所述嵌埋封装框架100的上表面,并使所述封装层400的上表面与所述第一导通柱102的上表面和所述嵌埋封装框架100的上表面齐平。这样,可以使得嵌埋封装框架100的上表面具有良好的平整性,避免器件波动起伏引发的加层导通困难,利于后续在嵌埋封装框架100的上表面进行第一线路层500等的制备。通常,可以通过磨板或等离子蚀刻等方式减薄封装材料。54.(c3)对所述第二芯片220的端子进行开窗,在所述封装层400上形成盲孔410。通常,所述盲孔410与所述第二芯片220的端子221相连,以利于第二芯片220与后续制备的第一线路层500等的电连接。这样,可以使得芯片组与封装基板之间的电连接具有高的集成性和稳定性。通常,可以通过镭射钻孔等对第二芯片220的端子进行开窗,形成盲孔410。55.接着,在所述嵌埋封装框架100的上表面形成第一线路层500和第二导通柱600-步骤(d),如图3e所示。通常,步骤(d)包括:56.(d1)在所述嵌埋封装框架100的上表面及所述盲孔410的底部和侧壁上形成第二金属种子层;通常,可以通过溅射工艺形成第二金属种子层。第二金属种子层的材质没有具体限定,根据实际需求确定即可,通常可以为钛和铜。57.(d2)在所述第二金属种子层上施加第三光刻胶层,曝光显影所述第三光刻胶层形成第三特征图案;58.(d3)在所述第三特征图案中电镀形成第一线路层500。通常所述第一线路层500与所述第二芯片220的端子面连接;59.(d4)移除所述第三光刻胶层,在所述第二金属种子层上施加第四光刻胶层,曝光显影所述第四光刻胶层形成第四特征图案;60.(d5)在所述第四特征图案中电镀形成第二导通柱600;通常第二导通柱600与所述第一导通柱102相对应设置;61.(d6)移除所述第三光刻胶层和所述第四光刻胶层,并蚀刻暴露的第二金属种子层。62.然后,在所述第一线路层500的上表面层压第一介质层700-步骤(e),如图3f。通常,步骤(e)包括:63.在所述第一线路层500的上表面层压第一介质材料。通常,所述第一介质材料的高度超过第二导通柱600的高度。这样,可以通过后续的减薄暴露第二导通柱600,利于第二导通柱600端面与第一介质层700的齐平,便于后续的层级结构的制作等。64.减薄所述第一介质材料暴露所第二导通柱600的上表面(端面),形成上表面与所述导通柱的上表面齐平的第一介质层700。通常,可以通过磨板或等离子蚀刻等方式减薄第一介质材料。65.接着,在所述第一介质层700的上表面形成第二线路层800,并在所述嵌埋封装框架的下表面形成第三线路层和围绕嵌埋封装框架设置的支撑柱围墙310-步骤(f),如图3g。通常,步骤(f)中在所述第一介质层700的上表面形成第二线路层800包括:66.(f1)在所述第一介质层700的上表面形成第三金属种子层;通常,可以通过溅射工艺形成第三金属种子层。第三金属种子层的材质没有具体限定,根据实际需求确定即可,通常可以为钛和铜;67.(f2)在所述第三金属种子层上施加第五光刻胶层,曝光显影所述第五光刻胶层形成第五特征图案;68.(f3)在所述第五特征图案中电镀形成第二线路层800;所述第二线路层800通过所述第二导通柱600与所述第一线路层500连接;69.(f4)移除所述第五光刻胶层,并蚀刻暴露的第三金属种子层。70.通常,步骤(f)中,在所述嵌埋封装框架的下表面形成第三线路层和围绕嵌埋封装框架设置的支撑柱围墙310包括:71.(f5)移除嵌埋封装框架的下表面上施加的粘合层240;72.(f6)在所述嵌埋封装框架的下表面形成第一金属种子层;通常,可以通过溅射工艺形成第一金属种子层。第一金属种子层的材质没有具体限定,根据实际需求确定即可,通常可以为钛和铜;73.(f7)在所述第一金属种子层上施加第一光刻胶层,曝光显影所述第一光刻胶层形成第一特征图案;74.(f8)在所述第一特征图案中电镀形成第三线路层;所述第三线路层可以包括功能线路层910和线路围墙920,支撑柱围墙310可以对应设置在线路围墙920上;其中,第一芯片210的传感部件212的表面外露,也即传感部件的表面并未被第三线路层覆盖。75.(f9)移除所述第一光刻胶层,在所述第一金属种子层上施加第二光刻胶层,曝光显影所述第二光刻胶层形成第二特征图案;76.(f10)在所述第二特征图案中电镀形成支撑柱围墙310,如图3h。通常,所述支撑柱围墙310可以为铜支撑柱围墙310,这样可以在支撑的同时起到散热的作用。以嵌埋封装框架所在的面为参考面,所述支撑柱围墙310在所述参考面的正投影与所述线路围墙920在所述参考面的正投影部分重叠。77.(f11)移除所述第二光刻胶层,并蚀刻暴露的第一金属种子层。78.然后,形成沿高度方向依次贯穿所述第一介质层700和所述嵌埋封装框架的通孔103,形成具有所述芯片组的第一封装结构和不具有芯片组的第二封装结构-步骤(g),如图3i。通常可以通过机械钻孔等方式形成通孔103,通过该通孔103,该第一芯片210(也即传感芯片)可以感受外界环境载荷,然后输出电信号至第二芯片220。79.接着,在所述第二封装结构的下表面贴装被动元件250;在所述嵌埋封装框架的下表面及所述线路围墙920和所述支撑柱围墙310的外侧形成塑封层300-步骤(h),如图2。通常,被动元件250可以贴装在第三线路层中的功能线路层910的下表面。80.通常,在所述嵌埋封装框架的下表面及所述线路围墙920和所述支撑柱围墙310的外侧形成塑封层300包括:81.在所述嵌埋封装框架的下表面及所述线路围墙920和所述支撑柱围墙310的外侧层压第二介质层350,形成容纳所述被动元件250的第二空腔340。这样,芯片组中的第一芯片210(也即mems传感芯片)可以通过第二空腔340和通孔103感受外界环境载荷,然后输出电信号至第二芯片220(也即asic芯片)。asic芯片将mems芯片输出的电信号放大、调制为所需的标准输出信号。通常,第二介质层350可以为覆型膜。采用覆型膜能够起到保护和隔离的作用。且使得塑封层300具有高的透明度和平滑性,具有耐温性和耐候性和抗静电性能等。82.在所述第二介质层350的表面层压塑封层300。83.本技术实施例提供的塑封空腔结构及其制作方法,通过将mems传感芯片和asic芯片堆叠嵌埋封装于封装基板内部,实现高密度集成封装;嵌埋封装基板顶部加工铜柱围墙,封装后可形成塑封空腔;mems传感芯片的传感部位外露,通过塑封空腔结构以及贯穿基板的孔实现与外部环境的传感。从而解决现有技术中低效率、高成本、精密程度差、封装体积无法小型化等技术问题。具有能够实现mems传感芯片与asic芯片的高密度集成封装;通过面板级加工塑封空腔结构,提升加工效率、降低成本;通过设置铜柱围墙,压合覆型膜并封装后形成塑封空腔,相比保护罩形成的空腔,加工精密程度更高,可满足高密度集成封装的需求等优点。84.所属领域的普通技术人员应当理解:以上任何实施例的讨论仅为示例性的,并非旨在暗示本公开的范围(包括权利要求)被限于这些例子;在本公开的思路下,以上实施例或者不同实施例中的技术特征之间也可以进行组合,步骤可以以任意顺序实现,并存在如上所述的本公开实施例的不同方面的许多其它变化,为了简明它们没有在细节中提供。85.尽管已经结合了本公开的具体实施例对本公开进行了描述,但是根据前面的描述,这些实施例的很多替换、修改和变型对本领域普通技术人员来说将是显而易见的。86.本公开实施例旨在涵盖落入所附权利要求的宽泛范围之内的所有这样的替换、修改和变型。因此,凡在本公开实施例的精神和原则之内,所做的任何省略、修改、等同替换、改进等,均应包含在本公开的保护范围之内。

本文地址:https://www.jishuxx.com/zhuanli/20240726/123895.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

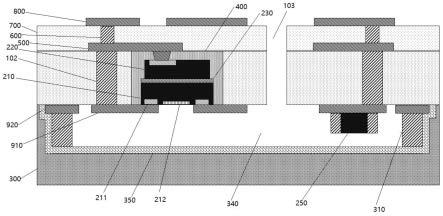

返回列表