一种基于WLP工艺的MEMS磁通门传感器的制作方法与流程

- 国知局

- 2024-07-27 12:53:39

本发明涉及微型传感器,尤其涉及一种基于wlp工艺的mems磁通门传感器的制作方法。

背景技术:

1、传统的磁通门传感器使用一个坚固的骨架作为基座,将软磁薄膜磁芯固定在基座上,然后在磁芯上缠绕一个通过电流产生磁场的激励线圈,和一个在激励线圈诱发磁场基础上检测外部磁场效应的磁场感应线圈。这种传统的磁通门传感器存在工作温度范围有限、体积大、重量大、灵敏度低、功耗高和长期稳定性差等缺点,难以满足电子元器件微型化的需求。

2、mems工艺技术的出现为微型化磁通门传感器的制备提供了一条有效可靠的路径。mems磁通门传感器包括激励线圈、感应线圈和软磁薄膜磁芯三个关键部分。通过mems工艺技术不仅可以减小磁通门传感器的体积和重量,还可以有效降低功耗和提高灵敏度等,从而实现芯片尺寸磁通门传感器的制作。mems磁通门传感器是磁性传感器中一类重要的基础性弱磁探测器件,其广泛应用于工业自动化、航空航天、汽车、电力输运等各种民用、军用设备中,在设备中主要用来实现地磁导航、电流检测、深空探测、倾角测量、转速测试等功能。

3、对于mems磁通门传感器,目前主要的工艺为电镀工艺技术,其工艺流程如下图1所示。利用多层电镀的方式制备mems磁通门传感器。采用电镀的方式制备下层铜线圈,之后旋涂一层聚酰亚胺绝缘层材料,隔离铜线圈和磁芯材料,磁芯材料采用磁控溅射的方式制备,最后再用电镀的方式制备上层铜线圈。

4、这种电镀工艺具有制作工艺流程复杂,生产成本较高,长期稳定性较差以及与磁芯材料的匹配度较低等缺点,难以保证mems磁通门传感器的整体性能。即这种传统电镀工艺的工艺流程复杂,包括电镀、旋涂、刻蚀以及打磨抛光等,并且制备的层数越多导致器件制备难度越大,成功率难以保证。因此,需要对mems磁通门传感器的制作工艺进行改进,以满足器件的可靠性要求,拓宽器件的应用场景。

5、现有公开号为cn 107367288 a 的中国专利申请,公开了一种微型磁通门传感器制备方法,该方法是先键合硅基片,在填充线圈材料,之后通过开槽、密封的方式放置磁芯材料,这种方法对磁芯材料的结构有所限制,且该方法无法准确判断磁芯材料位置是否放置妥当,存在后期与器件匹配度较差等问题。而本发明是先在磁芯槽中放置好磁芯材料,再通过键合、填充线圈材料的方式制备mems磁通门传感器。

技术实现思路

1、本发明的目的就在于提供一种基于wlp工艺的mems磁通门传感器的制作方法,以解决上述问题。

2、为了实现上述目的,本发明采用的技术方案是这样的:一种基于wlp工艺的mems磁通门传感器的制作方法,包括下述步骤:

3、(1)选择硅基片,并对硅基片进行减薄处理,其厚度为280-420 μm,然后至少在其中一个硅基片的第一表面刻蚀磁芯槽;

4、需要说明的是:本技术中,为了后续键合过程中便于区分贴合的表面,发明人将刻蚀有磁芯槽的硅基片表面定义为第一表面,在同一个硅基片上刻蚀有多条横跨磁芯的感应线圈槽的表面定义为第二表面;

5、相互键合的两个硅基片中,可以在两个硅基片上均刻蚀磁芯凹槽,也可以只用在其中一个硅基片上刻蚀磁芯凹槽,只需刻蚀的尺寸满足磁芯材料即可;

6、(2)在硅基片第二表面刻蚀多条横跨磁芯的感应线圈槽,然后刻蚀多条横跨磁芯的激励线圈槽,沿硅基片厚度方向,在每个线圈槽两端垂直刻蚀多条与线圈槽连通的通孔,在硅基片第二表面刻蚀与线圈槽或者通孔相连通的电极窗口;

7、(3)在所述磁芯槽表面、感应线圈槽、激励线圈槽内表面以及通孔内表面晶圆裸露在外的部分沉积一层二氧化硅绝缘层;通过沉积二氧化硅绝缘层实现隔离磁芯材料和铜导线的目的;

8、(4)对硅基片进行清洗;

9、(5)对硅基片表面进行活化处理;

10、(6)将软磁薄膜放置在磁芯槽中;

11、(7)键合过程:将两个硅基片的第一表面贴合在一起,使得两个硅基片上的磁芯槽对合形成磁芯腔,并且各线圈和通孔之间连通形成围绕在磁芯腔外周围的螺线管腔,将圆片对在惰性气体气氛中进行退火,温度在200-400℃范围内,使键合界面的原子间形成牢固的键合力,实现键合过程;

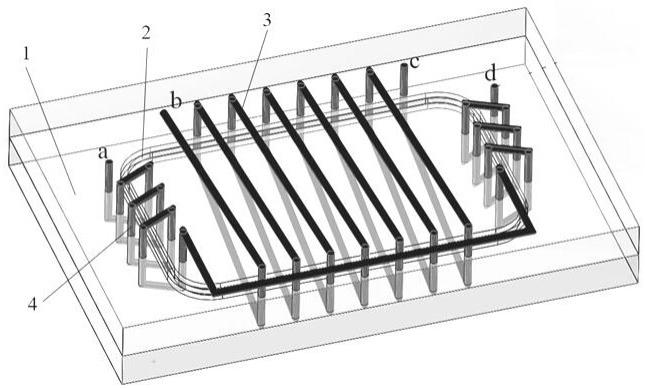

12、(8)电镀铜:采用“自底向上”的电镀方式在螺线管腔内填充铜,形成激励线圈和感应线圈,即得。

13、本技术中,磁芯形状可以是跑道型,还可以包含环形、矩形等,如图6所示,图6中从左至右分别为环形磁芯结构、跑道型磁芯结构和矩形磁芯结构,这几种结构的磁芯材料在灵敏度、噪声、零漂及稳定性等方面均具有较大的优势,也是目前主流研究或商业磁通门产品中使用较为广泛的几种磁芯结构。

14、本发明简化了传统电镀方式制备磁通门传感器的步骤,本发明所采用的方法主要依靠tsv技术,即硅通孔技术,根据魏红军等人的文献“tsv制程关键工艺设备技术及发展”,该技术具有高密度集成、提高电性能以及降低成本等的优势。本发明采用tsv技术,是三维堆叠芯片实现互连的关键工艺技术,该技术具有集成密度高和成本等优点。相对于公开号为cn 107367288 a的专利申请,本发明所采用的方法具有步骤简单,能根据磁芯材料的形状(例如环行、矩形或者跑道型磁芯材料)刻蚀磁芯槽,并且磁芯材料与器件本身匹配度较好等优点

15、发明人通过大量试验发现,高温键合存在的问题:(1)过高的温度会对 ic和 mems器件产生不利影响,对于某些温敏器件而言,甚至会使其破坏而失效;(2)高温键合时常常会产生一定的热应力,在完成键合冷却后热应力无法释放,会造成 mems 器件工作不稳定和可靠性降低;(3)如果界面存在一些污染和缺陷,在高温的作用下会扩散开,使产品失效区域变得不可控。因此,工艺温度在 400℃以下的低温键合技术对于器件性能的改善至关重要。

16、本发明先分别在两个硅基片上刻蚀出能够放置磁芯的凹槽和在键合后围绕在磁芯外周围的螺线管腔以及与线圈相连的电极窗口,两个硅基片在键合前,在放置磁芯凹槽的腔体位置沉积绝缘层;在两个硅基片螺线管腔的内表面沉积绝缘层,并在腔体内填充线圈材料,从而使其形成螺线管线圈;将两个硅基片相对的表面进行处理,之后将两个硅基片面对面贴合在一起,两键合表面通过表面分子或者氢键的作用力连接在一起进行键合。

17、作为优选的技术方案:步骤(1)中,采用深度离子刻蚀法进行刻蚀,刻蚀的磁芯槽的宽度为300 μm ,长度为900 μm,厚度为20 μm。

18、作为优选的技术方案:步骤(2)中,采用深度离子刻蚀法刻蚀感应线圈槽和激励线圈槽,所述感应线圈槽宽度为50 μm,厚度为50 μm,长度为400 μm;所述激励线圈槽宽度为50 μm,厚度为50 μm,长度为70 μm;采用硅通孔技术(即tsv)刻蚀所述通孔,通孔的尺寸为φ50 μm,深度为300 μm,所述电极窗口,尺寸为φ50 μm。采用tsv技术,提高硅基衬底上下层导体材料的信号互连作用,实现减小尺寸和降低损耗的目的。

19、作为优选的技术方案:步骤(3)中,所述沉积方法为通过热氧化的方法沉积,所述二氧化硅绝缘层的厚度为,厚度为200nm。

20、作为优选的技术方案:步骤(4)中,所述清洗方法为:依次使用丙酮、无水乙醇、酸性双氧水、盐酸和双氧水混合溶液超声清洗基片,之后用氮气枪吹干硅基片。

21、作为优选的技术方案:步骤(5)中,所述活化处理的方法为利用湿法活化的方法对硅基片表面进行活化处理:依次使用去离子水、rca-1溶液、 热去离子水和冷去离子水处理硅基片,之后用氮气枪吹干基片。

22、硅基片表面活化处理也可以使用等离子体干法活化或者湿法活化和等离子体干法活化相结合的方法。

23、作为优选的技术方案:步骤(7)中,在室温和一定压力作用下进行键合。为了保证mems磁通门传感器的可靠性,这里采用在室温条件下进行键合,后期在400℃以下的范围内进行退火处理。

24、作为优选的技术方案:步骤(8)中,电镀铜前先沉积一层ti、tiw或者cr种子层,厚度为10~200 nm。可以提高铜的附着力,但需要满足键合后形成的通孔的tsv(硅通孔)工艺要求。

25、作为优选的技术方案,所述软磁薄膜材料采用nife合金薄膜和fe基、co基非晶/纳米晶薄膜等金属软磁材料,或采用yig、nizn铁氧体软磁材料。磁芯材料的选择与磁通门传感器的设计要求有关,磁环的加工可以采用多种方法,如传统机械加工、电镀、激光切割等。

26、需要说明的是:所用的磁芯材料的厚度一般在几微米到几十微米之间,并且磁芯优选具有高相对磁导率、低矫顽力和低磁致伸缩的软磁性材料,因此磁通门所用磁芯材料也为软磁薄膜材料,即本发明中所述的“磁芯材料”亦即“软磁薄膜材料”。

27、与现有技术相比,本发明的优点在于:本发明采用wlp工艺制作mems磁通门传感器,能够达到简化工艺流程的目的,采用tsv技术能进一步提高连接通孔的成功率和线圈互连可靠性,采用刻槽放置磁芯的方法,能减少后期固化绝缘聚合物等材料对磁芯性能的伤害,采用低温键合的方式减小高温键合对器件产生的不良影响,提高器件的工作稳定性和可靠性,也能达到减小器件尺寸的目的,上述方案保证了mems磁通门传感器的整体性能。

本文地址:https://www.jishuxx.com/zhuanli/20240726/123999.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表