一种集成反应键合体系及制备方法与流程

- 国知局

- 2024-07-27 12:56:53

本技术涉及微电子和微机电系统,具体涉及一种集成反应键合体系及制备方法,利用局域热源实现微米尺度键合。

背景技术:

1、微机电系统是将微机械元件、传感元件、信号处理元件及执行元件集成于一体的微系统。随着微机电系统的发展,封装和键合的要求也越来越苛刻。用于微机电器件的常用键合技术有直接键合、阳极键合、共晶键合键合。在上述三种键合技术中,较高温度、较大压力都是实现良好连接的必要工艺参数,需要将微机电器件整体进行加热处理,而温度敏感的微系统极易受到上述键合工艺的损害。因此研究局域热源、低损伤键合技术对微机电系统具有重要意义。

2、采用微米尺度局域热源技术是解决上述问题的有效方法。

3、反应纳米多层膜是一种新结构形式的纳米含能材料,一般由能够发生混合放热反应的a/b两种材料交替层叠排列组成。两种材料的原子充分混合生成中间化合物,释放大量的热,反应释放的热量加速附近原子的混合,可形成自蔓延传播。在外加能量的激励下,反应多层膜可进行自蔓延反应,放热瞬间可获得上千度的高温可融化钎料,同时借助反应产物实现材料的连接。反应多层膜快速升温、快速降温(毫秒)的特点使其可作为微米尺度局域热源,由于热量影响区域限制在表界面区域,不会对器件或部件的整体产生热影响。

4、从形态上看,反应多层膜分为自支撑膜和附着基体膜两类。自支撑多层膜的厚度在几十微米范围,已经较为成熟的用于宏观物体的连接,如金属/陶瓷连接、金属/金属连接等,利用其自蔓延放热作为钎焊的热源。但在微电子、微机电系统等微米尺度的场合,应用自支撑纳米多层膜需要根据形状和尺寸进行裁切,实现微尺度连接并不方便。因此将反应多层膜沉积在基片上并利用其自蔓延反应放热实现微米尺度连接框架的焊接,是实现微系统封装和键合的重要发展方向,该技术也被称为集成反应键合技术,所用纳米多层膜被称为集成反应多层系统。

5、集成反应多层系统的厚度一般在若干微米,并且其工艺可集成到微电子和微机电系统的微纳加工流程中。

6、从结构上看,当前应用的反应多层膜都是平行于基片交替排列。平行基片排列的优点是制备方便。采用磁控溅射或电子束蒸发镀膜技术交替沉积两种组元,可方便的控制每一层的厚度和微观结构,获得周期和总厚度可调的反应多层膜。

7、但本技术发现,反应多层膜平行于基片设置还存在很多缺点。首先在沉积过程中粒子都携带一定的能量,造成两组元界面原子的互混,形成化合物互混层。互混层消耗了纳米多层膜的能量,降低反应体系的放热量。其次在随着厚度增加,热量累积效应显著,可能发生伴随沉积过程的同步自反应,即已经沉积的两组元发生混合放热反应,造成制备后的反应多层膜降低甚至失去放热能力。这种情况在导热性较差的基片上常常出现,比如在si片上沉积反应多层膜时,当超过临界厚度(~1μm)时往往发生沉积同步自反应。在导热性较好的基片上沉积时该效应可一定程度的减弱。但在随后的点燃过程中,激励能量会被导热性较好的基片耗散,导致点燃困难甚至无法点燃,即使能够点燃反应多层膜,由于热量耗散导致无法持续反应,失去自蔓延效应。因此在基片上沉积反应多层膜存在这样一个矛盾,即导热性差的基片容易导致沉积同步自反应,导热性好的基片往往点燃困难或反应不持续。再次采用磁控溅射制备的纳米多层膜往往具有较大的内应力,以往的研究表明厚度>5μm的薄膜容易因内应力过大而从基片剥离。因此通过增加厚度来增大放热量以实现自持续放热也是困难的。

8、综上所述,集成反应多层膜体系可作为微米尺度局部热源,用于微系统的封装和键合,但组元平行于基片的方式存在较大困难。

技术实现思路

1、为了解决本领域存在的上述不足,本技术旨在提供一种集成反应键合体系及制备方法,采用组元垂直于基片的方式制备集成反应膜体系。

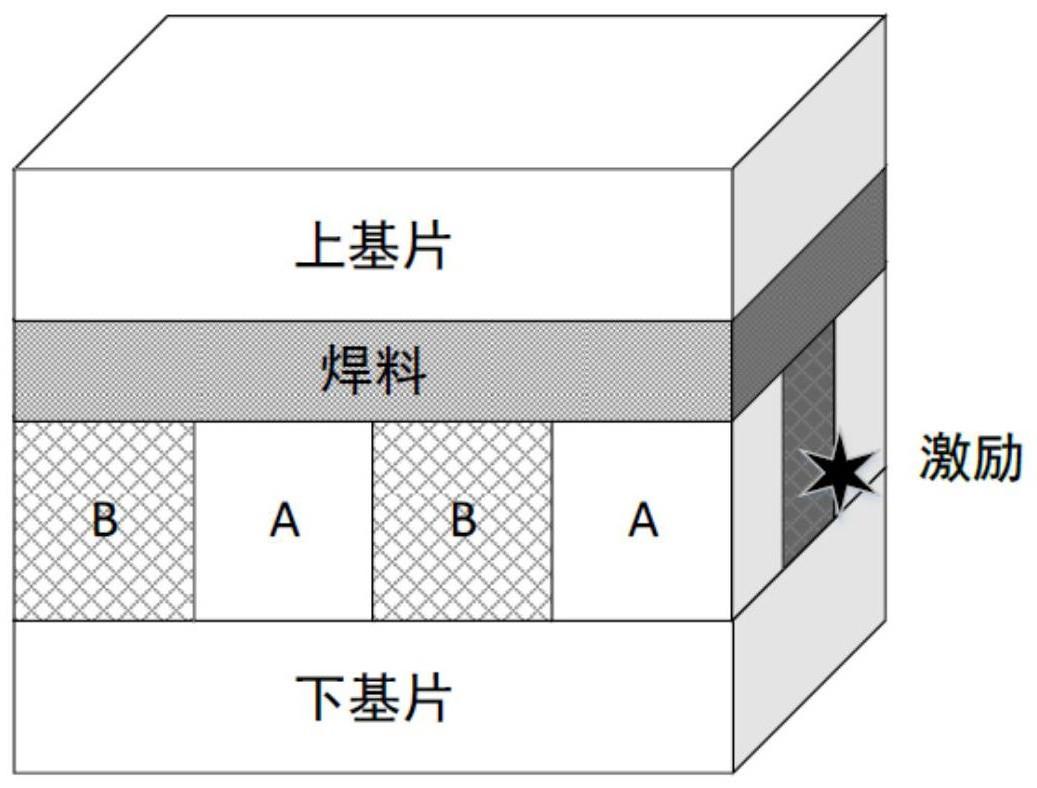

2、根据本技术的一方面,提供一种集成反应键合体系,包括:上基片、反应放热系统和下基片;

3、其中,所述反应放热系统包括至少两种组元;

4、所述至少两种组元的接触面垂直设置于上基片和下基片之间;

5、所述至少两种组元具有底端和开放端;

6、所述底端附着于所述下基片表面;

7、所述至少两种组元的侧面互相接触。

8、根据本技术的一些实施例,所述组元呈柱状。

9、根据本技术的一些实施例,所述组元的高度相同或不同;

10、所述组元的宽度相同或不同。

11、根据本技术的一些实施例,所述组元的宽度为200~1000nm;所述组元高度100nm~5微米。

12、根据本技术的一些实施例,所述组元为两组时,第一组元的材料选自铝、碳、硅中的任一种;

13、第二组元的材料选自钛、锆、铪、钒、铌、钽、镍、钯、铂中的任一种。

14、根据本技术的一些实施例,所述组元为两种以上时,除第一组元和第二组元以外的其他组元材料选自铝、碳、硅、钛、锆、铪、钒、铌、钽、镍、钯、铂、铟、锡、铅中的任一种;

15、其中,所述第一组元、第二组元与所述其他组元不同时为一种材料。

16、根据本技术的一些实施例,至少两种组元之间的混合焓<0。

17、根据本技术的一些实施例,当含有三组组元且第三组元材料选择铟、锡、铅中的一种时,第三组元所占比例不超过总组元的50%。

18、根据本技术的另一方面,提供一种上述的集成反应键合体系的制备方法,包括:

19、采用刻蚀工艺或剥离工艺制备垂直于下基片表面的第一组元的周期结构;

20、采用离子束刻蚀去除所述第一组元的表面氧化层;

21、采用磁控溅射或电子束蒸发沉积工艺,在所述第一组元周期结构的间隙区域制备第二组元;以及

22、在制备完成的所述第一组元和所述第二组元上方覆盖上基片;

23、或,

24、采用刻蚀工艺或剥离工艺制备垂直于下基片表面的第一组元的周期结构;

25、采用离子束刻蚀去除所述第一组元的表面氧化层;

26、采用微纳加工刻蚀或剥离工艺制备垂直于下基片表面的第二组元的周期结构;

27、采用磁控溅射或电子束蒸发沉积工艺,在所述第一、二组元周期结构的间隙区域制备第三组元,重复该步骤制备其他组元;以及

28、在制备完成的所述第一组元、所述第二组元和所述第三组元上方覆盖上基片。

29、与现有技术相比,本技术至少包括如下有益效果:

30、本技术提供一种集成反应键合体系,包括:上基片、反应放热系统和下基片;其中,所述反应放热系统包括至少两种组元,并垂直于上下基片之间。上述反应键合体系作为热源,易点燃,放热稳定,不产生形成界面原子互混导致热量减低的问题。特别适合于半导体、mems等微系统中导热性较差的基片上集成热源。通过改变组元比例,调整体系放热量,实现片上器件的低温、低应力键合。

31、本技术还提供一种集成反应键合体系的制备方法,该方法操作简便,不易产生热量堆积。不会因热量累积效应而发生伴随沉积过程的同步自反应,可避免制备后的反应多层膜降低甚至失去放热能力的问题。

本文地址:https://www.jishuxx.com/zhuanli/20240726/124300.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表