一种PMUT接收阵列的制备方法和系统

- 国知局

- 2024-07-27 12:57:54

本申请实施例涉及集成电路微纳系统和3d成像应用,具体涉及一种pmut接收阵列的制备方法和系统。

背景技术:

1、三维(3d)成像设备在手势技术、物体识别与跟踪技术、场景检测等领域应用广泛。其结构通常由发射基阵单元,接收基阵单元和系统化集成电路单元构成,通过信号采集、传输和显控等过程实现。

2、目前,作接收阵或发射阵的被广泛使用的高频换能器主要采用压电陶瓷作为单元,具有体积大、不易加工、难集成、低带宽等缺点,限制了3d成像设备的成像精度。基于微机电系统mems技术的大带宽压电微型超声换能器pmut阵列是近些年兴起的一种新型超声换能器技术。借助于半导体加工技术以及薄膜弯曲振动的谐振模态的优势,使其具有高一致性、大带宽、易小尺寸系统化集成等特点,因此具有解决以上传统超声换能器接收阵列问题的潜在优势。

3、然而,基于mems技术的大带宽pmut接收阵的研究和制备技术尚不成熟,是目前该领域亟待解决的研究难题。

技术实现思路

1、为此,本申请实施例提供一种pmut接收阵列的制备方法和系统,能够实现大带宽pmut接收阵的制备,有助于提高现有三维成像设备分辨率和成像精度。

2、为了实现上述目的,本申请实施例提供如下技术方案:

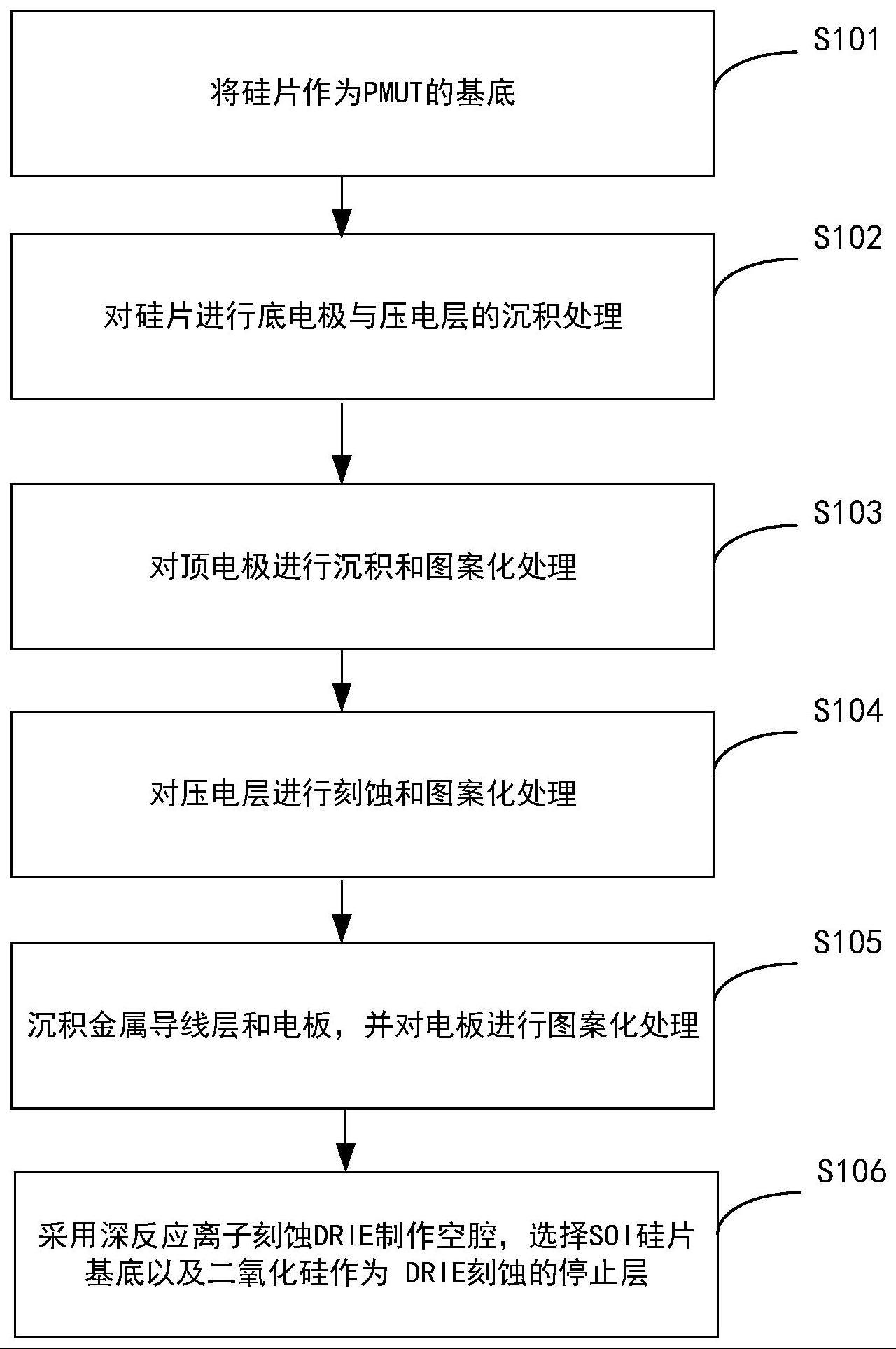

3、根据本申请实施例的第一方面,提供了一种pmut接收阵列的制备方法,所述方法包括:

4、将硅片作为pmut的基底;

5、对硅片进行底电极与压电层的沉积处理;

6、对顶电极进行沉积和图案化处理;

7、对压电层进行刻蚀和图案化处理;

8、沉积金属导线层和电板,并对电板进行图案化处理;

9、采用深反应离子刻蚀drie制作空腔,选择soi硅片基底以及二氧化硅作为drie刻蚀的停止层。

10、可选地,所述对硅片进行底电极与压电层的沉积处理包括:

11、基于scaln压电薄膜材料进行薄膜沉积,选择aln作为薄膜沉积的种子层,以及mo作为电极层,通过湿法刻蚀scaln暴露底电极作为电信号连接。

12、可选地,基于scaln压电薄膜材料进行薄膜沉积,包括:

13、选择晶格匹配的底电极与压电层,优化衬底、种子层、缓冲层,进行scaln压电薄膜的沉积。

14、可选地,所述对顶电极进行沉积和图案化处理,包括:

15、选择图形化的光刻胶作为膜版,对顶电极进行金属薄膜沉积、以及光刻胶剥离。

16、可选地,所述底电极的沉积处理方法包括:磁控溅射、电子束蒸镀和电镀;

17、所述压电层的沉积处理方法包括磁控溅射和溶胶凝胶;

18、所述顶电极的图案化处理方法包括剥离和刻蚀;

19、所述压电层的图案化处理方法包括刻蚀。

20、根据本申请实施例的第二方面,提供了一种pmut接收阵列的制备系统,所述系统包括:

21、基底模块,用于将硅片作为pmut的基底;

22、底电极与压电层沉积模块,用于对硅片进行底电极与压电层的沉积处理;

23、顶电极沉积模块,用于对顶电极进行沉积和图案化处理;

24、压电层模块,用于对压电层进行刻蚀和图案化处理;

25、导线电板沉积模块,用于沉积金属导线层和电板,并对电板进行图案化处理;

26、空腔模块,用于采用深反应离子刻蚀drie制作空腔,选择soi硅片基底以及二氧化硅作为drie刻蚀的停止层。

27、可选地,所述底电极与压电层沉积模块,用于:

28、基于scaln压电薄膜材料进行薄膜沉积,选择aln作为薄膜沉积的种子层,以及mo作为电极层,通过湿法刻蚀scaln暴露底电极作为电信号连接。

29、可选地,所述底电极与压电层沉积模块,具体用于:

30、选择晶格匹配的底电极与压电层,优化衬底、种子层、缓冲层,进行scaln压电薄膜的沉积。

31、根据本申请实施例的第三方面,提供了一种电子设备,包括:存储器、处理器及存储在所述存储器上并可在所述处理器上运行的计算机程序,所述处理器运行所述计算机程序时执行以实现上述第一方面所述的方法。

32、根据本申请实施例的第四方面,提供了一种计算机可读存储介质,其上存储有计算机可读指令,所述计算机可读指令可被处理器执行以实现上述第一方面所述的方法。

33、综上所述,本申请实施例提供了一种pmut接收阵列的制备方法和系统,通过将硅片作为pmut的基底;对硅片进行底电极与压电层的沉积处理;对顶电极进行沉积和图案化处理;对压电层进行刻蚀和图案化处理;沉积金属导线层和电板,并对电板进行图案化处理;采用深反应离子刻蚀drie制作空腔,选择soi硅片基底以及二氧化硅作为drie刻蚀的停止层。能够实现大带宽pmut接收阵的制备,有助于提高现有三维成像设备分辨率和成像精度。

技术特征:1.一种pmut接收阵列的制备方法,其特征在于,所述方法包括:

2.如权利要求1所述的方法,其特征在于,所述对硅片进行底电极与压电层的沉积处理包括:

3.如权利要求2所述的方法,其特征在于,基于scaln压电薄膜材料进行薄膜沉积,包括:

4.如权利要求1所述的方法,其特征在于,所述对顶电极进行沉积和图案化处理,包括:

5.如权利要求1所述的方法,其特征在于,所述底电极的沉积处理方法包括:磁控溅射、电子束蒸镀和电镀;

6.一种pmut接收阵列的制备系统,其特征在于,所述系统包括:

7.如权利要求6所述的系统,其特征在于,所述底电极与压电层沉积模块,用于:

8.如权利要求7所述的系统,其特征在于,所述底电极与压电层沉积模块,具体用于:

9.一种电子设备,包括:存储器、处理器及存储在所述存储器上并可在所述处理器上运行的计算机程序,其特征在于,所述处理器运行所述计算机程序时执行以实现如权利要求1-5任一项所述的方法。

10.一种计算机可读存储介质,其特征在于,其上存储有计算机可读指令,所述计算机可读指令可被处理器执行以实现如权利要求1-5任一项所述的方法。

技术总结本申请实施例公开了一种PMUT接收阵列的制备方法和系统,所述方法包括:将硅片作为PMUT的基底;对硅片进行底电极与压电层的沉积处理;对顶电极进行沉积和图案化处理;对压电层进行刻蚀和图案化处理;沉积金属导线层和电板,并对电板进行图案化处理;采用深反应离子刻蚀DRIE制作空腔,选择SOI硅片基底以及二氧化硅作为DRIE刻蚀的停止层。能够实现大带宽PMUT接收阵的制备,有助于提高现有三维成像设备分辨率和成像精度。技术研发人员:卢奕鹏,郑磊,赵雷,杨冲受保护的技术使用者:北京大学技术研发日:技术公布日:2024/1/15本文地址:https://www.jishuxx.com/zhuanli/20240726/124382.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表