具有绝缘层的微机械超声换能器及制造方法与流程

- 国知局

- 2024-07-27 13:03:26

背景技术:

1、本公开涉及可用于医学背景中的半导体和微机电系统(mems)技术,例如,mems超声换能器。

2、微机械超声换能器(mut)在许多领域中提供巨大潜力,包括但不限于医疗成像、空气耦合成像、距离监测、指纹监测、非破坏性缺陷监测、背面照明、生物mems以及诊断。串扰是mut经常面临的问题。

3、在mems装置中,绝缘体上硅(soi)基底的使用已变得更加普遍。soi晶片使得能够制造在消费者、汽车、工业和医疗应用中使用的最先进的mems、互补金属氧化物半导体(cmos)、功率和射频(rf)部件。soi晶片在可用于设计若干mems装置的高质量二氧化硅层(埋入氧化物或box)上提供高质量单晶硅层。soi晶片提供对能够设计和制造独特的装置配置的若干材料参数的精确控制。

4、尽管有这些优点,常规的soi晶片技术面临挑战,其中几何结构的精确控制需要先进mems装置,该先进的mems装置需要与cmos电路进行三维(3d)竖直集成。这些挑战已经通过使用双soi技术得到缓解,该双sio技术将两个soi基底分层。

技术实现思路

1、双soi技术还可改善各种微机电系统(mems)装置(诸如包括压电mut(pmut)和电容mut(cmut)的微机械超声换能器(mut))的功能。双soi技术的使用可以使设计者能够更灵活地对在装置的埋入氧化物(box)和半导体层中蚀刻的腔(或波导)和沟槽定尺寸和定位置。因此,双soi设计可以改善声波传输(例如,通过增加波输出功率)并减少串扰。

2、此外,本文所公开的多soi工艺可以在蚀刻mut装置中的沟槽和腔的工艺期间实现更好的临界尺寸控制,从而增强设计灵活性。此外,多soi工艺可以提供更精确的对准容差,从而减轻对准误差的影响。

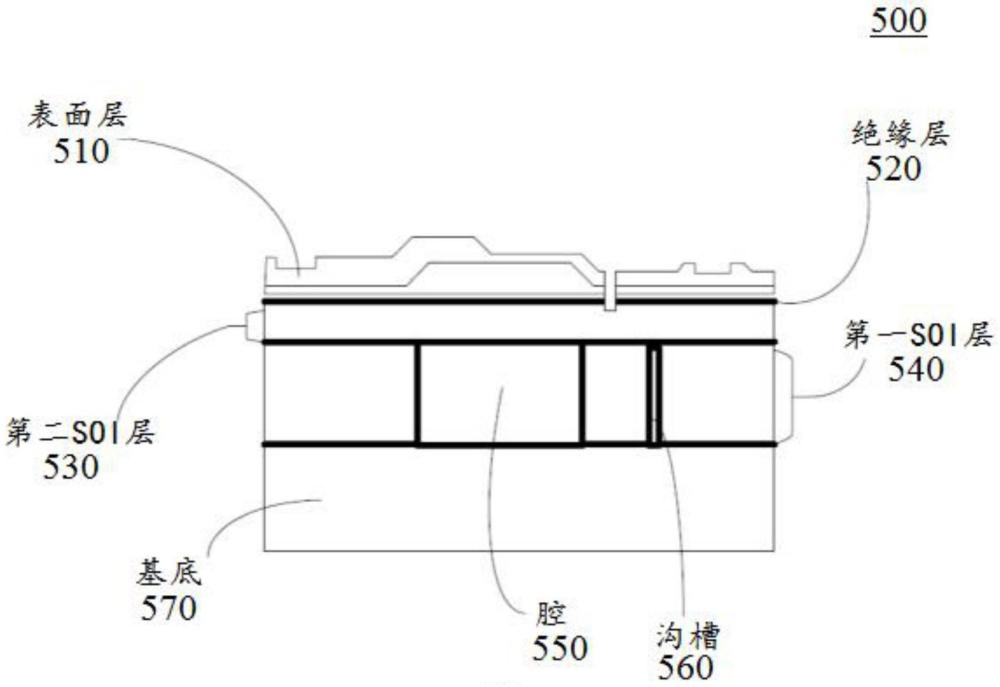

3、在一些方面中,公开了一种多绝缘体上硅(soi)微机械超声换能器(mut)装置。该装置包括多soi基底。该装置还包括具有膜的mut。该装置还公开了mut附着于多soi基底的表面。该装置还公开了多soi基底包括第一soi层以及设置在第一soi层上方的至少第二soi层,第一soi层和第二soi层各自包括绝缘层和半导体层。第一soi层还包括位于mut的膜下方的腔。一个或多个沟槽至少部分地围绕该腔的周边。

4、在一些实施例中,mut是压电微机械超声换能器(pmut)。

5、在一些实施例中,mut是电容式微机械超声换能器(cmut)。

6、在一些实施例中,第二soi层的高度为40微米-80微米。

7、在一些实施例中,绝缘层是埋入氧化物(box)层。

8、在一些实施例中,box层的高度是1微米-5微米。

9、在一些实施例中,第一soi层和至少第二soi层的半导体层是处理层(handlelayer);其中腔通过蚀刻处理层和box层中的至少一者而产生。

10、在一些实施例中,装置包括硅通孔。

11、在一些实施例中,半导体层是硅膜层。

12、在一些实施例中,多soi基底是双soi基底。

13、在一些实施例中,腔包括沉积的氧化物层。

14、在一些实施例中,沟槽被蚀刻至跨越装置的一个或多个层的深度。

15、在一些实施例中,装置还包括在第一soi层下方的处理层。

16、在一些实施例中,处理层是半导体层。

17、在一些实施例中,第二soi层的半导体层包括金属涂层。

18、在一些实施例中,腔填充有气体。

19、在一些实施例中,腔包含真空。

20、在一些实施例中,绝缘层包括非氧化物绝缘体。

21、在一个方面中,公开了一种多绝缘体上硅(soi)微机械超声换能器(mut)阵列。阵列包括多soi基底。阵列还包括各自具有膜的多个mut。多个mut附着于多soi基底的表面。多soi基底包括设置在第一soi层上方的第二soi层,第一soi层和第二soi层各自均包括绝缘层和半导体层。第一soi层还包括多个腔,每个腔位于多个mut中的mut的膜下方。第一soi层还包括至少部分地围绕多个mut的多个腔中的腔的周边的一个或多个沟槽。

22、在一个方面中,提供了制造双绝缘体上硅(soi)微机械超声换能器(mut)阵列的方法。该方法包括通过蚀刻第一soi层的氧化物层以包含至少一个沟槽的宽度来在第一soi层中限定至少一个沟槽。该方法还包括将光致抗蚀剂层施加到第一soi层的氧化物层。该方法还包括通过对光致抗蚀剂层和氧化物层进行图案蚀刻以包含腔的宽度来在第一soi层中限定腔。该方法还包括蚀刻腔和至少一个沟槽。该方法还包括将氧化物层施加到腔和至少一个沟槽。

23、通过引用并入

24、在本说明书中提及的所有出版物、专利和专利申请均通过引用并入本文,其程度与每个单独的出版物、专利或专利申请被明确且单独地指示通过引用并入的程度相同。

技术特征:1.一种多绝缘体上硅(soi)微机械超声换能器(mut)装置,包括:

2.根据权利要求1所述的装置,其中,所述mut是压电微机械超声换能器(pmut)。

3.根据权利要求1所述的装置,其中,所述mut是电容式微机械超声换能器(cmut)。

4.根据权利要求1所述的装置,其中,所述第二soi层的高度为40微米-80微米。

5.根据权利要求1所述的装置,其中,所述绝缘层是埋入氧化物(box)层。

6.根据权利要求5所述的装置,其中,所述box层的高度是1微米-5微米。

7.根据权利要求5所述的装置,其中,所述第一soi层的所述半导体层和至少所述第二soi层的所述半导体层是处理层;其中,所述腔通过蚀刻所述处理层和所述box层中的至少一者而产生。

8.根据权利要求1所述的装置,还包括硅通孔。

9.根据权利要求1所述的装置,其中,所述半导体层是硅膜层。

10.根据权利要求1所述的装置,其中,所述多soi基底为双soi基底。

11.根据权利要求1所述的装置,其中,所述腔包括沉积的氧化物层。

12.根据权利要求1所述的装置,其中,所述沟槽被蚀刻至跨越所述装置的一个或多个层的深度。

13.根据权利要求1所述的装置,还包括在所述第一soi层下方的处理层。

14.根据权利要求13所述的装置,其中,所述处理层是半导体层。

15.根据权利要求1所述的装置,其中,所述第二soi层的所述半导体层包括金属涂层。

16.根据权利要求1所述的装置,其中,所述腔填充有气体。

17.根据权利要求1所述的装置,其中,所述腔包含真空。

18.根据权利要求1所述的装置,其中,所述绝缘层包括非氧化物绝缘体。

19.一种多绝缘体上硅(soi)微机械的超声换能器(mut)阵列,包括:

20.一种制造双绝缘体上硅(soi)微机械超声换能器(mut)阵列的方法,包括:

技术总结公开了一种多绝缘体上硅(SOI)微机械超声换能器(MUT)装置。该装置包括多SOI基底和MUT。MUT附着于多SOI基底的表面。该多SOI基底具有第一SOI层以及设置在第一SOI层上方的至少第二SOI层。第一SOI层和第二SOI层各自包括绝缘层和半导体层。第一SOI层进一步限定位于MUT的膜下方的腔以及至少部分地围绕腔的周边的一个或多个沟槽。技术研发人员:纳雷什·曼特拉瓦第,权·海成,布莱恩·伯德姆肖受保护的技术使用者:EXO成像公司技术研发日:技术公布日:2024/3/24本文地址:https://www.jishuxx.com/zhuanli/20240726/124721.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。