全氮化镓集成的电压基准电路和电压基准电路控制方法与流程

- 国知局

- 2024-07-30 09:21:35

本发明涉及集成电路,尤其涉及一种全氮化镓集成的电压基准电路和电压基准电路控制方法。

背景技术:

1、在电子系统中,通常需要一个可靠的电压基准来确保其他电路和组件的正常工作,电压基准电路可以用于提供稳定、准确的电压参考。传统的silicon电压基准电路通常采用标准双极性晶体管和互补式金属氧化物半导体(bipolar junction transistor andcomplementary metal-oxide-semiconductor,bicmos)工艺或双极性晶体管、互补式金属氧化物半导体和双扩散金属氧化物半导体(bipolar junction transistor,complementary metal-oxide-semiconductor and double-diffused metal-oxide-semiconductor,bcd)工艺,δvbe(base-emitter voltage,基极发射极电压)呈正温系数,vbe呈负温系数。然而,传统silicon工艺的电压基准电路无法适用极高温度应用场景,例如汽车电子场景(200℃)。

2、在gan电压基准电路采用的工艺中,depletion mode(d-mode)器件的阈值的负值是负温系数,enhancement mode(e-mode)器件的阈值是正温系数。然而,gan工艺的电压基准电路对工艺要求较高,e mode器件和d mode器件的阈值温度系数比值有较高要求,若相差较大,会导致电路内组成的电流环失效,使得基准两条支路的电流不相等,进而导致基准无法保持零温。

技术实现思路

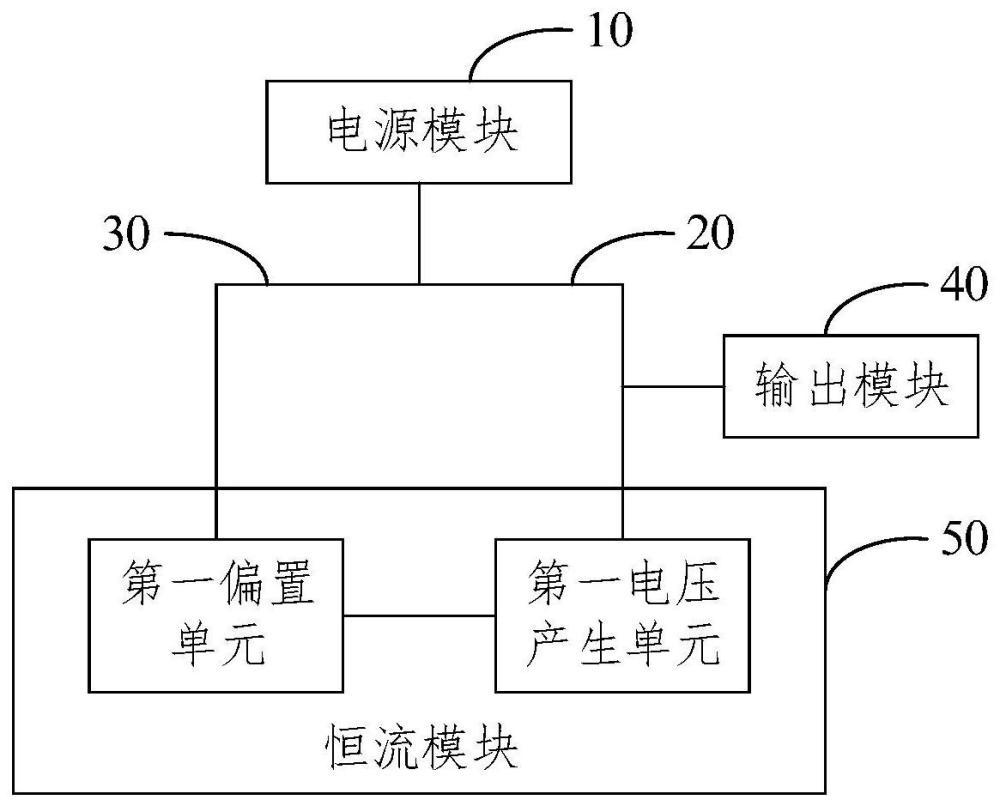

1、针对现有技术存在的问题,本发明提供一种全氮化镓集成的电压基准电路,包括:电源模块、第一基准支路、第二基准支路和输出模块,所述第一基准支路包括第一偏置单元,所述第二基准支路包括第一电压产生单元,所述第一偏置单元与所述第一电压产生单元连接组成恒流模块;

2、所述电源模块,用于提供所述第一基准支路和所述第二基准支路的输入电流;

3、所述恒流模块,用于保持所述第一基准支路和所述第二基准支路的输入电流相等;

4、所述输出模块接入所述第二基准支路,用于输出基准电压。

5、根据本发明提供的一种全氮化镓集成的电压基准电路,所述第二基准支路还包括调整单元,所述调整单元一端与所述第一偏置单元连接,另一端与所述第一电压产生单元连接,所述输出模块的一端接入设置在所述调整单元和所述第一电压产生单元之间的第一连接端;

6、所述第一电压产生单元,用于产生负温电压;

7、所述第一偏置单元,用于为所述第一电压产生单元提供偏置电流;

8、所述调整单元,用于保持所述基准电压稳定。

9、根据本发明提供的一种全氮化镓集成的电压基准电路,所述调整单元包括第一增强型氮化镓器件,所述第一偏置单元包括第一电阻和第二增强型氮化镓器件,所述第一增强型氮化镓器件的栅极通过所述第一电阻与所述第二增强型氮化镓器件的漏极连接。

10、根据本发明提供的一种全氮化镓集成的电压基准电路,所述第一电压产生单元包括第二电阻、第三增强型氮化镓器件和第一连接线,所述第一增强型氮化镓器件的源极通过所述第二电阻与所述第三增强型氮化镓器件的漏极连接,所述第三增强型氮化镓器件的栅极与所述第二增强型氮化镓器件的栅极连接,所述第一连接线的一端接入设置在所述第二电阻与所述第三增强型器件的漏极之间的第二连接端,另一端接入设置在所述第三增强型氮化镓器件的栅极与所述第二增强型氮化镓器件的栅极之间的第三连接端,所述输出模块的一端接入设置在所述第一增强型氮化镓器件的源极与所述第二电阻之间的第一连接端。

11、根据本发明提供的一种全氮化镓集成的电压基准电路,所述电路还包括接地模块,所述第三增强型氮化镓器件的源极和所述第二增强型氮化镓器件的源极接入所述接地模块。

12、根据本发明提供的一种全氮化镓集成的电压基准电路,所述第一基准电路还包括第二偏置单元,所述第二基准电路还包括第二电压产生单元,所述第二偏置单元和所述第二电压产生单元分别接入所述电源模块的输出端;

13、所述第二电压产生单元,用于产生正温电压;

14、所述第二偏置单元,用于为所述第二电压产生单元提供偏置电流。

15、根据本发明提供的一种全氮化镓集成的电压基准电路,所述第二电压产生单元包括第三电阻、第一耗尽型氮化镓器件和第一电容,所述第一耗尽型氮化镓器件的漏极接入所述电源模块的输出端,所述第一耗尽型氮化镓器件的栅极通过所述第一电容与所述第一增强型氮化镓器件的漏极连接,所述第一耗尽型氮化镓器件的源极通过所述第三电阻与所述第一增强型氮化镓器件的漏极连接。

16、根据本发明提供的一种全氮化镓集成的电压基准电路,所述第二偏置单元包括第二耗尽型氮化镓器件和第二电容,所述第二耗尽型氮化镓器件的漏极与所述电源模块的输出端连接,所述第二耗尽型氮化镓器件的栅极依次通过所述第二电容、所述第一电阻与所述第二增强型氮化镓器件的漏极连接,所述第二耗尽型氮化镓器件的源极通过设置在所述第一电阻与所述第二电容之间的第四连接端与所述第一增强型氮化镓器件的栅极连接。

17、本发明还提供一种电压基准电路控制方法,所述方法用于控制如上所述的全氮化镓集成的电压基准电路,所述方法包括:

18、在温度变化时,调整所述第二电阻和所述第三电阻的比值,控制输出的基准电压达到零温。

19、根据本发明提供的一种电压基准电路控制方法,所述调整所述第二电阻和所述第三电阻的比值,包括:

20、调整所述第二电阻和所述第三电阻的比值为增强型器件和耗尽型器件阈值电压温度的变化率的比值。

21、本发明还提供一种电子设备,包括存储器、处理器及存储在所述存储器上并可在所述处理器上运行的计算机程序,所述处理器执行所述程序时实现如上述任一项所述的电压基准电路控制方法的步骤。

22、本发明还提供一种非暂态计算机可读存储介质,其上存储有计算机程序,所述计算机程序被处理器执行时实现如上述任一项所述的电压基准电路控制方法的步骤。

23、本发明实施例提供的全氮化镓集成的电压基准电路不带电流环,通过设置第一基准支路上的第一偏置单元和第二基准支路上的第一电压产生单元连接组成恒流模块,可以通过恒流模块使得第一基准支路和第二基准支路的输入电流保持相等,进而避免基准无法保持零温的问题,并且本发明提供的全氮化镓集成的电压基准电路对工艺要求较低,可以应用在更宽范围温度条件。

技术特征:1.一种全氮化镓集成的电压基准电路,其特征在于,包括:电源模块、第一基准支路、第二基准支路和输出模块,所述第一基准支路包括第一偏置单元,所述第二基准支路包括第一电压产生单元,所述第一偏置单元与所述第一电压产生单元连接组成恒流模块;

2.根据权利要求1所述的电路,其特征在于,所述第二基准支路还包括调整单元,所述调整单元一端与所述第一偏置单元连接,另一端与所述第一电压产生单元连接,所述输出模块的一端接入设置在所述调整单元和所述第一电压产生单元之间的第一连接端;

3.根据权利要求2所述的电路,其特征在于,所述调整单元包括第一增强型氮化镓器件,所述第一偏置单元包括第一电阻和第二增强型氮化镓器件,所述第一增强型氮化镓器件的栅极通过所述第一电阻与所述第二增强型氮化镓器件的漏极连接。

4.根据权利要求3所述的电路,其特征在于,所述第一电压产生单元包括第二电阻、第三增强型氮化镓器件和第一连接线,所述第一增强型氮化镓器件的源极通过所述第二电阻与所述第三增强型氮化镓器件的漏极连接,所述第三增强型氮化镓器件的栅极与所述第二增强型氮化镓器件的栅极连接,所述第一连接线的一端接入设置在所述第二电阻与所述第三增强型器件的漏极之间的第二连接端,另一端接入设置在所述第三增强型氮化镓器件的栅极与所述第二增强型氮化镓器件的栅极之间的第三连接端,所述输出模块的一端接入设置在所述第一增强型氮化镓器件的源极与所述第二电阻之间的第一连接端。

5.根据权利要求4所述的电路,其特征在于,所述电路还包括接地模块,所述第三增强型氮化镓器件的源极和所述第二增强型氮化镓器件的源极接入所述接地模块。

6.根据权利要求4所述的电路,其特征在于,所述第一基准电路还包括第二偏置单元,所述第二基准电路还包括第二电压产生单元,所述第二偏置单元和所述第二电压产生单元分别接入所述电源模块的输出端;

7.根据权利要求6所述的电路,其特征在于,所述第二电压产生单元包括第三电阻、第一耗尽型氮化镓器件和第一电容,所述第一耗尽型氮化镓器件的漏极接入所述电源模块的输出端,所述第一耗尽型氮化镓器件的栅极通过所述第一电容与所述第一增强型氮化镓器件的漏极连接,所述第一耗尽型氮化镓器件的源极通过所述第三电阻与所述第一增强型氮化镓器件的漏极连接。

8.根据权利要求7所述的电路,其特征在于,所述第二偏置单元包括第二耗尽型氮化镓器件和第二电容,所述第二耗尽型氮化镓器件的漏极与所述电源模块的输出端连接,所述第二耗尽型氮化镓器件的栅极依次通过所述第二电容、所述第一电阻与所述第二增强型氮化镓器件的漏极连接,所述第二耗尽型氮化镓器件的源极通过设置在所述第一电阻与所述第二电容之间的第四连接端与所述第一增强型氮化镓器件的栅极连接。

9.一种电压基准电路控制方法,其特征在于,所述方法用于控制如权利要求7-8中任一项所述的全氮化镓集成的电压基准电路,所述方法包括:

10.根据权利要求9所述的方法,其特征在于,所述调整所述第二电阻和所述第三电阻的比值,包括:

11.一种电子设备,包括存储器、处理器及存储在所述存储器上并可在所述处理器上运行的计算机程序,其特征在于,所述处理器执行所述程序时实现如权利要求9至10任一项所述的电压基准电路控制方法。

12.一种非暂态计算机可读存储介质,其上存储有计算机程序,其特征在于,所述计算机程序被处理器执行时实现如权利要求9至10任一项所述的电压基准电路控制方法。

技术总结本发明涉及集成电路技术领域,提供一种全氮化镓集成的电压基准电路和电压基准电路控制方法,该电路包括:电源模块、第一基准支路、第二基准支路和输出模块,所述第一基准支路包括第一偏置单元,所述第二基准支路包括第一电压产生单元,所述第一偏置单元与所述第一电压产生单元连接组成恒流模块;所述电源模块,用于提供所述第一基准支路和所述第二基准支路的输入电流;所述恒流模块,用于保持所述第一基准支路和所述第二基准支路的输入电流相等;所述输出模块接入所述第二基准支路,用于输出基准电压。本发明提供的全氮化镓集成的电压基准电路不带电流环,通过设置恒流模块使得基准两条支路的输入电流保持相等,避免基准无法保持零温的问题。技术研发人员:孙汉萍,严慧,李思超受保护的技术使用者:英诺赛科(珠海)科技有限公司技术研发日:技术公布日:2024/7/18本文地址:https://www.jishuxx.com/zhuanli/20240730/149182.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表