一种高精度的授时精度测量系统的制作方法

- 国知局

- 2024-07-30 09:31:00

1.本实用新型属于时间统一技术领域,特别是涉及一种高精度的授时精度测量系统。背景技术:2.时间统一系统是通过无线或有线信道对航天、军工、工业和民用等领域的测量系统、控制系统的各种设备进行授时,为各种设备提供统一的标准时间信号(以下简称“时码信号”)和标准的频率信号(以下简称“频标信号”)。提供标准时码、频标信号的设备一般统称为时统设备,接收标频时码、频标信号的设备一般统称用时设备。3.时统设备的性能优劣直接影响测控系统的测量精度,如果没有统一的时间标准,用时设备测量时间的时刻、记录的测量数据价值急剧降低。因此,授时精度测量的关键问题为:简便、高精度测量时统设备授时精度。4.目前时统设备授时精度主要的检验方法是将时间基准输出秒脉冲信号(以下简称“pps”)作为示波器的触发信号,时统设备输出的pps接入示波器其它通道,利用示波器余晖功能测量时统设备的授时精度。发明人发现现有技术存在以下问题:5.(1)测量设备一致性影响授时精度:批量生产的时统设备在检验环节严重依赖示波器等测量设备的精度、一致性,固定资产的投入降低现金流,测量设备的集中、长期使用存在一定的安全隐患;6.(2)检验效率低:常规的示波器通道数一般为4-5个,测量效率低;7.(3)示值误差影响授时精度:受示波器设置及时间刻度的限制,测量结果准确读数相对困难,准确度偏低;8.(4)缺少检验过程数据,不利于时统设备的改进、问题分析的数据支撑。技术实现要素:9.本实用新型的目的在于克服现有技术的一项或多项不足,提供一种高精度的授时精度测量系统。10.本实用新型的目的是通过以下技术方案来实现的:一种高精度的授时精度测量系统,包括:11.fpga单元,用于接收外部输入的基准pps信号和时统pps信号,并将基准pps信号输出至第一时间数字转换器,将时统pps信号输出至第二时间数字转换器,以及产生本地pps信号,并将本地pps信号输出至第一时间数字转换器和第二时间数字转换器;12.第一时间数字转换器,与所述fpga单元连接,用于测量所述基准pps信号和本地pps信号之间的第一相位差,并输出所述第一相位差;13.第二时间数字转换器,与所述fpga单元连接,用于测量所述时统pps信号和本地pps信号之间的第二相位差,并输出所述第二相位差;14.微处理器,与所述fpga单元、第一时间数字转换器和第二时间数字转换器连接,用于根据所述第一相位差和所述第二相位差得到基准pps信号和时统pps信号之间的相位差;15.恒温晶振,与所述fpga单元和微处理器连接,用于为fpga单元和微处理器提供工作时钟。16.优选的,所述授时精度测量系统还包括上位机,所述上位机与所述微处理器通信连接。17.优选的,所述上位机与所述微处理器之间采用串口连接。18.优选的,所述第一时间数字转换器的型号为tdc-gp21,所述第一时间数字转换器的start端与fpga单元的本地pps信号输出端连接,所述第一时间数字转换器的stop1端与fpga单元的基准pps信号输出端连接。19.优选的,所述第二时间数字转换器的型号为tdc-gp21,所述第二时间数字转换器的start端与fpga单元的本地pps信号输出端连接,所述第二时间数字转换器的stop1端与fpga单元的一个时统pps信号输出端连接,所述第二时间数字转换器的stop1端与fpga单元的一个时统pps信号输出端连接。20.优选的,所述第二时间数字转换器的数量为一个或多个。21.优选的,所述第一时间数字转换器的输出端与微处理器的一个spi通信接口连接,每个所述第二时间数字转换器的输出端分别与微处理器的一个spi通信接口连接。22.优选的,所述微处理器的一个spi通信接口与fpga单元的一个spi通信接口连接。23.本实用新型的有益效果是:24.(1)本实用新型中的授时精度测量系统可以通过增加第二时间数字转换器的数量来实现多个时统pps信号精度的同时测量,扩展性好;25.(2)本实用新型中通过微处理器驯服恒温晶振,间接测量基准pps信号和时统pps信号的相位差(即授时精度),有效的提高了测量精度,解决了传统授时精度测量严重依赖硬件设备、检验效率低、示值误差的影响、缺少过程数据的痛点。附图说明26.图1为本实用新型中授时精度测量系统的一个实施例的示意框图。具体实施方式27.下面将结合实施例,对本实用新型的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域技术人员在没有付出创造性劳动的前提下所获得的所有其他实施例,都属于本实用新型保护的范围。28.参阅图1,本实施例提供了一种高精度的授时精度测量系统:29.如图1所示,一种高精度的授时精度测量系统,包括fpga单元、恒温晶振、第一时间数字转换器、第二时间数字转换器和微处理器。30.所述恒温晶振的第一时钟端与fpga单元时钟端连接,所述恒温晶振的第二时钟端与微处理器的时钟端连接,所述恒温晶振用于为fpga单元和微处理器提供工作时钟。31.所述fpga单元的基准pps信号输入端用于接收外部输入的基准pps信号,所述fpga单元的时统pps信号输入端用于接收外部输入的时统pps信号,所述fpga单元的本地pps信号输出分别与所述第一时间数字转换器的第一输入端和第二时间数字转换器的第一输入端连接,所述fpga单元的基准pps信号输出端与所述第一时间数字转换器的第二输入端连接,所述fpga单元的时统pps信号输出端与所述第二时间数字转换器的第二输入端连接,所述fpga单元还与微处理器通信连接。所述fpga单元用于接收外部输入的基准pps信号和时统pps信号,并将基准pps信号输出至第一时间数字转换器,将时统pps信号输出至第二时间数字转换器,以及产生本地pps信号,并将本地pps信号输出至第一时间数字转换器和第二时间数字转换器。32.在一个实施例中,fpga单元检测基准pps信号和时统pps信号的有无,并将检测结果通过spi总线通知微处理器,并将基准pps信号映射到第一时间数字转换器的stop1端口和微处理器,将时统pps信号映射到第二时间数字转换器的stop1端口和/或stop2端口。33.在一个实施例中,fpga单元产生本地pps信号的过程为:fpga单元获取微处理器输出的初始pps信号,利用本地恒温晶振产生的标频信号对初始pps信号进行打拍处理得到本地pps信号,然后将本地pps信号输出至第一时间数字转换器、第二时间数字转换器和微处理器。34.在一个实施例中,所述恒温晶振的驯服过程为:微处理器基于基准pps信号对恒温晶振进行驯服,其过程是通过第一时间数字转换器实时测量基准pps信号与本地pps信号的相位差,微处理器通过内置的dac单元输出压控信号给恒温晶振,调整恒温晶振的相位和频率,使本地pps信号的相位无限逼近基准pps信号的相位,当两者的相位差在设定时间内收敛至设定范围内时,则判定恒温晶振锁定,所述设定收敛时间及设定范围由参考源、驯服算法等决定,本实施例不涉及对恒温晶振驯服过程的改进。35.本实施例中fpga单元的时统pps信号输入端和时统pps信号输出端可以有多个,此时第二时间数字转换器的数量也为多个,每个第二时间数字转换器的第二输入端分别与fpga单元的一个时统pps信号输出端连接,从而可以同时接收并输出多个时统pps信号,从而实现多个时统pps信号的精度测量,从而提高了测量效率。一般的,所述fpga单元的时统pps信号输入端和时统pps信号输出端的数量相同,一个时统pps信号输出端对应一个时统pps信号输入端。36.所述第一时间数字转换器的第一输入端与fpga单元的本地pps信号输出端连接,所述第一时间数字转换器的第二输入端与fpga单元的基准pps信号输出端连接,所述第一时间数字转换器接收fpga单元输出的本地pps信号和基准pps信号,并测量所述本地pps信号和基准pps信号的相位差,记为第一相位差。在一个实施例中,所述第一时间数字转换器的型号为tdc-gp21,所述第一时间数字转换器的start端与fpga单元的本地pps信号输出端连接,所述第一时间数字转换器的stop1端与fpga单元的基准pps信号输出端连接。37.所述第二时间数字转换器的第一输入端与fpga单元的本地pps信号输出端连接,所述第二时间数字转换器的第二输入端与fpga单元的时统pps信号输出端连接,所述第二时间数字转换器接收fpga单元输出的本地pps信号和时统pps信号,并测量所述本地pps信号和时统pps信号的相位差,记为第二相位差。在一个实施例中,所述第二时间数字转换器的型号为tdc-gp21,所述第二时间数字转换器的start端与fpga单元的本地pps信号输出端连接,所述第二时间数字转换器的stop1端与fpga单元的一个时统pps信号输出端连接,所述第二时间数字转换器的stop1端与fpga单元的一个时统pps信号输出端连接,第二时间数字转换器的每个相差输出端与微处理器的一个第二相差输入端连接。所述第二时间数字转换器的数量为一个或多个,从而可以实现多个时统pps信号与基准pps信号之间相位差的同时测量,从而提高了测量效率。38.所述微处理器的第一相差输入端与第一时间数字转换器的输出端连接,所述微处理器的第二相差输入端与第二时间数字转换器的输出端连接,所述微处理器用于接收第一时间数字转换器输出端的第一相位差和第二时间数字转换器输出的第二相位差,并根据所述第一相位差和第二相位差得到基准pps信号和时统pps信号之间的相位差。当第二时间数字转换器有多个时,每个第二时间数字转换器的输出端分别与微处理器的一个第二相差输入端连接。39.在一个实施例中,所述授时精度测量系统还包括上位机,所述上位机可以采用pc机等,所述上位机与所述微处理器通信连接,上位机用于接收基准pps信号和时统pps信号的相位差测量结果,以及将该测量结果进行显示和存储。一般的,所述上位机与所述微处理器之间采用串口连接。40.在一个实施例中,所述第一时间数字转换器的输出端与微处理器的一个spi通信接口连接,每个所述第二时间数字转换器的输出端分别与微处理器的一个spi通信接口连接,所述微处理器的一个spi通信接口与fpga单元的一个spi通信接口连接。41.本实施例中的微处理器、fpga单元和恒温晶振等器件为一般意义的器件,无专用器件,采用现有相关市售产品即可。42.以上所述仅是本实用新型的优选实施方式,应当理解本实用新型并非局限于本文所披露的形式,不应看作是对其他实施例的排除,而可用于各种其他组合、修改和环境,并能够在本文所述构想范围内,通过上述教导或相关领域的技术或知识进行改动。而本领域人员所进行的改动和变化不脱离本实用新型的精神和范围,则都应在本实用新型所附权利要求的保护范围内。

本文地址:https://www.jishuxx.com/zhuanli/20240730/149733.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

一种多功能圭表的制作方法

下一篇

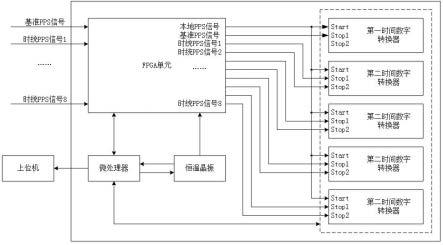

返回列表