一种用于时间数字转换器的延迟链译码器的装置和方法与流程

- 国知局

- 2024-07-30 09:34:20

1.本技术属于数字集成电路设计技术领域,具体涉及一种用于时间数字转换器的延迟链译码器的装置和方法。背景技术:2.时间数字转换器(tdc)是一种将待测时间间隔转换为数字编码的电路,被广泛应用于激光雷达测距、混合信号处理和生物医学成像等各种领域。随着各个领域计数的发展进步,对tdc的分辨率、转换速率等性能提出了越来越高的要求。tdc也从第一代发展到现在的第三代。3.第一代tdc以参考时钟周期为标准进行时间测量,典型结构为计数型tdc,其测量范围大,转换速率快;但分辨率受时钟频率限制,最高只能达到几百皮秒,且功耗大。第二代tdc以单个门延迟为标准进行时间测量,典型结构为延迟链型tdc,也称为快闪型tdc。这一类型的tdc转换速率快,分辨率也提高到了十几到几时皮秒,但是测量范围受延迟链长度限制。改进的循环延迟链型tdc扩大了测量范围,有效解决了测量范围受限地问题。第三代tdc泛指达到亚门级分辨率的tdc,种类繁多。两个典型代表为游标延迟链型tdc和流水线型tdc;前者将游标方法和延迟链相结合获得亚门级分辨率,但测量范围受电路复杂度限制明显;后者在延迟链的基础上加入时间放大器,时间分辨率由流水线级数、时间放大器放大倍数和单个延迟单元延迟时间共同决定。4.近年来tdc结构趋于多样化,但从第二代,第三代tdc的结构中可以看出,很大一部分高分辨率tdc都是基于延迟链进行设计改进的。为了实现性能较好的tdc,各种架构中的延迟链一半采用几十甚至上百个延迟单元,因而从延迟单元上采样获得的机器码位数多,数据量大,使得译码时间长,译码电路复杂,从而影响后续数据处理,减小tdc转换速率。技术实现要素:5.本技术提出了一种用于时间数字转换器的延迟链译码器,旨在解决从tdc中延迟链上采样获得的机器码译码时间长,译码电路复杂的问题,简化译码逻辑,降低毛刺产生的概率,提高tdc转换速率,减小误码率。6.为实现上述目的,本技术提供了如下方案:7.一种用于时间数字转换器的延迟链译码器的装置,8.包括:数据采集模块,数据预处理模块,独热码产生模块和独热码译码模块;9.所述数据采集模块是用于获取指定位数待测试机器码数据;10.所述数据预处理模块是用于基于所述指定位数待测试机器码数据进行预处理,将待测试机器码数据转换成温度计码;11.所述独热码产生模块是用于基于所述温度计码,通过独热码处理将所述温度计码转换成独热码;12.所述独热码译码模块是用于基于所述独热码,通过独热码译码处理将所述独热码转换成二进制码。13.优选的,所述数据预处理模块将待测试机器码数据转换成温度计码的方法包括:将所述指定位数待测试机器码数据分为奇数单元和偶数单元,通过三输入与门将待测试机器码数据转换成温度计码。14.优选的,所述独热码处理模块将所述温度计码转换成独热码的方法包括:15.通过非门和两输入与门将所述温度计码转换成独热码。16.优选的,所述独热码译码模块的输出端输出位二进制码。17.为实现上述目的,本技术还提供了一种用于时间数字转换器的延迟链译码器的方法,具体步骤如下:18.基于所述指定位数待测试机器码数据进行预处理,将待测试机器码数据转换成温度计码;19.基于所述温度计码,通过独热码处理将所述温度计码转换成独热码;20.基于所述独热码,通过独热码译码处理将所述独热码转换成二进制码。21.优选的,所述预处理方法包括:将所述指定位数待测试机器码数据分为奇数组和偶数组,通过三输入与门将待测试机器码数据转换成温度计码。22.优选的,所述偶数组生成独热码的高位的方法包括:23.将ring_counter_in[2*(i-(n+3)/2)]、ring_counter_in[2*(i-(n+3)/2)+2]、ring_counter_in[2*(i-(n+3)/2)+4]划分为偶数组生成独热码的高位prepro_code[i],其中i》(n+1)/2,其中ring_counter_in表示:所述指定位数待测试机器码数据。[0024]优选的,所述奇数组生成独热码的低位的方法包括:[0025]将ring_counter_in[2i-3]、ring_counter_in[2i-1]、ring_counter_in[2i+1]划分为奇数组生成独热码的低位prepro_code[i],其中1《i《(i-1)/2。[0026]优选的,所述独热码处理方法包括:[0027]通过非门和两输入与门将所述温度计码转换成独热码。[0028]优选的,所述独热码译码处理方法包括:[0029]通过多路选择器将所述独热码转换成二进制码。[0030]本技术公开了一种用于时间数字转换器的延迟链译码器的装置和方法,本技术的有益效果为:本技术简化了译码逻辑,减小了毛刺产生的概率;同时减小了系统的面积和功耗;且当采样有误差连续采到多个“1”时,译码器仍能正确译码,一定程度上减小了误码率,具有广阔的推广空间和使用价值。附图说明[0031]为了更清楚地说明本技术的技术方案,下面对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。[0032]图1为本技术实施例系统结构示意图;[0033]图2为本技术实施例电路结构示意图;[0034]图3为本技术实施例方法流程示意图。[0035]下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。[0036]为使本技术的上述目的、特征和优点能够更加明显易懂,下面结合附图和具体实施方式对本技术作进一步详细的说明。[0037]实施例一[0038]本发明提供一种用于时间数字转换器的延迟链译码器的装置,如图1所示,包括:数据采集模块,数据预处理模块,独热码产生模块和独热码译码模块,数据采集模块是用于获取指定位数待测试机器码数据ring_counter_i;数据预处理模块是用于基于指定位数待测试机器码数据进行预处理,将待测试机器码数据转换成温度计码prepro_code;独热码产生模块是用于基于温度计码,通过独热码处理将温度计码转换成独热码one_hot_code;独热码译码模块是用于基于独热码,通过独热码译码处理将独热码转换成二进制码ring_counter_decode。[0039]预处理模块,其输入端n位ring_counter_in连接外部采样触发器的输出端;其输出端输出n位prepro_code连接独热码产生模块;独热码产生模块,其输入端输入n位prepro_code连接数据预处理模块;其输出端输出n位one_hot_code连接独热码译码模块;独热码译码模块,其输入端输入n位one_hot_code连接独热码产生模块;其输出端输出位ring_counter_decode为本发明最终输出的二进制码。[0040]数据预处理模块用于将n位ring_counter_in数据分为奇数组和偶数组,每组内三个1位数据通过一个三输入与门获得n位prepro_code。其输入为n位ring_counter_in为零一相间的机器码,其中n为奇数。[0041]数据预处理模块将ring_counter_in[2*(i-(n+3)/2)]、ring_counter_in[2*(i-(n+3)/2)+2]、ring_counter_in[2*(i-(n+3)/2)+4]划分为偶数组生成独热码的高位prepro_code[i],其中i》(n+1)/2。[0042]数据预处理模块将ring_counter_in[2i-3]、ring_counter_in[2i-1]、ring_counter_in[2i+1]划分为奇数组生成独热码的低位prepro_code[i],其中1《i《(i-1)/2。[0043]数据预处理模块将ring_counter_in[n-3]、ring_counter_in[n-1]、ring_counter_in[1]划分为一组,生成prepro_code[0]。[0044]数据预处理模块将ring_counter_in[n-1]、ring_counter_in[1]、ring_counter_in[3]划分为一组,生成prepro_code[1]。[0045]数据预处理模块将ring_counter_in[n-4]、ring_counter_in[n-2]、ring_counter_in[0]划分为一组,生成prepro_code[(n-1)/2]。[0046]数据预处理模块将ring_counter_in[n-2]、ring_counter_in[0]、ring_counter_in[2]划分为一组,生成prepro_code[(n+1)/2]。[0047]独热码产生模块将n位prepro_code数据两两进行prepro_code[j]&(!prepro_code[j+1])运算,其中0≤j<n-1,产生独热码one_hot_code[j]连接独热码译码模块。[0048]独热码产生模块将prepro_code数据最高位和最低位进行prepro_code[n-1]&(!prepro_code[0])运算,产生独热码最高位one_hot_code[n-1]连接独热码译码模块。[0049]独热码译码模块采用多路选择器将n位独热码one_hot_code译码获得位二进制码ring_counter_deode。[0050]如图2所示,在本实施例中,用于时间数字转换器的延迟链译码器,其输入ring_counter_in数据为63位零一相间的机器码;用于时间数字转换器的延迟链译码器,其输出ring_counter_decode数据为6位二级制码。[0051]在本实施例中数据预处理模块将输入ring_counter_in按奇偶进行分组,每组通过三输入与门进行运算,获得预处理后的63位数据prepro_code。数据预处理模块中具体分组和预处理运算过程,可以表示为如下表达式组:[0052]prepro_code[62]=ring_counter_in[58]&ring_counter_in[60]&ring_counter_in[62][0053]prepro_code[61]=ring_counter_in[56]&ring_counter_in[58]&ring_counter_in[60][0054]l l[0055]prepro_code[33]=ring_counter_in[0]&ring_counter_in[2]&ring_counter_in[4][0056]prepro_code[32]=ring_counter_in[61]&ring_counter_in[0]&ring_counter_in[2][0057]prepro_code[31]=ring_counter_in[59]&ring_counter_in[61]&ring_counter_in[0][0058]prepro_code[30]=ring_counter_in[57]&ring_counter_in[59]&ring_counter_in[61][0059]l l[0060]prepro_code[2]=ring_counter_in[1]&ring_counter_in[3]&ring_counter_in[5][0061]prepro_code[1]=ring_counter_in[62]&ring_counter_in[1]&ring_counter_in[3][0062]prepro_code[0]=ring_counter_in[60]&ring_counter_in[62]&ring_counter_in[1][0063](1)[0064]数据预处理模块输出的63位prepro_code为温度计码,形如“111111111111……00000000000000”。[0065]在本实施例中,独热码产生模块采用非门和与门将输入的63位温度计码prepro_code转换为63位独热码one_hot_code。独热码产生模块具体的运算过程,可以概括为如下表达式:[0066][0067]在本实施例中,独热码译码模块采用多路选择器将63位独热码one_hot_code译码获得6位二进制码ring_counter_deode。[0068]至此,完成了对本发明整个电路从电路模块构成、每个模块运行原理、以及每个模块对数据处理的说明。[0069]实施例二[0070]本发明提供一种用于时间数字转换器的延迟链译码器的方法,如图3所示,具体步骤如下:[0071]获取指定位数待测试机器码数据ring_counter_in;基于指定位数待测试机器码数据进行预处理,将待测试机器码数据转换成温度计码prepro_cod;基于温度计码,通过独热码处理将温度计码转换成独热码one_hot_code;基于独热码,通过独热码译码处理将独热码转换成二进制码ring_counter_decode;[0072]预处理方法的过程包括:用于将n位ring_counter_in数据分为奇数组和偶数组,每组内三个1位数据通过一个三输入与门获得n位prepro_code。其输入为n位ring_counter_in为零一相间的机器码,其中n为奇数;[0073]预处理方法将ring_counter_in[2*(i-(n+3)/2)]、ring_counter_in[2*(i-(n+3)/2)+2]、ring_counter_in[2*(i-(n+3)/2)+4]划分为偶数组生成独热码的高位prepro_code[i],其中i》(n+1)/2;[0074]预处理方法将ring_counter_in[2i-3]、ring_counter_in[2i-1]、ring_counter_in[2i+1]划分为奇数组生成独热码的低位prepro_code[i],其中1《i《(i-1)/2;[0075]预处理方法将ring_counter_in[n-3]、ring_counter_in[n-1]、ring_counter_in[1]划分为一组,生成prepro_code[0];[0076]预处理方法将ring_counter_in[n-1]、ring_counter_in[1]、ring_counter_in[3]划分为一组,生成prepro_code[1];[0077]预处理方法将ring_counter_in[n-4]、ring_counter_in[n-2]、ring_counter_in[0]划分为一组,生成prepro_code[(n-1)/2];[0078]预处理方法将ring_counter_in[n-2]、ring_counter_in[0]、ring_counter_in[2]划分为一组,生成prepro_code[(n+1)/2]。[0079]独热码处理方法将n位prepro_code数据两两进行prepro_code[j]&(!prepro_code[j+1])运算,其中0≤j<n-1,产生独热码one_hot_code[j]连接独热码译码模块;[0080]独热码处理方法将prepro_code数据最高位和最低位进行prepro_code[n-1]&(!prepro_code[0])运算,产生独热码最高位one_hot_code[n-1]连接独热码译码模块;[0081]独热码译码方法包括采用多路选择器将n位独热码one_hot_code译码获得位二进制码ring_counter_deode。[0082]如图2所示,在本实施例中,用于时间数字转换器的延迟链译码器,其输入ring_counter_in数据为63位零一相间的机器码;用于时间数字转换器的延迟链译码器,其输出ring_counter_decode数据为6位二级制码。[0083]在本实施例中数据预处理模块将输入ring_counter_in按奇偶进行分组,每组通过三输入与门进行运算,获得预处理后的63位数据prepro_code。数据预处理模块中具体分组和预处理运算过程,可以表示为如下表达式组:[0084]prepro_code[62]=ring_counter_in[58]&ring_counter_in[60]&ring_counter_in[62][0085]prepro_code[61]=ring_counter_in[56]&ring_counter_in[58]&ring_counter_in[60][0086]l l[0087]prepro_code[33]=ring_counter_in[0]&ring_counter_in[2]&ring_counter_in[4][0088]prepro_code[32]=ring_counter_in[61]&ring_counter_in[0]&ring_counter_in[2][0089]prepro_code[31]=ring_counter_in[59]&ring_counter_in[61]&ring_counter_in[0][0090]prepro_code[30]=ring_counter_in[57]&ring_counter_in[59]&ring_counter_in[61][0091]l l[0092]prepro_code[2]=ring_counter_in[1]&ring_counter_in[3]&ring_counter_in[5][0093]prepro_code[1]=ring_counter_in[62]&ring_counter_in[1]&ring_counter_in[3][0094]prepro_code[0]=ring_counter_in[60]&ring_counter_in[62]&ring_counter_in[1][0095](1)[0096]数据预处理模块输出的63位prepro_code为温度计码,形如“111111111111……00000000000000”。[0097]在本实施例中,独热码产生模块采用非门和与门将输入的63位温度计码prepro_code转换为63位独热码one_hot_code。独热码产生模块具体的运算过程,可以概括为如下表达式:[0098][0099]在本实施例中,独热码译码模块采用多路选择器将63位独热码one_hot_code译码获得6位二进制码ring_counter_deode。[0100]至此,完成了对本发明整个电路从电路模块构成、每个模块运行原理、以及每个模块对数据处理的说明。[0101]以上的实施例仅是对本技术优选方式进行的描述,并非对本技术的范围进行限定,在不脱离本技术设计精神的前提下,本领域普通技术人员对本技术的技术方案做出的各种变形和改进,均应落入本技术权利要求书确定的保护范围内。

本文地址:https://www.jishuxx.com/zhuanli/20240730/150000.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

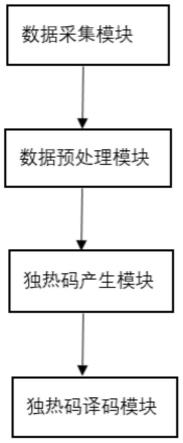

返回列表