一种应用于数字锁相环的时间数字转换器的校准方法与流程

- 国知局

- 2024-07-30 09:42:40

1.本发明涉及模拟集成电路的设计技术领域,更具体地说,它涉及一种应用于数字锁相环的时间数字转换器的校准方法。背景技术:2.在过去20年里,数字锁相环在很多高性能的通信芯片中替代了传统的模拟锁相环。虽然最初由得州仪器公司(texas i nstruments)发表的数字锁相环结构不采用相位/频率检测器(pfd:phase-frequency detector),但之后文献里出现的数字锁相环大多保留了pfd。3.相比于模拟锁相环(apll:ana l og phase-l ocked l oop),数字锁相环有很多优点,比如:改变工艺时电路转换的便利,省去了模拟环路滤波器中占面积的电容,需要数字调制时锁相环参数校正的便利,乃至采用了σ-δ小数分频时消除量化噪声的便利等。同时,采用了量化噪声消除的σ-δ小数锁相环(fn-pll:fract iona l-n pll),其环路带宽可以增大很多。4.尽管dpll与apll相比有上述的诸多优点,但其设计的主要困难就是tdc。tdc的设计要求,除了精度、线性度、功耗之外,一个重要的环节是在dpll中涉及tdc的一些校准。现有的tdc校准存在使用时间太长的参考时钟的周期,容易增加tdc转换的累计误差和非线性误差。技术实现要素:5.针对现有技术存在的不足,本发明的目的在于提供一种应用于数字锁相环的时间数字转换器的校准方法。6.为实现上述目的,本发明提供了如下技术方案:7.一种应用于数字锁相环的时间数字转换器的校准方法,包括如下步骤:8.步骤一:将osc的频率校准至fosc,获取osc的相位差参考时钟ckref和除法器反馈时钟ckdiv;9.步骤二:向pfd输入相位差参考时钟和除法器反馈时钟的第一组数据,设置ckref领先ckdiv共k个osc周期;10.步骤三:用tdc测量pfd第一组数据的输出脉宽并标记为dkp;11.步骤四:向pfd输入相位差参考时钟和除法器反馈时钟的第二组数据,设置ckref领先ckdiv共2k个osc周期;12.步骤五:用tdc测量pfd第二组数据的输出脉宽并标记为d2kp;13.步骤六:利用公式dp=2·dkp-d2kp计算pfd的最小正脉冲宽度,对应的k个tosc的tdc量化值为dktosc=d2kp-dkp;14.步骤七:向pfd输入相位差参考时钟和除法器反馈时钟的第三组数据,设置ckref落后ckdiv共k个osc周期;15.步骤八:用tdc测量pfd第三组数据的输出脉宽并标记为dkm;16.步骤九:向pfd输入相位差参考时钟和除法器反馈时钟的第四组数据,设置ckref落后ckdiv共2k个osc周期;17.步骤十:用tdc测量pfd第四组数据的输出脉宽并标记为d2km;18.步骤十一:利用公式dm=2·dkm-d2km计算频率检测器的最小正脉冲宽度。19.进一步的,步骤二中pfd的输入相位差为其中为pfd输入相位为正时的偏差。20.进一步的,步骤四中pfd的输入相位差为21.进一步的,步骤六中pfd输入正相位偏差的tdc转换值为其中ttdc是tdc的转换精度。22.进一步的,步骤七中pfd的输入相位差为其中为pfd输入相位为负时的偏差。23.进一步的,步骤九pfd的输入相位差为24.进一步的,步骤十一中pfd输入负相位偏差的tdc转换值为25.与现有技术相比,本发明具备以下有益效果:26.1、本发明使用数字频率校准的osc,产生校准需要的pfd输入相位差,避免了使用时间太长的参考时钟的周期,减少了tdc转换的累计误差和非线性误差,既分别测量了tdc输入相位为正和负时各自的相位偏差,又测量了tdc本身的精度,可供sdm量化误差消除、等功能使用。27.2、本发明的检测结果为数字输出,数字输出便于反馈控制电路的灵活实现,可以根据实际电路功能和性能的要求,以各种不同的方式实现电源波动最佳的反馈控制。附图说明28.图1为本发明的流程框图;29.图2为包含pfd和tdc的数字锁相环模块图;30.图3为数字锁相环中消除pfd正、负相位偏差的结构框图。具体实施方式31.无论振荡器部分采用直接数字控制(dco:d igita l ly-contro l l ed osc i l l ator),还是采用数模转换器(dac:d igita l-to-ana l og converter)加上模拟电压控制的振荡器(vco:vo ltage-contro l l ed osci l l ator),类似图2采用pfd+时间数字转换器(tdc)+环路数字滤波器的数字锁相环(dpll:d igita l phase-l ocked l oop)结构,已被学术界和工业界广泛使用。32.考虑到精度和线性度要求,tdc每次转换的使能时间不能太短。类似于在使用电荷泵(cp:charge pump)的apll里,为了消除cp的死角(dead zone),pfd的输出脉冲宽度设定了一个最小值一样。在使用pfd+tdc的dpll里,pfd的输出脉冲宽度也不能小于一个最小值。为了提高dpll的总体性能,在dpll中涉及tdc的校准有以下几方面:1)当pfd输出正相位差时,对应最小相位差的tdc转换值;2)当pfd输出负相位差时,对应最小相位差的tdc转换值;3)tdc的精度测量,用于σ-δ量化噪声的消除和数字调制时环路参数的校准等。33.实施例134.参照图1至图3,本发明提出了一种应用于数字锁相环的时间数字转换器的校准方法,如图1所示。首先对通常为很高频率的振荡器(osc:osci l l ator)的频率进行数字校准。在振荡器的可使用频率范围内,可以灵活选择合适的设置频率fosc。比如,以方便计算σ-δ调制器(sdm:s i gma-de lta modu l ator)量化噪声消除为标准。通常osc频率的数字校准精度在±0.2%以下。比如在手机射频通信里,锁相环中的lc osc震荡在4ghz左右,而osc频率经数字校准后的误差通常不超过±30mhz。因此,数字校准后的osc频率已有足够的精度供本发明的tdc校准使用。35.需要指出的一点是,本发明采用数字频率校准的osc的周期产生pfd输入相位差,而不是通常频率为十几到几十mhz的参考时钟周期。好处是大大减小tdc校准时pfd的输入相位差。当数字锁相环处于稳态工作时,其瞬态输入相位差通常在几个osc周期之内。虽然来自晶体振荡器的参考时钟具有更精确的频率,但由于tdc的非线性以及转化误差累积,采用太大的输入相位差则最后校准的误差会大很多。36.接下来,分别测量在输出相位差为正和负时,pfd的最小脉冲对应的tdc转换结果。为此,先从数字校准后的osc产生已知相位差的参考时钟ckref和除法器反馈时钟ckdiv到pfd的输入。37.第一组pfd输入时钟,设为ckref领先ckdiv共k个osc周期。即pfd的输入相位差为:其中为pfd输入相位为正时的偏差,即对应输出的最小正相位。记此时tdc转换输出的数据为dkp。38.第二组pfd输入时钟,设为ckref领先ckdiv共2k个osc周期。即pfd的输入相位差为:记对应tdc转换输出的数据为d2kp。39.至此,计算出对应pfd输入正相位偏差的tdc转换值为其中ttdc是tdc的转换精度,即时间量化的步长,对应的k个tosc的时间数字转换器量化值为dktosc=d2kp-dkp。40.同时,根据上面两步tdc转换结果,计算出ttdc如下:如下:其中,tvco是vco的周期;41.类似地,接着测量pfd输入负相位时的相位偏差。42.第三组pfd输入时钟,设为ckref落后ckdiv共k个osc周期。即pfd的输入相位差为:其中为pfd输入相位为负时的偏差,即对应输出的最小负相位。记这次tdc转换输出的数据为dkm。43.第四组pfd输入时钟,设为ckref落后ckdiv共2k个osc周期。即pfd的输入相位差为:记该次tdc转换输出的数据为d2km。至此,计算出对应pfd输入负相位偏差的tdc转换值为44.同样可以从dkm和d2km计算ttdc的值。结果应该和公式四相近。另外,如果同样的输入相位差,两次tdc转换结果相差超过±1,可以取多次tdc转换结果的平均值来提高测量精度。45.从公式三和公式七看,osc数字校准后的频率精度,基本上不影响dp和dm的测量和计算结果的值。而从公式四看,如果不考虑每次tdc转换的量化误差,计算结果得到的ttdc的精度和osc频率设置的精度相同。因此,在实际芯片设计时osc频率数字校准的精度足够高,不会影响本发明涉及tdc的数字锁相环校准精度。46.图3所示为本发明的数字锁相环中消除pfd正、负相位偏差的结构框图。根据每次pfd输入相位的正、负符号位,选择从tdc输出数据中减去正相位偏差或负相位偏差。根据公式四计算的tdc转化的时间步长值,可以计算出每个pfd输入周期下sdm的量化误差,进而也从tdc输出数据里减去。消除了pfd相位偏差和sdm量化误差的tdc输出数据,作为环路数字滤波器的输入。47.通常经高通整形(high-pass shaped)后的sdm量化误差,是锁相环带宽的主要限制因素。如本发明里,测量和计算后得到的ttdc值,可以用于计算sdm的量化误差,进而在tdc输出数据进入滤波器前,从中减去。限于各种测量和计算误差,即便sdm量化误差只消除了90%(即并未完全消除,而是减小了20db),也可以大大增加锁相环的带宽。48.实施例249.本发明的数字锁相环里涉及tdc的校准技术,也可以应用在其他类似芯片涉及领域。尽管校准方法和流程稍有不同,但其原理、以及简单性和可靠性都类似。50.以上所述仅是本发明的优选实施方式,本发明的保护范围并不仅局限于上述实施例,凡属于本发明思路下的技术方案均属于本发明的保护范围。应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理前提下的若干改进和润饰,这些改进和润饰也应视为本模板的保护范围。

本文地址:https://www.jishuxx.com/zhuanli/20240730/150604.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

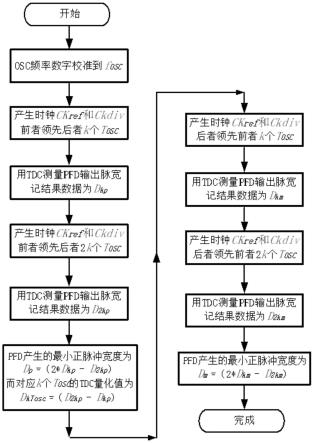

返回列表