基于FPGA的多回波及低资源消耗的时间数字转换方法

- 国知局

- 2024-07-30 10:08:17

本发明属于高精度时间测量,尤其涉及基于fpga的多回波及低资源消耗的时间数字转换方法。

背景技术:

1、时间数字转换器(time-to-digital converter,tdc),是一种高精度的时间间隔测量电路,可以实现由连续的时间量到数字量的输出,已广泛应用于科学实验和工程试验中,特别是在激光雷达等领域,通常需要获取激光脉冲的多回波信息来辅助数据的滤波和处理,从而更好地揭示被测目标的特性,这一需求使得多回波时间数字转换器得到飞速发展。

2、从tdc的实现平台来看,可以分为两类:一类是专用集成电路(asic)技术设计的tdc;第二类是现场可编程门阵列(fpga)技术设计的tdc。专用集成电路实现的tdc,其优点是测量精度高、可靠性和线性度更好,但设计成本昂贵、开发周期长且不利于系统的升级和维护。现场可编程门阵列实现的tdc可解决上述的问题,具备成本低、开发周期短且更容易验证的特点,特别是近年来随着fpga技术的普及,设计工艺的提高,基于fpga的tdc技术得到空前发展。

3、从tdc的实现架构来看,抽头延迟线和相控时钟是目前国内外应用较为广泛的架构,抽头延迟线分辨率高,但是其积分非线性度会随着延迟链的长度增加而恶化,尤其是在针对多回波信号的测量时,很容易由于误差的累积而对结果造成严重的偏差,导致回波时间数据错乱,而且测量范围通常较小。相控时钟架构是利用一组工作在同频等相差时钟下的计数器通过累加的方式从而实现时间的细分测量,具备良好的线性度,且很容易实现较高的测量范围,十分适合多回波信号的特性,但是传统的相控时钟架构需要使用到大量计数器,导致硬件资源使用率高的问题。因此,如何改进这一架构,设计出一种兼顾多回波测量与低资源消耗的时间数字转换方法具有十分重要的研究意义。

技术实现思路

1、本发明公开的基于fpga的多回波及低资源消耗的时间数字转换方法,旨在提供一种利用fpga作为部署器件,通过对传统相控时钟架构实现方式的改进,实现了一种既能完成对多回波信号时间间隔的测量,又可以满足低资源消耗的时间数字转换方法。本发明可用于激光雷达、三维成像等领域。

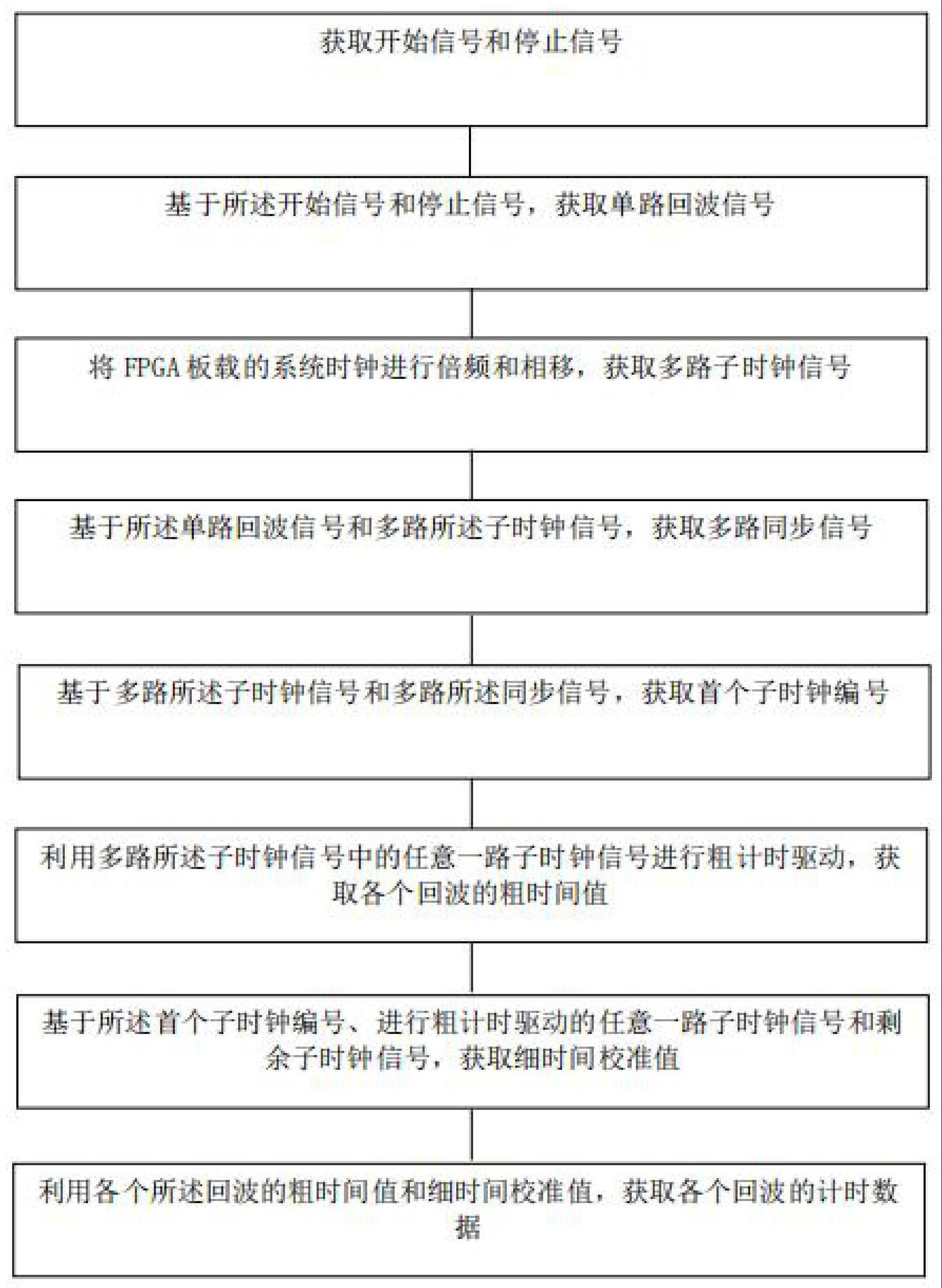

2、为实现上述目的,本发明提供了一种基于fpga的多回波及低资源消耗的时间数字转换方法,包括以下步骤:

3、获取开始信号和停止信号;

4、基于所述开始信号和停止信号,获取单路回波信号;

5、将fpga板载的系统时钟进行倍频和相移,获取多路子时钟信号;

6、基于所述单路回波信号和多路所述子时钟信号,获取多路同步信号;

7、基于多路所述子时钟信号和多路所述同步信号,获取首个子时钟编号;

8、利用多路所述子时钟信号中的任意一路子时钟信号进行粗计时驱动,获取各个回波的粗时间值;

9、基于所述首个子时钟编号、进行粗计时驱动的任意一路子时钟信号和剩余子时钟信号,获取细时间校准值;

10、利用各个所述回波的粗时间值和细时间校准值,获取各个回波的计时数据。

11、可选的,获取所述单路回波信号包括:

12、将所述开始信号和所述停止信号通过异或门进行整合,获得所述单路回波信号。

13、可选的,基于所述单路回波信号和多路所述子时钟信号,获取多路所述同步信号包括:

14、将所述单路回波信号分别在多路所述子时钟信号的上升沿和下降沿进行同步,获取多路所述同步信号。

15、可选的,多路所述同步信号的特征包括:

16、多路所述同步信号中每一路同步信号的上升沿与对应多路所述子时钟信号中每一路子时钟信号的上升沿或下降沿重合;

17、多路所述同步信号中每一路同步信号的下降沿与所述单路回波信号的下降沿重合。

18、可选的,获取所述首个子时钟编号的方法包括:

19、利用多路所述子时钟信号驱动的触发器对多路所述同步信号中每一路同步信号状态进行捕获,获取多路所述同步信号状态的编码;

20、基于多路所述同步信号状态的编码,获取所述首个子时钟编号。

21、可选的,基于多路所述同步信号状态的编码,获取所述首个子时钟编号的方法包括:

22、基于多路所述同步信号状态的编码,判断每一路所述同步信号状态的编码中高低电平的个数,获取多路所述同步信号的到达顺序;

23、基于多路所述同步信号的到达顺序,获取所述首个子时钟编号。

24、可选的,基于所述首个子时钟编号、进行粗计时驱动的任意一路子时钟信号和剩余子时钟信号,获取细时间校准值的方法包括:

25、获取进行粗计时驱动的所述任意一路子时钟信号和所述剩余子时钟信号的相位关系;

26、基于所述相位关系和首个所述子时钟编号,获取多路所述子时钟信号的上升沿和下降沿的细时间校准系数;

27、基于所述细时间校准系数和系统分辨率,获取开始信号脉冲的细时间校准值和停止信号脉冲的细时间校准值。

28、可选的,所述细时间校准值包括:

29、q=λ×δ

30、其中,q为细时间校准值,λ为各个子时钟信号的上升沿时钟或下降沿时钟的细时间校准系数,δ为系统分辨率。

31、可选的,各个所述回波的计时数据具体包括:

32、tn=pn+q0-qn

33、其中,tn为第n个回波的计时数据,pn为当前第n个回波的粗时间值,q0为针对开始信号脉冲的细时间校准值,qn为针对第n个停止信号脉冲的细时间校准值。

34、本发明技术效果:本发明公开的基于fpga的多回波及低资源消耗的时间数字转换方法,通过对传统相控时钟架构的改进创新,实现了一种既能完成对多回波信号时间间隔的测量,又能实现低资源消耗的时间数字转换方法。

技术特征:1.基于fpga的多回波及低资源消耗的时间数字转换方法,其特征在于,包括:

2.如权利要求1所述的基于fpga的多回波及低资源消耗的时间数字转换方法,其特征在于,获取所述单路回波信号包括:

3.如权利要求1所述的基于fpga的多回波及低资源消耗的时间数字转换方法,其特征在于,基于所述单路回波信号和多路所述子时钟信号,获取多路所述同步信号包括:

4.如权利要求3所述的基于fpga的多回波及低资源消耗的时间数字转换方法,其特征在于,多路所述同步信号的特征包括:

5.如权利要求1所述的基于fpga的多回波及低资源消耗的时间数字转换方法,其特征在于,获取所述首个子时钟编号的方法包括:

6.如权利要求5所述的基于fpga的多回波及低资源消耗的时间数字转换方法,其特征在于,基于多路所述同步信号状态的编码,获取所述首个子时钟编号的方法包括:

7.如权利要求1所述的基于fpga的多回波及低资源消耗的时间数字转换方法,其特征在于,基于所述首个子时钟编号、进行粗计时驱动的任意一路子时钟信号和剩余子时钟信号,获取细时间校准值的方法包括:

8.如权利要求7所述的基于fpga的多回波及低资源消耗的时间数字转换方法,其特征在于,所述细时间校准值包括:

9.如权利要求8所述的基于fpga的多回波及低资源消耗的时间数字转换方法,其特征在于,各个所述回波的计时数据具体包括:

技术总结本发明公开基于FPGA的多回波及低资源消耗的时间数字转换方法,包括:获取开始信号和停止信号;基于所述开始信号和停止信号,获取单路回波信号;将FPGA板载的系统时钟进行倍频和相移,获取多路子时钟信号;基于所述单路回波信号和多路所述子时钟信号,获取多路同步信号;基于多路所述子时钟信号和多路所述同步信号,获取首个子时钟编号;利用多路所述子时钟信号中的任意一路子时钟信号进行粗计时驱动,获取各个回波的粗时间值;基于所述首个子时钟编号、进行粗计时驱动的任意一路子时钟信号和剩余子时钟信号,获取细时间校准值;利用各个所述回波的粗时间值和细时间校准值,获取各个回波的计时数据。技术研发人员:曹杰,李杨,李升才,郝群,韩斌,梁龙受保护的技术使用者:北京理工大学技术研发日:技术公布日:2024/1/13本文地址:https://www.jishuxx.com/zhuanli/20240730/151787.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表