基于单管耦合精细延迟产生电路的时间数字转换方法

- 国知局

- 2024-07-30 10:08:57

本发明涉及集成电路,具体为一种基于单管耦合精细延迟产生电路的时间数字转换方法。

背景技术:

1、高精度的时间测量技术对于现代诸多领域都有着十分重要的意义,例如:激光测距、天文观测、量子物理、雷达定位、分子影像等,诸如此类的发展都离不开高精度的测时技术。与此同时,国防科技的发展,工业技术的进步,也都对时间的测量都提出了越来越高的要求。研究细微时间间隔的测量方法,进一步提高时间测量的分辨率与测量范围,是当今研究的热点之一。时间数字转换器(time-to-digital converter,tdc)是一种常用的测时电路,它通过时间数字转换技术,可以将待测量的时间域信号转换为数字信号,通过对数字信号的处理得到一个表征待测时间量的数字码,通过延迟单元延时与数字码值的简单运算便可得到皮秒级分辨率的测量时间间隔。高分辨率的tdc在很多领域都有着广泛的应用。

2、现有技术中,提高时间数字转换器分辨率的常用方法,常见的方法是通过减小单个延迟单元的最小延时,采用cmos反相器耦合n个环形振荡器,通过注入锁定将电路产生的延时为单个反相器延时的1/n,从而产生精细延迟单元。

3、上述现有技术中,采用cmos反相器进行环形振荡器耦合来产生最小延迟差,由于耦合使用与环型振荡器相同尺寸的反相器,会导致电路的负载增大,反相器中的pmos晶体管寄生电容会对整个环路的振荡频率造成影响。同时,当纵向级连数大于环形振荡器种反相器个数时,会使振荡的主环副环发生转换,最高振荡频率此时由纵向级连决定,从而限制耦合环形振荡器的最高振荡频率。限制最高振荡频率,会导致tdc的最小延迟单元延迟受到限制,进而使tdc的测量分辨率受限。由于环形振荡器横向主环路与和纵向主环路采用相同尺寸的反相器,在受到外界干扰时会引起两环间的竞争现象,从而导致系统无法正常工作。

4、本发明基于以上问题,提出了一种基于单管进行环形振荡器耦合的精细时间产生电路来进行时间数字转换,可保证时间数字转换所需相位数、较高的工作稳定性、能够在简单的tdc结构上提高tdc的分辨率、在使tdc具有高分辨率的同时,还具有较高的线性度和较大的测量范围。

5、为此,我们提出一种基于单管耦合精细延迟产生电路的时间数字转换方法。

技术实现思路

1、本发明的目的在于提供一种基于单管耦合精细延迟产生电路的时间数字转换方法,以解决上述背景技术中提出的问题。

2、术语解释:

3、时间数字转换器(time-to-digital converter,简称tdc):是将时间间隔转换为数字信号的有效手段。tdc的分辨率是tdc所能够测量的最小时间间隔,依赖于单位门延迟的大小。tdc测时的精度可以达到皮秒级,且能够支持连续测量、集成;

4、单管耦合:两个系统之间仅仅采用单个pmos或者nmos进行连接;

5、精细延迟产生电路:一种可以产生亚门级延时的电路;

6、环形振荡器:是由三个或更多奇数个反相器输出端和输入端首尾相接,构成环状的机器。电路的输出是振荡的两个高低电平。τ是单个反相器的最小延迟,n是环形振荡器中反相器个数。振荡周期t=2*τ*n;

7、注入锁定:指一个环形振荡器被另一个频率相近的环形振荡器所扰动的频率效应。当第二个环形振荡器的振荡频率与第一个环形振荡器足够接近,且两个环形振荡器间耦合足够大时,会使得第一个环形振荡器跟随第二个环形振荡器振荡。达到平衡时,两者的振荡频率相等。

8、为实现上述目的,本发明提供如下技术方案:

9、一种基于单管耦合精细延迟产生电路的时间数字转换方法,包括:

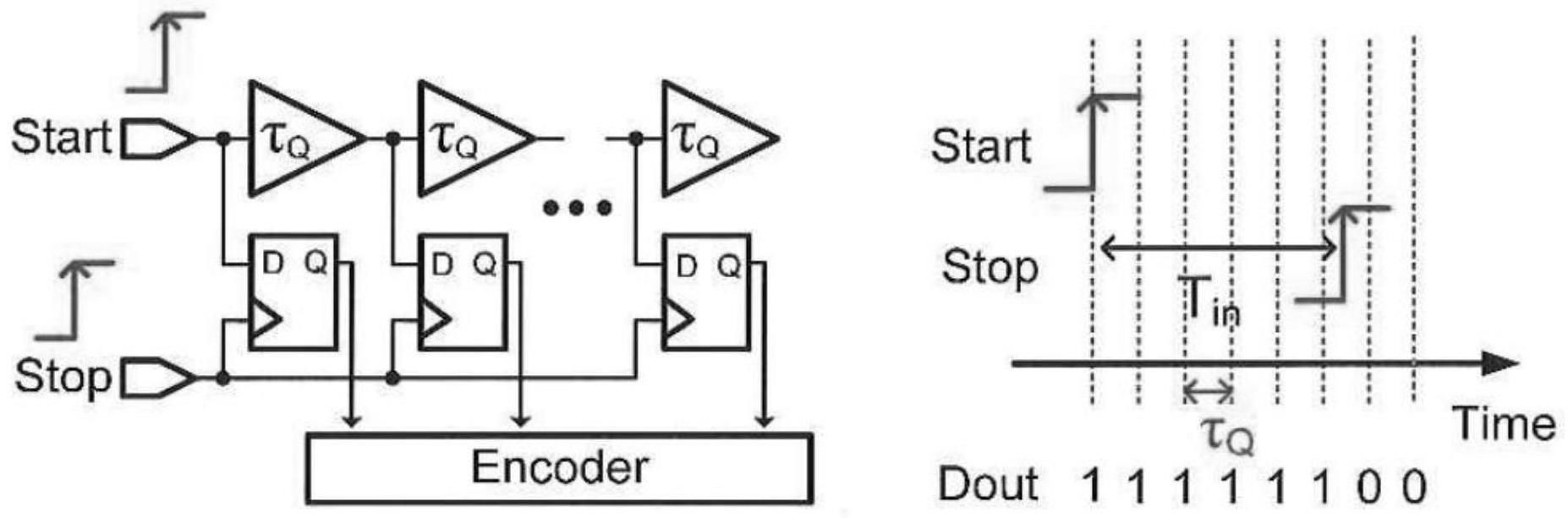

10、通过时间数字转换器测量具有一定时间间隔的start和stop两个信号上升沿,当start信号快于stop信号到达d触发器时,d触发器输出高电平码值1,当start信号慢于stop信号到达d触发器时,d触发器输出低电平码值0,通过让start信号经过由一系列延迟单元构成的延迟链,使start信号到达触发器阵列中d触发器的时刻逐渐慢于stop信号,进而由d触发器q端输出一系列数字码值,得出start和stop之间的延时,以量化待测时间间隔,实现时间数字转换;

11、环形振荡器基于m级反相器的环形振荡器结构,反相器通过m1和m2组成,其中m2的宽长比是m1宽长比的两倍,

12、振荡频率:

13、延迟时间:td=rctot

14、r=r1||r2

15、r为延时单元输出结点等效阻抗,r1为m1管等效阻抗,r2为m2管等效阻抗,ctot为延时单元输出等效电容,其大小为:

16、

17、ctot、cin、cout、cox、w1、l1、w2和l2分别表示延时单元的输出结点总电容、输入电容、输出电容、栅氧电容、m1管宽度、m2管长度、m1管宽度和m2管长度,由上式可以得到:ctot∝w1l1+w2l2,因为

18、

19、k1、k2是与工艺相关的量且k1≠k2,因此可以得到:

20、

21、从上式可以得到:延迟时间td与m1、m2的宽度无关,且与m1、m2长度密切相关,

22、n个上述环形振荡器通过单个nmos晶体管进行耦合构成的精细延迟产生电路,其最上端输ti与下方bi+2相连接,其中nmos晶体管宽度w与环形振荡器中m1相同,但是m是环形振荡器m1的四分之一,当环形振荡器中所有反相器与其耦合输入之间有一个固定相位差时,由于每一个环形振荡器中反相器的延时时间都相等,因此每一个环形振荡器的振荡频率都相同,从而导致每一个环形振荡器中反相器与耦合输入的相位差随时间而固定,这样就使得当经历n个环之后,环形振荡器的相位输出能够与之前的环形振荡器相位输出相等,通过将最上端注入ti与最下方输出bi+2相连接,通过上述原理可以知道当环形振荡器在注入锁定发生达到平衡后,最上端的环与最下端的环之间相位差为两个反相器相差即2π,这样从上到下每个环之间的相位差即为2π/n,每个环形振荡器输出上升沿之间延时差为td/n,td为单个反相器延时时间,通过start和stop分别连接9个d触发器对环型振荡器每个相位输出采样,依据相位关系将d触发器采样结果按如图顺序进行编码,能够得到两个数字码,对这个数字码作差就可以得到start和stop信号在一个反相器周期t内的相位差x,环路计数器用于在start信号上升沿到来后对环路输出上升沿进行计数,得到计数值y,通过公式:ts=x*τ+y*t,就可以得到start和stop信号间的时间间隔ts,其中为相位差延时,完成通过数字码x和y对待测时间间隔ts的量化。

23、优选地,所述start和stop之间的延时定义为t,其中,

24、t=n*t

25、n为采样1的个数,t为每个延时单元的最小延迟。

26、优选地,所述环形振荡器基于m级反相器的环形振荡器结构,且m为奇数。

27、与现有技术相比,本发明的有益效果是:使用单个小尺寸nmos管耦合的n个环形振荡器的精细时间产生电路以及将其用于时间数字转换的技术,一定程度避免两环路“竞争”现象,完全消除pmos管寄生电容影响,可以得到更高的环形振荡器振荡频率和更优越的工作稳定性。通过d触发器对本发明精细时间产生电路单跳沿采样可获得更小的时间数字转换间隔,使得本发明中的时间数字转换技术具有更高的分辨率,进而采用本发明的时间数字转换器将具有更高的分辨率。

本文地址:https://www.jishuxx.com/zhuanli/20240730/151852.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表