一种快速锁定的宽可调范围高精度数字时间转换器

- 国知局

- 2024-07-30 10:16:21

本发明属于数字集成电路设计领域,具体涉及一种快速锁定的宽可调范围高精度数字时间转换器。

背景技术:

1、数字时间转换器(dtc)是一种将数字信号转化为时间信号的器件,可以将固定参考频率的信号经延迟生成频率偏移或相位偏移的信号,被应用于自动化测试设备(ate)、锁相环、同步应用系统等技术领域。

2、常用的数字时间转换器往往难以实现同时兼顾快速锁定、宽可调范围和高精度的特性。例如使用多相参考时钟实现的数字时间转换器往往可以实现快速锁定和很宽的延迟调节范围,但由于参考时钟频率难以提到很高,而其精度又受限于参考时钟相位间的时间差,故量化时间间隔往往达到几百皮秒甚至更高,不能实现高精度的特点。而使用多周期时钟相位差的数字时间转换器基于游标法的原理,可以达到较好的延迟精度,缺点是牺牲了反应时间,即其往往需要很多个时钟周期才能输出一个延迟信号,且延迟信号的宽度难以调节。

3、在自动化测试设备(ate)应用领域,往往需要输出高精度的可调节相位的激励信号,这一功能可以通过构建数字时间转换器实现。该转换器一般要求锁定时间短且稳定可控,调节范围至少在一个系统时钟以上,可量化时间间隔至少达到50ps以内。

技术实现思路

1、有鉴于此,本发明的目的在于提供一种快速锁定的宽可调范围高精度数字时间转换器,该转换器可以用于ate设备产生高精度相位可调节激励信号,也可用于其它适合的高精度数字时间转换应用。

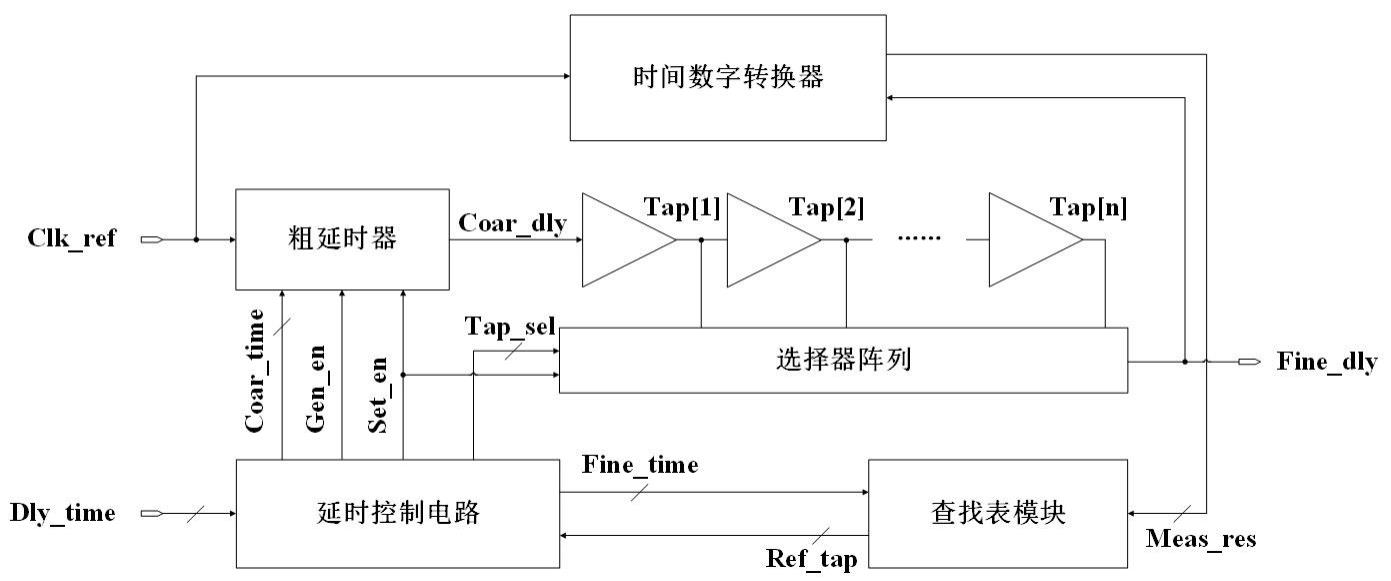

2、一种快速锁定的宽可调范围高精度数字时间转换器,包括粗延时器、细延时器、时间数字转换器、查找表模块、延时控制电路;

3、所述的粗延时器用于按照参考时钟产生粗延时信号,该信号接入细延时器进行进一步的细延时;

4、所述的细延时器用于将粗延时信号进一步的延时,输出为细延时信号,该信号被分别接到时间数字转换器的待测信号输入端口和系统输出io上;

5、所述的时间数字转换器用于测量细延时信号与开始延时使能信号的时间差值;

6、所述的查找表模块用于将测量得到的细延时器每个抽头输出对应的延时值进行计算并按大小排列储存到储存器中,在进行延时时,延时控制电路会向查找表模块查询细延时值对应的抽头;

7、所述的延时控制电路用于计算上位机或数字时间转换器以外的其他模块发送来的控制字为粗、细控制字并分别输入到粗延时器和查找表模块,所述的延时控制电路还接受来自查找表返回的细控制字对应的细延时抽头,并将其输入到细延时器中。

8、所述的粗延时器,按照系统时钟周期计数,达到粗延时控制信号对应值时释放粗延时信号。

9、所述的细延时器,采用抽头延迟链结构,延时路径由延迟单元级联而成的延迟链和选择输出抽头的选择器阵列组成;抽头延迟链采用延迟单元级联链,或者使用双链插值的延迟单元级联链;该抽头延迟链中选择任一抽头输出都有一对应唯一延迟时间,不同延迟时间排列后将系统时钟量化为至少50ps以下的时间间隔;

10、在校准状态下遍历每个抽头作为输出并测量其对应延迟时间,在延时状态下接受延时控制电路输入的抽头值,选择抽头值对应的抽头作为细延时信号输出。

11、所述的时间数字转换器,其测量精度大于所述的高精度数字时间转换器的延时精度。

12、所述的查找表模块,在校准状态下保存所述时间数字转换器的测量结果,并计算得到每个抽头输出的平均延时差,以此为依据排序并保存;在延时状态下,根据输入的细控制字输出对应的抽头值。

13、高精度数字时间转换包括以下步骤:

14、步骤1、搭建所述的高精度数字时间转换器的电路;

15、步骤2、系统上电或校准按键被触发,进入校准状态;

16、步骤3、选择相同的抽头重复输出相同延迟差的细延迟信号,重复次数为能够测得较为准确的抽头对应延迟差的任一合适值,每次测得的延迟差保存到ram中;

17、步骤4、改变输出抽头,重复步骤二,直至遍历所有抽头;

18、步骤5、计算每个抽头对应的延迟差并建立延迟时间对应抽头的查找表;

19、步骤6、进入延迟状态,按照上位机或数字时间转换器以外其他模块输入的控制字计算并输出粗延迟值和细延迟值,将细延迟值输入查找表模块得到返回的抽头值,将细延迟器的输出抽头设置为该值。

20、本发明的有益效果在于:本发明针对自动化测试设备(ate)应用领域需要输出高精度的可调节相位的激励信号的功能,提出了一种应用于自动测试设备的快速锁定宽可调范围高精度数字时间转换器,其也可被应用于其它合适场景。

21、常用的数字时间转换器往往难以实现同时兼顾快速锁定、宽可调范围和高精度的特性。例如使用多相参考时钟实现的数字时间转换器往往精度受限,而使用多周期时钟相位差的数字时间转换器在达到较好的延迟精度往往牺牲反应时间。

22、该转换器使用抽头延迟链与选择器阵列实现至少50ps以内的量化延时,并使用高精度时间数字转换器进行校准,可以显著减少抽头延迟链和选择器阵列结构的非线性。在校准完成后只需要根据设定的延迟值设置粗、细计数器即可完成延时设定,实现了快速锁定的特性。再通过粗、细延时器的两步式量化方法实现了宽可调范围,其覆盖的可调延时范围可达到粗延时器能够提供的最大计数周期数对应延迟时间。

技术特征:1.一种快速锁定的宽可调范围高精度数字时间转换器,其特征在于:包括粗延时器、细延时器、时间数字转换器、查找表模块、延时控制电路;

2.根据权利要求1所述的高精度数字时间转换器,其特征在于:所述的粗延时器,按照系统时钟周期计数,达到粗延时控制信号对应值时释放粗延时信号。

3.根据权利要求1所述的高精度数字时间转换器,其特征在于:所述的细延时器,采用抽头延迟链结构,延时路径由延迟单元级联而成的延迟链和选择输出抽头的选择器阵列组成;抽头延迟链采用延迟单元级联链,或者使用双链插值的延迟单元级联链;该抽头延迟链中选择任一抽头输出都有一对应唯一延迟时间,不同延迟时间排列后将系统时钟量化为至少50ps以下的时间间隔;

4.根据权利要求1所述的高精度数字时间转换器,其特征在于:所述的时间数字转换器,其测量精度大于所述的高精度数字时间转换器的延时精度。

5.根据权利要求4所述的高精度数字时间转换器,其特征在于:所述的查找表模块,在校准状态下保存所述时间数字转换器的测量结果,并计算得到每个抽头输出的平均延时差,以此为依据排序并保存;在延时状态下,根据输入的细控制字输出对应的抽头值。

6.根据权利要求1所述的高精度数字时间转换器,其特征在于:高精度数字时间转换包括以下步骤:

技术总结本发明公开了一种快速锁定的宽可调范围高精度数字时间转换器,包括粗延时器、细延时器、时间数字转换器、查找表模块、延时控制电路;粗延时器用于按照参考时钟产生粗延时信号,该信号接入细延时器进行进一步的细延时;细延时器用于将粗延时信号进一步的延时,输出为细延时信号,该信号被分别接到时间数字转换器的待测信号输入端口和系统输出IO上。本发明可以用于ATE设备产生高精度相位可调节激励信号,也可用于其它适合的高精度数字时间转换应用。技术研发人员:梅雪笑,韩雁,陈江华,夏吉品受保护的技术使用者:浙江大学技术研发日:技术公布日:2024/1/15本文地址:https://www.jishuxx.com/zhuanli/20240730/152162.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表