低频时码信号解码及标准时间输出装置的制作方法

- 国知局

- 2024-07-30 10:24:21

本技术属于电子测量,具体涉及到低频时码信号解码及标准时间输出装置。

背景技术:

1、我国的低频时码授时技术已在钟表行业得到广泛地应用,人们佩戴各种款式的电波钟手表、各类型室内挂钟、室外大钟和巨型塔钟均可接收低频时码信号并自动校时,但在电子政商务、测绘、教育、交通、国防等技术领域需要继续加大推广力度,必须研发更多相适应地低频时码用户的接收前端装置。一种能远距离移动可选择干扰较小区域并且快速可靠正确解码的低频时码接收装置,就能满足定时接收机和计算机网络时间服务器用户对时间精度的要求。

技术实现思路

1、本实用新型所要解决的技术问题在于为各种中等精度的用户时间服务器提供一种设计合理、抗干扰能力强、能耗低、时码信号可远距离传输、操作灵活简便的低频信号解码及标准时间输出装置。

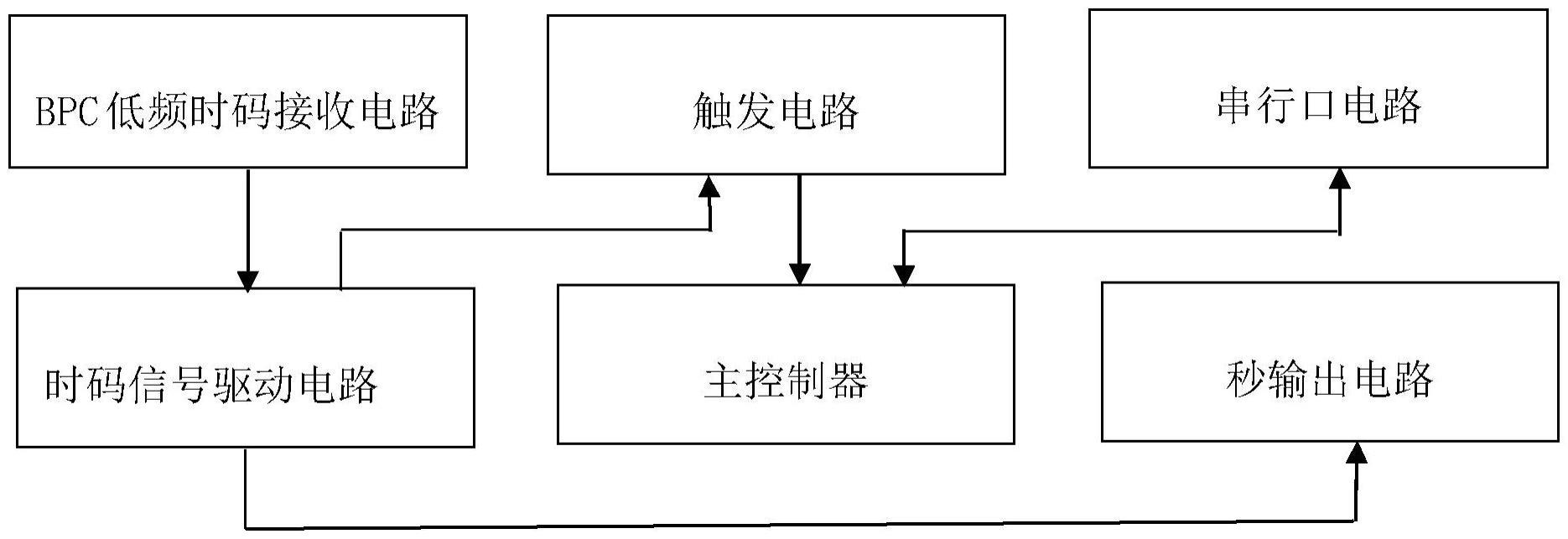

2、解决上述技术问题所采用的技术方案是:一种低频时码信号解码及标准时间输出装置,包括:bpc低频时码接收电路、时码信号驱动电路、触发电路、主控制器、秒输出电路;

3、所述bpc低频时码接收电路输出端与时码信号驱动电路相连,用于接收低频时码信号;

4、所述时码信号驱动电路的输出端与触发电路和秒输出电路相连,用于对bpc低频时码输出脉冲信号进行整形并驱动输出到触发电路的输入端,同时输出一定阻抗,使秒输出电路与时间用户的接口电路相匹配;

5、所述触发电路的输出端与主控制器相连,用于产生主控制器所需的中断申请信号;

6、所述主控制器,用于对触发电路状态的控制,测量出各个时码脉冲的宽度,根据编码规则解出标准时间码,并经过串行口电路输出到时间用户端;

7、所述秒输出电路,用于给时间用户提供的标准秒信号。

8、作为一种优选技术方案,所述主控制器上还连接有串行口电路,用于与时间用户端通信。

9、作为一种优选技术方案,所述bpc低频时码接收电路包括集成电路u2、电容c1、电感l1,集成电路u2的型号为t4227,集成电路u2的in1端接电容c1的一端和电感l1的一端、in2端接电容c1的另一端和电感l1的另一端、out端接时码信号驱动电路。

10、作为一种优选技术方案,所述时码信号驱动电路由集成电路u4构成,集成电路u4的型号为74hc14。

11、作为一种优选技术方案,所述触发电路包括集成电路u3、电阻r1,集成电路u3的型号为74hc74,集成电路u3的2脚、4脚、10脚、12脚并联并通过电阻r1接5v电源,集成电路u3的1脚、6脚、9脚、13脚接主控制器,集成电路u3的11脚、3脚接时码信号驱动电路。

12、作为一种优选技术方案,所述主控制器的型号为at89c2051。

13、作为一种优选技术方案,所述秒输出电路由集成电路u5构成,集成电路u5的型号为74128。

14、本实用新型的有益效果如下:

15、本实用新型抗干扰能力强、能耗低、实现时码信号远距离传输,本实用新型可灵活移动到干扰相对小的区域可靠工作,保证接收低频时码信号正常接收并正确解码。

技术特征:1.一种低频时码信号解码及标准时间输出装置,其特征在于,包括:bpc低频时码接收电路、时码信号驱动电路、触发电路、主控制器、秒输出电路;

2.根据权利要求1所述低频时码信号解码及标准时间输出装置,其特征在于,所述主控制器上还连接有串行口电路,用于与时间用户端通信。

3.根据权利要求1所述低频时码信号解码及标准时间输出装置,其特征在于,所述bpc低频时码接收电路包括集成电路u2、电容c1、电感l1,集成电路u2的型号为t4227,集成电路u2的in1端接电容c1的一端和电感l1的一端、in2端接电容c1的另一端和电感l1的另一端、out端接时码信号驱动电路。

4.根据权利要求1或2所述低频时码信号解码及标准时间输出装置,其特征在于,所述时码信号驱动电路由集成电路u4构成,集成电路u4的型号为74hc14。

5.根据权利要求4所述低频时码信号解码及标准时间输出装置,其特征在于,所述触发电路包括集成电路u3、电阻r1,集成电路u3的型号为74hc74,集成电路u3的2脚、4脚、10脚、12脚并联并通过电阻r1接5v电源,集成电路u3的1脚、6脚、9脚、13脚接主控制器,集成电路u3的11脚、3脚接时码信号驱动电路。

6.根据权利要求1或5所述低频时码信号解码及标准时间输出装置,其特征在于,所述主控制器的型号为at89c2051。

7.根据权利要求1所述低频时码信号解码及标准时间输出装置,其特征在于,所述秒输出电路由集成电路u5构成,集成电路u5的型号为74128。

技术总结低频时码信号解码及标准时间输出装置,包括:BPC低频时码接收电路、时码信号驱动电路、触发电路、主控制器、秒输出电路;BPC低频时码接收电路输出端与时码信号驱动电路相连,用于接收低频时码信号;时码信号驱动电路的输出端与触发电路和秒输出电路相连,用于对BPC低频时码输出脉冲信号进行整形并驱动输出到触发电路的输入端,同时输出一定阻抗,使秒输出电路与时间用户的接口电路相匹配;触发电路的输出端与主控制器相连,用于产生主控制器所需的中断申请信号;主控制器,用于对触发电路状态的控制,测量出各个时码脉冲的宽度,根据编码规则解出标准时间码,并经过串行口电路输出到时间用户端;秒输出电路,用于给时间用户提供的标准秒信号。技术研发人员:许林生,齐震,刘强,冯平,赵凡,黄璐希,任晓乾受保护的技术使用者:封开低频时码授时台技术研发日:20230728技术公布日:2024/1/15本文地址:https://www.jishuxx.com/zhuanli/20240730/152711.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表