基于差分延迟链的时间转换电路及芯片的制作方法

- 国知局

- 2024-07-30 10:26:07

本发明涉及属于时间数字转换器电路,具体而言涉及一种基于差分延迟链的时间转换电路及芯片。

背景技术:

1、时间数字转换器(time to digital convert,tdc)是一种对时间间隔进行测量,并将其转换为数字信号输出的器件,被广泛应用于高能物理、粒子物理、正电子断层扫描、自动测试设备、激光与超声波测量等诸多领域。实现高精度飞行时间测量主要有两大技术路径:

2、(1)高速、高精度adc(模拟-数字转换器)过采样,通过相关算法进行寻峰;

3、(2)延迟链技术,包括单端、游标、环状、流水线、flash等多种架构,对信号通过的逻辑单元个数进行锁存和累计。

4、第一种方法要求adc的采样吞吐率比信号频率高1-2个数量级以上,很可能在ghz或更高级别。这一方法带来的两个问题是:功耗极高(数十至数百倍)、成本极高(数百至数千元人民币),对于绝大多数应用场景来说是不可取的;

5、第二种方法,无论游标、环状、流水线,还是flash等架构,其核心部分都是基于单端延迟链的。受本地工艺变异(同一裸片上不同位置的延迟单元存在时间传播特性差异)和全局工艺变异(同一晶圆上不同位置的延迟单元存在时间传播特性差异)的影响,其时间分辨率及精度在很大程度上由延迟单元的一致性决定,符合正态分布规律。以当前极为成熟的工艺节点180-110nm为例,每个延迟单元的时间传播特性(时延分辨率)约为100ps,此处简化为精度±100ps。假定延迟链中包含n个延迟单元,每次测量均需遍历所有单元,则系统的整体累计精度(按照极值法)约为:±100ps*n数百至数千皮秒的精度等级,在实际应用中显然是远远不够的。

6、为解决上述问题,提升延迟链精度,目前采用的是筛选法,延迟单元的正负偏差,有一定几率刚好抵消。通过筛选,可以对芯片的时间精度进行分档(符合正态分布)。显然,达到数十皮秒精度的概率是比较低的,甚至可能达不到5%,因而高精度芯片的成本较高,实际应用比较困难。

技术实现思路

1、本发明目的在于提供一种基于差分延迟链的时间转换电路及芯片,采用差分延迟链系统架构,配合相应的内部测试与校准方法,可以大幅提升时间测量精度,同时在系统功耗和成本上则不会明显增加。

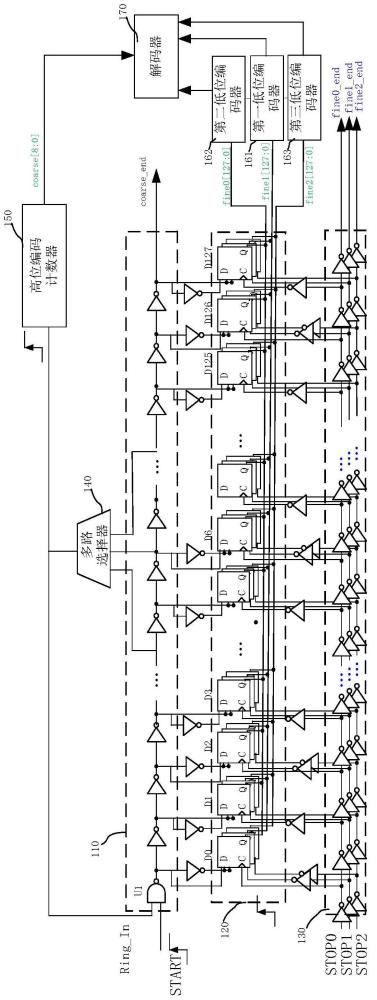

2、为达上述目的,本发明提出一种基于差分延迟链的时间转换电路,包括:粗延迟链、第一延迟链、第一触发器链、数据选择器、高位编码计数器、第一低位编码以及解码器。其中

3、粗延迟链包括首尾串联的n个粗延迟单元,粗延迟链的起始端接收开始信号start,所述n个粗延迟单元用于将接收到的start信号进行n级第一延时τ1处理,其中,n为不小于2的整数;

4、第一延迟链包括首尾串联的n个第一延迟单元,所述第一延迟链的起始端接收第一结束信号stop1,所述n个第一延迟单元用于将接收到的stop1进行n级第二延时τ2处理;

5、第一触发器链包括n个第一触发器,所述n个第一触发器的第一输入端分别一一对应连接至n个粗延迟单元的输出端,所述n个第一触发器的第二输入端分别一一对应连接至上述n个第一延迟单元的输出端;

6、所述数据选择器的输入分别连接至粗延迟链的第p级粗延迟单元以及第q级粗延迟单元的输出,所述数据选择器的输出反馈连接至粗延迟链的起始端ring_in,形成一环形振荡器,其中q≠p;

7、高位编码计数器的输入连接至所述数据选择器的输出端,用于记录所述start信号在环形振荡器中的循环次数;

8、第一低位编码器,所述第一低位编码器的各输入端对应连接至所述第一触发器链的n个第一触发器的输出端;

9、所述解码器的输入连接至所述高位编码计数器和所述第一低位编码器的输出,将所述高位编码计数器和所述第一低位编码器输入的数据解码为时间计数。

10、进一步,其中τ2<τ1,且所述n个第一触发器的数据输入端分别一一对应连接至n个粗延迟单元的输出端,所述n个第一触发器的时钟端分别一一对应连接至上述n个第一延迟单元的输出端。

11、进一步,其中,所述粗延迟链中第一级粗延迟单元是一个与非门,其余粗延迟单元是非门,且奇数级粗延迟单元的输出与上述各第一触发器的数据输入端之间通过一个非门对应连接,偶数级粗延迟单元的输出直接连接上述各第一触发器的数据输入端。

12、进一步,其中,所述第一延迟链的n级第一延迟单元是非门,且奇数级第一延迟单元通过一个额外的非门连接至对应的第一触发器的时钟端,偶数级第一延迟单元的输出直接连接至对应的第一触发器的时钟端。

13、进一步,其中,还包括第二延迟链、第二触发器链和第二低位编码器,第二延迟链包括首尾串联的n级第二延迟单元,n级第二延迟单元与上述第一延迟单元相同,延迟时间为τ2,所述数据选择器的输出连接至所述第二延迟链的起始端,所述第二触发器链的n个第二触发器的数据输入端分别一一对应连接至n个粗延迟单元的输出,第二触发器的时钟端分别一一对应连接至上述n个第二延迟单元的输出,第二低位编码器的各输入端对应连接至所述第二触发器链的n个第二触发器的输出端。

14、进一步,其中所述粗延迟链中第一级粗延迟单元是一个与非门,其余粗延迟单元是一个非门,且奇数级粗延迟单元的输出连接至所述第二触发器链的n个第二触发器的数据输入端,偶数级粗延迟单元的输出通过一个非门对应连接至n个第二触发器的数据输入端。

15、进一步,其中所述第二延迟链的n级第二延迟单元是非门,奇数级第二延迟单元的输出直接连接至对应的第二触发器的时钟端,偶数级第二延迟单元为通过一个额外的非门连接至对应的第二触发器的时钟端。

16、进一步,其中,还包括第三延迟链、第三触发器链和第三低位编码器,第三延迟链包括首尾串联的n级第三延迟单元,n级第三延迟单元与上述第二延迟单元完全相同,延迟时间为τ2,所述第三延迟链的起始端接收第二结束信号stop2,所述n个第三延迟单元用于将接收到的第二结束信号stop2进行n个第二延时τ2处理,所述第三触发器链的n个第三触发器的数据输入端分别一一对应连接至n个粗延迟单元的输出,所述第三触发器链的n个第三触发器的时钟端分别一一对应连接至上述n个第三延迟单元的输出,第三低位编码器的各输入端对应连接至所述第三触发器链的n个第三触发器的输出端。

17、进一步,其中,所述粗延迟链中第一级粗延迟单元是一个与非门,其余粗延迟单元是非门,且奇数级粗延迟单元的输出与各第三触发器的数据输入端之间通过一个非门对应连接,偶数级粗延迟单元的输出直接连接各第三触发器的数据输入端。

18、进一步,其中所述第三延迟链的n级第三延迟单元是非门,奇数级第三延迟单元通过一个额外的非门连接至对应的第三触发器的时钟端,偶数级第三延迟单元的输出直接连接至对应的第三触发器的时钟端。

19、进一步,其中所述粗延迟链、第一延迟链、第二延迟链以及第三延迟链中的延迟单元的数量均为128,且p、q为奇数。

20、本发明另提出一种基于差分延迟链的时间转换芯片,包括上述基于差分延迟链的时间转换电路。

21、本发明的时间转换电路及芯片,采用差分延迟链系统架构,配合相应的内部测试与校准方法,可以大幅提升测量精度至数十皮秒等级。

22、应当理解,前述构思以及在下面更加详细地描述的额外构思的所有组合只要在这样的构思不相互矛盾的情况下都可以被视为本公开的发明主题的一部分。另外,所要求保护的主题的所有组合都被视为本公开的发明主题的一部分。

23、结合附图从下面的描述中可以更加全面地理解本发明教导的前述和其他方面、实施例和特征。本发明的其他附加方面例如示例性实施方式的特征和/或有益效果将在下面的描述中显见,或通过根据本发明教导的具体实施方式的实践中得知。

本文地址:https://www.jishuxx.com/zhuanli/20240730/152876.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表