张量计算核心验证方法、装置、电子设备和存储介质与流程

- 国知局

- 2024-07-31 22:42:48

本技术涉及芯片设计验证,具体而言,涉及一种张量计算核心验证方法、装置、电子设备和存储介质。

背景技术:

1、张量计算核心(tensor core)是一种能高效执行矩阵乘法运算的微小核心。在图形处理器(graphics processing unit,gpu)中,张量计算核心通过高效地执行对神经网络算法至关重要的矩阵操作,为深度学习提供了显著的性能改进。这种改进使得深度学习模型的训练和推理时间更快,特别适用于诸如图像识别、自然语言处理和强化学习等任务。

2、相关技术通常是根据验证场景编写定向测试用例,静态配置后直接生成激励对张量计算核心进行验证,该方法无法适应不同验证场景的验证需求,灵活性和完备性差,验证效率低。

3、因此,如何提高张量计算核心验证的灵活性和完备性,提高验证效率成为业界亟待解决的技术问题。

技术实现思路

1、本技术提供一种张量计算核心验证方法、装置、电子设备和存储介质,用于解决如何提高张量计算核心验证的灵活性和完备性,提高验证效率的技术问题。

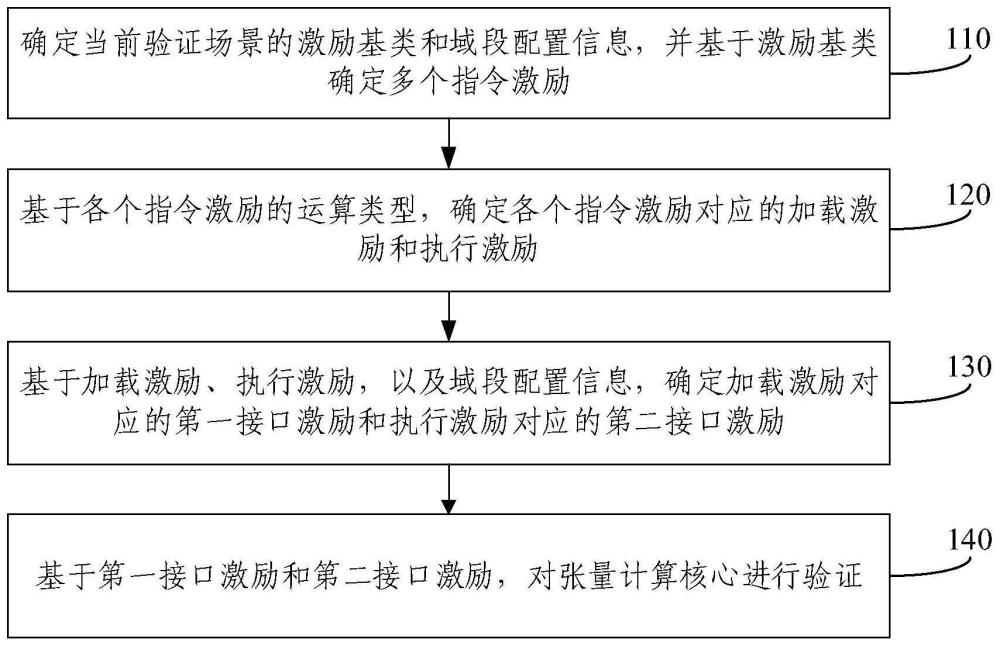

2、本技术提供一种张量计算核心验证方法,包括:

3、确定当前验证场景的激励基类和域段配置信息,并基于所述激励基类确定多个指令激励;

4、基于各个指令激励的运算类型,确定各个指令激励对应的加载激励和执行激励;

5、基于所述加载激励、所述执行激励,以及所述域段配置信息,确定所述加载激励对应的第一接口激励和所述执行激励对应的第二接口激励;

6、基于所述第一接口激励和所述第二接口激励,对张量计算核心进行验证。

7、在一些实施例中,所述指令激励对应的数据是基于如下步骤写入的:

8、基于上一指令激励在数据缓冲区中的数据结束地址和地址偏移量,确定当前指令激励在所述数据缓冲区中的数据起始地址;

9、基于所述当前指令激励在所述数据缓冲区中的数据起始地址,将所述当前指令激励对应的数据写入所述数据缓冲区;

10、在所述当前指令激励对应的数据的当前写入地址大于所述数据缓冲区的末地址的情况下,将所述数据缓冲区的首地址确定为所述当前写入地址对所述当前指令激励对应的数据进行写入;

11、基于所述当前指令激励对应的数据的写入结果,确定所述当前指令激励在数据缓冲区中的数据结束地址。

12、在一些实施例中,所述方法还包括:

13、确定当前指令激励的存储空间需求量,以及所述数据缓冲区中的存储空间剩余量;

14、在所述存储空间剩余量大于或者等于所述存储空间需求量的情况下,将所述当前指令激励对应的数据写入所述数据缓冲区;

15、基于所述当前指令激励对应的数据写入时间,确定所述当前指令激励对应的数据的地址的同步处理编号和写入时序编号;

16、将所述当前指令激励对应的数据在所述数据缓冲区中地址的空间可用状态设置为不可用;

17、基于所述当前指令激励对应的数据的写入时序编号,对已写入数据在所述数据缓冲区中地址的写入时序编号进行递增操作。

18、在一些实施例中,所述确定当前指令激励的存储空间需求量,以及所述数据缓冲区中的存储空间剩余量之后,所述方法还包括:

19、在所述存储空间剩余量大于或者等于所述存储空间需求量且所述同步处理编号数量有限的情况下,将所述当前指令激励对应的数据写入所述数据缓冲区;

20、将所述数据缓冲区中写入时序编号最大值的地址的同步处理编号确定为所述当前指令激励对应的数据的地址的同步处理编号;

21、将所述当前指令激励对应的数据在所述数据缓冲区中地址的空间可用状态设置为不可用;

22、确定所述当前指令激励对应的数据的写入时序编号,并对其余已写入数据在所述数据缓冲区中地址的写入时序编号进行递增操作。

23、在一些实施例中,所述确定当前指令激励的存储空间需求量,以及所述数据缓冲区中的存储空间剩余量之后,所述方法还包括:

24、在所述存储空间剩余量小于所述存储空间需求量的情况下,确定所述当前指令激励在所述数据缓冲区中的数据起始预测地址和数据结束预测地址;

25、基于所述数据起始预测地址和数据结束预测地址,确定所述当前指令激励对应的数据在所述数据缓冲区中的预测存储空间,以及所述预测存储空间中的目标已写入数据;

26、将所述当前指令激励对应的数据写入所述预测存储空间;

27、将所述目标已写入数据中写入时序编号最小值的的地址的同步处理编号确定为所述当前指令激励对应的数据的地址的同步处理编号;

28、将所述当前指令激励对应的数据在所述预测存储空间中的占用地址的空间可用状态设置为不可用;

29、确定所述当前指令激励对应的数据的写入时序编号,对其余已写入数据在所述数据缓冲区中地址的写入时序编号进行递增操作。

30、在一些实施例中,所述方法还包括:

31、构建同步处理编号队列,将未使用的同步处理编号加入所述同步处理编号队列;

32、将所述当前指令激励对应的数据写入所述数据缓冲区;

33、基于所述当前指令激励对应的数据写入时间,确定所述当前指令激励对应的数据的写入时序编号;

34、将所述同步处理编号队列中队首位置的同步处理编号确定为所述当前指令激励对应的数据的地址的同步处理编号;

35、将所述当前指令激励对应的数据在所述数据缓冲区中地址的空间可用状态设置为不可用;

36、基于所述当前指令激励对应的数据的写入时序编号,对已写入数据在所述数据缓冲区中地址的写入时序编号进行递增操作。

37、在一些实施例中,所述加载激励和执行激励是基于如下步骤调度的:

38、确定指令激励对应的各个加载激励和各个执行激励之间的数据依赖关系;

39、基于所述数据依赖关系,确定各个执行激励对应的目标加载激励;

40、在所述目标加载激励执行完成的情况下,对各个执行激励进行调度。

41、本技术提供一种张量计算核心验证装置,包括:

42、第一激励实例化单元,用于确定当前验证场景的激励基类和域段配置信息,并基于所述激励基类确定多个指令激励;

43、第二激励实例化单元,用于基于各个指令激励的运算类型,确定各个指令激励对应的加载激励和执行激励;

44、第三激励实例化单元,用于基于所述加载激励、所述执行激励,以及所述域段配置信息,确定所述加载激励对应的第一接口激励和所述执行激励对应的第二接口激励;

45、验证单元,用于基于所述第一接口激励和所述第二接口激励,对张量计算核心进行验证。

46、本技术提供一种电子设备,包括存储器、处理器及存储在所述存储器上并可在所述处理器上运行的计算机程序,所述处理器执行所述程序时实现所述的张量计算核心验证方法。

47、本技术提供一种非暂态计算机可读存储介质,其上存储有计算机程序,所述计算机程序被处理器执行时实现所述的张量计算核心验证方法。

48、本技术提供的张量计算核心验证方法、装置、电子设备和存储介质,确定当前验证场景的激励基类和域段配置信息,并根据激励基类确定多个指令激励;根据各个指令激励的运算类型,确定各个指令激励对应的加载激励和执行激励;根据加载激励、执行激励,以及域段配置信息,确定加载激励对应的第一接口激励和执行激励对应的第二接口激励;根据第一接口激励和第二接口激励,对张量计算核心进行验证;由于对张量计算核心进行验证的接口激励是根据对应的验证场景下的激励基类确定的,能够覆盖不同验证场景的验证需求,提高了张量计算核心验证的完备性;由于根据激励基类实例化指令激励,根据指令激励实例化加载激励和执行激励,最终确定接口激励,采用了多层级结构,便于对各个层级的激励进行动态配置,提高了张量计算核心验证的灵活性和扩展性,可以满足和支持不同验证场景的验证需求,提高了张量计算核心的验证效率。

本文地址:https://www.jishuxx.com/zhuanli/20240730/194240.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表