混合精度乘法电路的制作方法

- 国知局

- 2024-07-31 22:51:50

本发明是关于范围缩减电路(range reduction),特别是一种混合精度乘法电路。

背景技术:

1、科学应用经常使用超越数作为参数进行计算。然而,在浮点数格式中以硬件实现这种计算是一项挑战。例如:具有三角函数sin(x)的计算可能会用到y=x-2kπ的表达式,其中2kπ代表2π的倍数中小于x的最大者。若参数x很庞大,则很难计算出完全精确的y。如果希望精确地评估三角函数,必须使用精度达到x的指数范围的定点运算(fixed-pointarithmetic)来处理表达式。在上述例子中,如果x等于10200,那么k会是大约200位数的整数(在二进制形式中约为664位数),而且计算过程中要用到的π值在小数点后超过200位数。

2、给定两个输入a和b,其中a由指数ea和尾数ma表示,b由指数eb和尾数mb表示,则浮点乘法的执行包括:将尾数相乘(ma×mb),将指数相加(ea+eb),将乘法结果舍入(rounding),以及根据需要调整指数总和。乘法结果由指数总和与尾数总和表示。大部分硬件只有在a、b及乘法结果具有相同精度的情况下才能正常运作。一般来说,使用宽常数(例如上述例子中的k或π)进行乘法需要一个大型尾数乘法器和一个大型可变移位器(例如桶式移位器,barrel shifter)对结果进行标准化。然而,这种实现方式占用大量的电路面积而且具有高延迟。

技术实现思路

1、有鉴于此,本发明提出一种混合精度乘法电路以避免用到过宽的可变移位器,或是减少可变移位器的宽度。

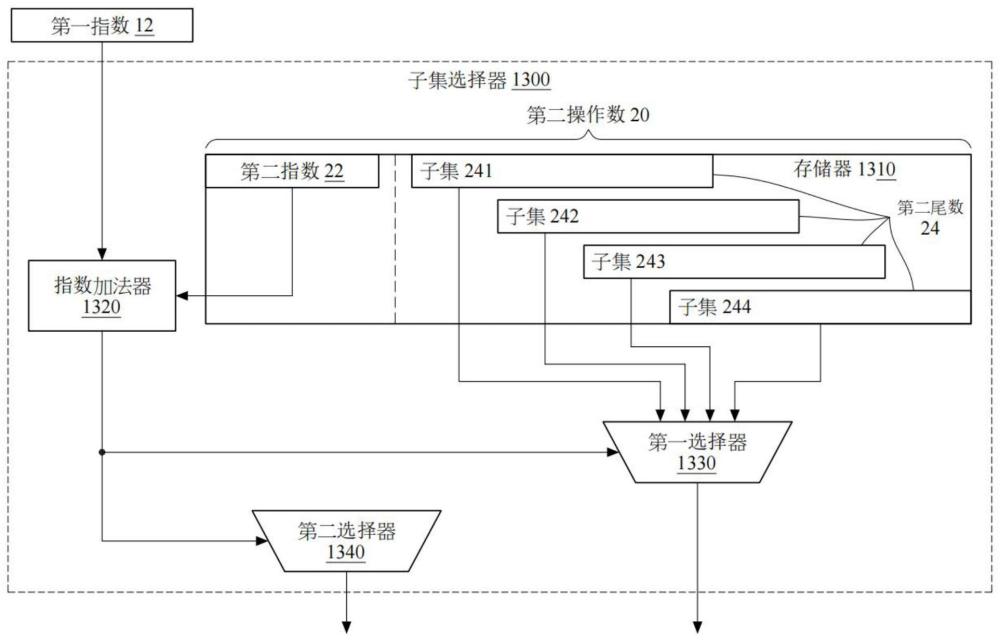

2、依据本发明一或多个实施例,一种混合精度乘法电路依据第一操作数及第二操作数计算。第一操作数包括指数及尾数。混合精度乘法电路包括子集选择器以及尾数乘法器。子集选择器用于存储第二操作数并接收指数。子集选择器依据指数从多个子集中输出所选子集,所述多个子集代表第二操作数。尾数乘法器耦合至子集选择器以接收关联于所选子集的被乘数,并用于接收尾数。尾数乘法器依据被乘数及尾数执行乘法以产生乘积,且混合精度乘法电路依据乘积输出结果。

3、依据本发明一或多个实施例,一种混合精度乘法电路依据第一操作数及第二操作数输出结果。第一操作数包括指数及尾数。混合精度乘法电路包括尾数乘法器以及子集选择器。尾数乘法器用于存储第二操作数并接收尾数。尾数乘法器依据第二操作数及尾数执行乘法以产生乘积。子集选择器耦合至尾数乘法器以接收乘积。子集选择器依据指数从多个子集中输出所选子集,每个子集的代表乘积的一部分。提取逻辑耦合至子集选择器以接收所选子集。提取逻辑从所选子集中提取一部分作为结果。

4、依据本发明一或多个实施例,一种混合精度乘法电路依据第一操作数及第二操作数计算。第一操作数包括指数及尾数。混合精度乘法电路包括部分乘积选择器以及部分乘积加法器。部分乘积选择器用于存储第二操作数及尾数倍数,其中:第二操作数被划分为多个子集,尾数倍数被划分为多个参考子集;每个子集包括多个数组,每个参考子集包括多个参考数组;每个数组为第二操作数依据一偏移量移位后的一部分;每个参考数组为尾数倍数依据一参考偏移量移位后的一部分;每个数组的采用的偏移量彼此不同,每个参考数组采用的参考偏移量彼此不同;部分乘积选择器依据指数从所述多个子集中选择一所需子集,并从所述多个参考子集中选择一所需参考子集;部分乘积选择器输出多个候选数组,每个候选数组的每一者是所需子集中的一数组或所需参考子集中的一参考数组。部分乘积加法器耦合至部分乘积选择器以接收所述多个候选数组,部分乘积加法器加总所述多个候选数组以输出结果。

5、为了对本新型的上述及其他方面有更佳的了解,下文特举实施例,并配合所附图式详细说明如下。

技术特征:1.一种混合精度乘法电路,其特征在于,依据第一操作数及第二操作数计算,其中该第一操作数包括一指数及一尾数,且该混合精度乘法电路包括:

2.如权利要求1所述混合精度乘法电路,其特征在于,该多个子集包括第一子集及第二子集,该第一子集包括第一部分作为该第二子集的第二部分。

3.如权利要求1所述混合精度乘法电路,其特征在于,该多个子集包括第一子集及第二子集,该第一子集包括第一部分,该第二子集包括第二部分,该第一子集的位元样式与该第二部分的位元样式相同。

4.如权利要求2所述混合精度乘法电路,其特征在于,该多个子集的每一者的位元宽度包括一基本宽度及一重叠宽度,该基本宽度关联于该第一操作数的该指数及该多个子集的数量,该重叠宽度是该第一部分的位元宽度或该第二部分的位元宽度。

5.如权利要求4所述混合精度乘法电路,其特征在于,该重叠宽度包括一尾数宽度及一结果宽度的总和。

6.如权利要求5所述混合精度乘法电路,其特征在于,该重叠宽度还包括与该乘积中潜在前导零的数量相关联的一保留宽度。

7.如权利要求5所述混合精度乘法电路,其特征在于,该重叠宽度还包括保留位元的宽度。

8.如权利要求5所述混合精度乘法电路,其特征在于:

9.如权利要求1所述混合精度乘法电路,其特征在于,还包括:

10.如权利要求1所述混合精度乘法电路,其特征在于,还包括:

11.一种混合精度乘法电路,其特征在于,依据第一操作数及第二操作数输出一结果,其中该第一操作数包括一指数及一尾数,且该混合精度乘法电路包括:

12.一种混合精度乘法电路,其特征在于,依据第一操作数及第二操作数计算,其中该第一操作数包括一指数及一尾数,且该混合精度乘法电路包括:

技术总结本发明提出一种混合精度乘法电路,该电路包含:第一操作数及第二操作数,第一操作数包括指数及尾数。混合精度乘法电路包括子集选择器及尾数乘法器。子集选择器用于存储第二操作数并接收指数。子集选择器依据指数从多个子集中选择一者,所述多个子集代表第二操作数。尾数乘法器耦合至子集选择器以接收关联于所选子集的被乘数,并用于接收尾数。尾数乘法器依据被乘数和尾数执行乘法以产生乘积,混合精度乘法电路依据乘积输出结果。技术研发人员:曾国增,黄家宁,欧瑞哲受保护的技术使用者:闳中股份有限公司技术研发日:技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240730/195045.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表