开发板和电子设备的制作方法

- 国知局

- 2024-08-01 00:12:42

本申请涉及电子的,尤其涉及一种开发板和电子设备。

背景技术:

1、随着芯片技术的发展,芯片功能多样化,随之出现数量较多的外设接口。众多外设接口的外观一致,且不同功能的接口分布混乱,用户使用不便。

技术实现思路

1、鉴于背景技术中存在的问题,本申请的目的在于提供一种开发板和电子设备,按照不同功能将多个外设接口进行划分,并设置于芯片对应的引脚附近,可以直观地展现芯片不同的外设接口所对应的功能。

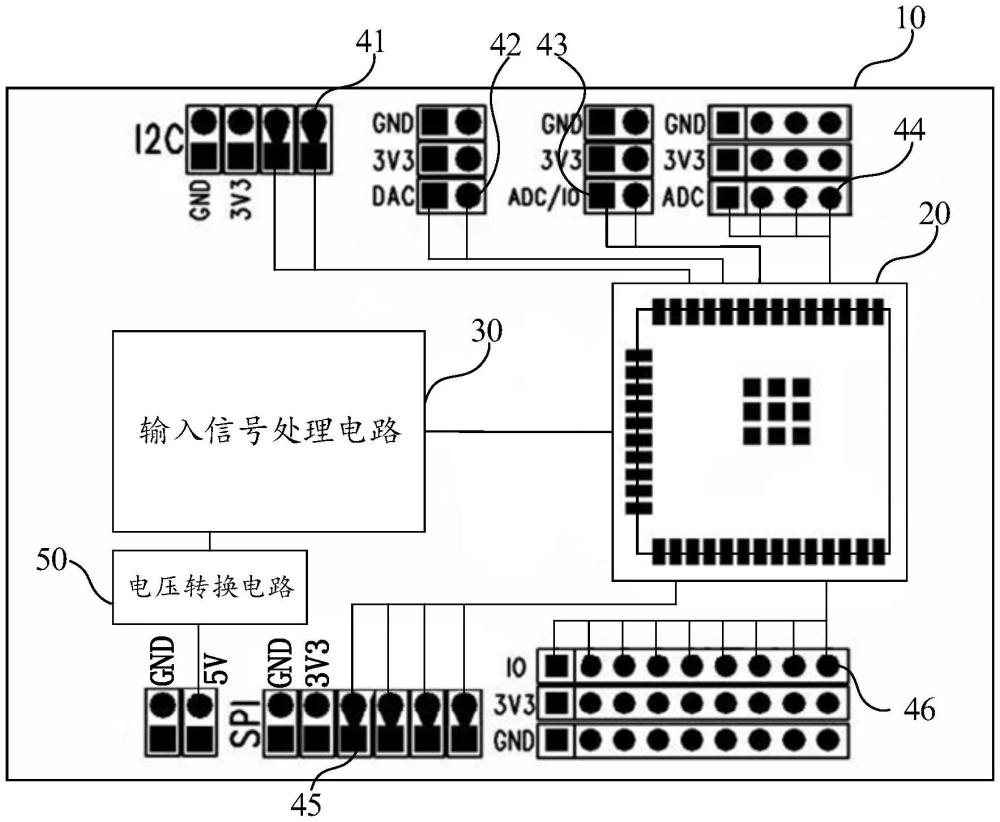

2、为达到上述目的,本申请提供了一种开发板,包括:电路板,具有长度方向和宽度方向;第一芯片,设置于所述电路板上;输入信号处理电路,与所述第一芯片连接,所述输入信号处理电路用于将接收到的第一数据转换为第二数据,以向所述第一芯片提供所述第二数据;多个i2c总线接口、多个dac接口、多个adc/io接口、多个adc接口、多个spi总线接口和多个数字io接口,均与所述第一芯片连接;其中,多个所述adc接口、所述第一芯片和多个所述数字io接口沿所述宽度方向依次间隔设置,多个所述i2c总线接口、多个所述dac接口、多个所述adc/io接口和多个所述adc接口沿所述长度方向依次间隔设置,多个所述spi总线接口和多个所述数字io接口沿所述长度方向依次间隔设置。

3、其中,所述输入信号处理电路和所述第一芯片位于所述电路板的中心线上,且沿所述长度方向间隔设置。

4、其中,所述多个所述i2c总线接口、所述输入信号处理电路和多个所述spi总线接口沿所述宽度方向间隔设置。

5、其中,所述i2c总线接口包括第一地引脚、第一电源引脚和第一接口引脚,每个所述i2c总线接口的所述第一地引脚、所述第一电源引脚和所述第一接口引脚沿所述长度方向依次排列,多个所述i2c总线接口的多个所述第一地引脚沿所述宽度方向依次排列,多个所述i2c总线接口的多个所述第一电源引脚沿所述宽度方向依次排列,多个所述i2c总线接口的多个所述第一接口引脚呈矩阵排列,且多个所述第一接口引脚沿所述宽度方向连通;所述dac接口包括所述第二地引脚、所述第二电源引脚和所述第二接口引脚,每个所述dac接口的所述第二地引脚、所述第二电源引脚和所述第二接口引脚沿所述宽度方向依次排列,多个所述dac接口的多个所述第二地引脚沿所述长度方向依次排列,多个所述dac接口的多个所述第二电源引脚沿所述长度方向依次排列,多个所述dac接口的多个所述第二接口引脚沿所述长度方向依次排列;所述adc/io接口包括所述第三地引脚、所述第三电源引脚和所述第三接口引脚,每个所述adc/io接口的所述第三地引脚、所述第三电源引脚和所述第三接口引脚沿所述宽度方向依次排列,多个所述adc/io接口的多个所述第三地引脚沿所述长度方向依次排列,多个所述adc/io接口的多个所述第三电源引脚沿所述长度方向依次排列,多个所述adc/io接口的多个所述第三接口引脚沿所述长度方向依次排列;所述adc接口包括所述第四地引脚、所述第四电源引脚和所述第四接口引脚,每个所述adc接口的所述第四地引脚、所述第四电源引脚和所述第四接口引脚沿所述宽度方向依次排列,多个所述adc接口的多个所述第四地引脚沿所述长度方向依次排列,多个所述adc接口的多个所述第四电源引脚沿所述长度方向依次排列,多个所述adc接口的多个所述第四接口引脚沿所述长度方向依次排列。

6、其中,所述spi总线接口包括第五地引脚、第五电源引脚和第五接口引脚,每个所述spi总线接口的所述第五地引脚、所述第五电源引脚和所述第五接口引脚沿所述长度方向依次排列,多个所述spi总线接口的多个所述第五地引脚沿所述宽度方向依次排列,多个所述spi总线接口的多个所述第五电源引脚沿所述宽度方向依次排列,多个所述spi总线接口的多个所述第五接口引脚呈矩阵排列,且多个所述第五接口引脚沿所述宽度方向连通;所述数字io接口包括所述第六接口引脚、所述第六电源引脚和所述第六地引脚,每个所述数字io接口的所述第六接口引脚、所述第六电源引脚和所述第六地引脚沿所述宽度方向依次排列,多个所述数字io接口的多个所述第六接口引脚沿所述长度方向依次排列,多个所述数字io接口的多个所述第六电源引脚沿所述长度方向依次排列,多个所述数字io接口的多个所述第六地引脚沿所述长度方向依次排列。

7、其中,所述开发板还包括电压转换电路,所述电压转换电路包括第二芯片、第一电容、第二电容、保险丝,所述第二芯片的第一引脚接地,所述第二芯片的第三引脚接收第一电压,所述第二芯片的第三引脚通过所述第一电容接地,所述第二芯片的第四引脚通过所述第二电容接地,所述第二芯片的第四引脚连接所述第二芯片的第二引脚,所述第二芯片的第二引脚通过所述保险丝输出第二电压;所述电压转换电路用于将所述第一电压转换为所述第二电压。

8、其中,所述输入信号处理电路包括第一接口、转换芯片和处理电路,所述第一接口通过所述转换芯片与所述处理电路连接,所述处理电路与所述第一芯片连接。

9、其中,所述处理电路包括第一电阻、第二电阻、第一三极管和第二三极管,所述第一电阻的第一端连接所述转换芯片的第一输出端,所述第一电阻的第二端连接所述第一三极管的基极,所述第一电阻的第一端连接所述第二三极管的发射极,所述第二电阻的第一端连接所述转换芯片的第二输出端,所述第二电阻的第二端连接所述第二三极管的基极,所述第二电阻的第一端连接所述第一三极管的发射极,所述第一三极管的集电极连接所述第一芯片的使能引脚,所述第二三极管的集电极连接所述第一芯片的第一io引脚。

10、其中,所述转换芯片包括第三芯片和第四芯片,所述第一接口通过所述第三芯片与所述第四芯片连接,所述第四芯片的第一输出端和第二输出端连接所述处理电路。

11、为达到上述目的,本申请还提供了一种电子设备,包括如上所述的开发板,所述开发板通过多个i2c总线接口、多个dac接口、多个adc/io接口、多个adc接口、多个spi总线接口和多个数字io接口中的至少一个接口与外部设备连接。

12、本申请实施例提供了一种开发板,包括:电路板,具有长度方向和宽度方向;第一芯片,设置于电路板上;输入信号处理电路,与第一芯片连接,输入信号处理电路用于将接收到的第一数据转换为第二数据,以向第一芯片提供第二数据;多个i2c总线接口、多个dac接口、多个adc/io接口、多个adc接口、多个spi总线接口和多个数字io接口,均与第一芯片连接;其中,多个adc接口、第一芯片和多个数字io接口沿宽度方向依次间隔设置,多个i2c总线接口、多个dac接口、多个adc/io接口和多个adc接口沿长度方向依次间隔设置,多个spi总线接口和多个数字io接口沿长度方向依次间隔设置。本申请按照不同功能将多个外设接口进行划分、排列,并设置于芯片对应的引脚附近,便于使用,也可以减少外设接口占用面积,缩小开发板的面积。此外,本申请通过输入信号处理电路实现第一数据的自动烧录和复位。

技术特征:1.一种开发板,其特征在于,包括:

2.根据权利要求1所述的开发板,其特征在于,所述输入信号处理电路和所述第一芯片位于所述电路板的中心线上,且沿所述长度方向间隔设置。

3.根据权利要求2所述的开发板,其特征在于,所述多个所述i2c总线接口、所述输入信号处理电路和多个所述spi总线接口沿所述宽度方向间隔设置。

4.根据权利要求1所述的开发板,其特征在于,所述i2c总线接口包括第一地引脚、第一电源引脚和第一接口引脚,每个所述i2c总线接口的所述第一地引脚、所述第一电源引脚和所述第一接口引脚沿所述长度方向依次排列,多个所述i2c总线接口的多个所述第一地引脚沿所述宽度方向依次排列,多个所述i2c总线接口的多个所述第一电源引脚沿所述宽度方向依次排列,多个所述i2c总线接口的多个所述第一接口引脚呈矩阵排列,且多个所述第一接口引脚沿所述宽度方向连通;

5.根据权利要求1所述的开发板,其特征在于,所述spi总线接口包括第五地引脚、第五电源引脚和第五接口引脚,每个所述spi总线接口的所述第五地引脚、所述第五电源引脚和所述第五接口引脚沿所述长度方向依次排列,多个所述spi总线接口的多个所述第五地引脚沿所述宽度方向依次排列,多个所述spi总线接口的多个所述第五电源引脚沿所述宽度方向依次排列,多个所述spi总线接口的多个所述第五接口引脚呈矩阵排列,且多个所述第五接口引脚沿所述宽度方向连通;

6.根据权利要求1-5任一项所述的开发板,其特征在于,所述开发板还包括电压转换电路,所述电压转换电路包括第二芯片、第一电容、第二电容、保险丝,所述第二芯片的第一引脚接地,所述第二芯片的第三引脚接收第一电压,所述第二芯片的第三引脚通过所述第一电容接地,所述第二芯片的第四引脚通过所述第二电容接地,所述第二芯片的第四引脚连接所述第二芯片的第二引脚,所述第二芯片的第二引脚通过所述保险丝输出第二电压;所述电压转换电路用于将所述第一电压转换为所述第二电压。

7.根据权利要求1所述的开发板,其特征在于,所述输入信号处理电路包括第一接口、转换芯片和处理电路,所述第一接口通过所述转换芯片与所述处理电路连接,所述处理电路与所述第一芯片连接。

8.根据权利要求7所述的开发板,其特征在于,所述处理电路包括第一电阻、第二电阻、第一三极管和第二三极管,所述第一电阻的第一端连接所述转换芯片的第一输出端,所述第一电阻的第二端连接所述第一三极管的基极,所述第一电阻的第一端连接所述第二三极管的发射极,所述第二电阻的第一端连接所述转换芯片的第二输出端,所述第二电阻的第二端连接所述第二三极管的基极,所述第二电阻的第一端连接所述第一三极管的发射极,所述第一三极管的集电极连接所述第一芯片的使能引脚,所述第二三极管的集电极连接所述第一芯片的第一io引脚。

9.根据权利要求8所述的开发板,其特征在于,所述转换芯片包括第三芯片和第四芯片,所述第一接口通过所述第三芯片与所述第四芯片连接,所述第四芯片的第一输出端和第二输出端连接所述处理电路。

10.一种电子设备,其特征在于,包括如权利要求1-9任一项所述的开发板,所述开发板通过多个i2c总线接口、多个dac接口、多个adc/io接口、多个adc接口、多个spi总线接口和多个数字io接口中的至少一个接口与外部设备连接。

技术总结本申请公开了一种开发板和电子设备,包括:电路板,具有长度方向和宽度方向;第一芯片,设置于电路板上;输入信号处理电路,与第一芯片连接,输入信号处理电路用于将接收到的第一数据转换为第二数据;多个I2C总线接口、多个DAC接口、多个ADC/IO接口、多个ADC接口、多个SPI总线接口和多个数字IO接口,均与第一芯片连接;其中,多个ADC接口、第一芯片和多个数字IO接口沿宽度方向依次间隔设置,多个I2C总线接口、多个DAC接口、多个ADC/IO接口和多个ADC接口沿长度方向依次间隔设置,多个SPI总线接口和多个数字IO接口沿长度方向依次间隔设置。本申请按照不同功能、第一芯片引脚位置,将多个外设接口进行划分、排列,可以减少外设接口的占用面积,缩小开发板的面积。技术研发人员:蔡德顺,张磊受保护的技术使用者:深圳市集慧技术有限公司技术研发日:20230921技术公布日:2024/7/11本文地址:https://www.jishuxx.com/zhuanli/20240730/200020.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表