一种ESD防护器件及微处理芯片的制作方法

- 国知局

- 2024-07-31 18:14:25

本申请涉及电子,具体地涉及一种esd防护器件及微处理芯片。

背景技术:

1、静电放电(e l ectro stat ic di scharge,esd)现象是指具有不同电势的物体相互靠近或接触时发生的电荷转移现象,由于放电时间极短,放电过程中会产生很大的电流;对于集成电路而言,现代芯片更容易受到esd引起的损坏,这种大电流会损伤甚至烧毁内部器件,导致芯片失效;芯片生产运输使用的各个环节都有可能出现静电放电现象,因此芯片的esd防护措施对于其可靠性是不可或缺的。

2、二极管直连触发的可控硅整流器(di rect connected s i l icon contro lled rect if ier,dcscr)是一种利用二极管串触发的scr器件,其具有电阻小、鲁棒性高等诸多优势,同时dcscr还可以通过器件堆叠来调整触发电压以满足不同设计窗口需求,广泛应用于先进工艺下的esd防护中。

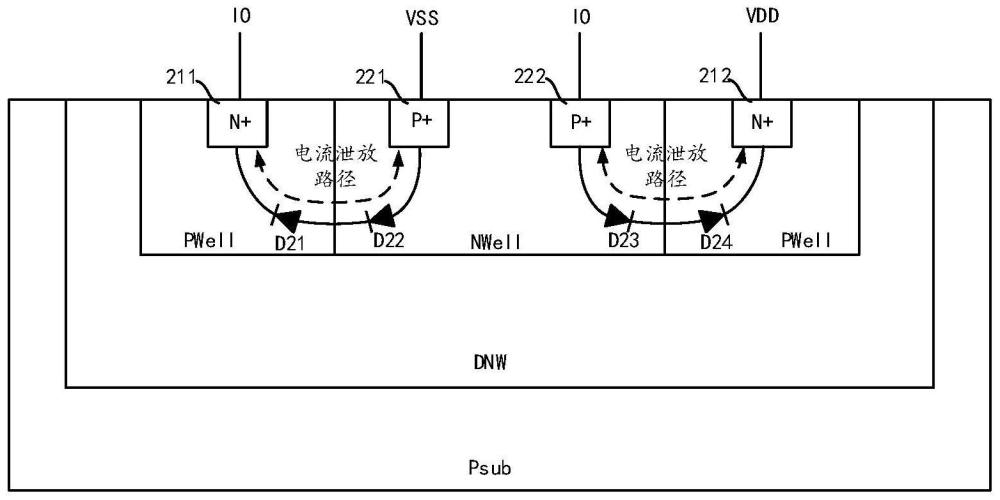

3、但是,现有技术中的dcscr器件用于esd防护时至少存在以下问题:1、布局不够紧凑,导致版图面积较大;2、只能用于两个端口之间一个方向(由阳极向阴极)的静电防护,不适用于全芯片。

4、需要指出的是,公开于本申请背景技术部分的信息仅仅旨在加深对本申请的一般背景技术的理解,而不应当被视为承认或以任何形式暗示该信息构成己为本领域技术人员所公知的现有技术。

技术实现思路

1、本申请提供一种esd防护器件及微处理芯片,以利于解决现有技术中esd防护器件布局不够紧凑,导致版图面积较大,以及只能用于两个端口之间一个方向的静电防护,不适用于全芯片的问题。

2、第一方面,本申请实施例提供了一种esd防护器件,包括:

3、a导电类型衬底;

4、b导电类型深阱区,所述b导电类型深阱区设置在所述a导电类型衬底内;

5、a导电类型阱区,所述a导电类型阱区设置在所述b导电类型深阱区内,且所述a导电类型阱区内设有第一b导电类型掺杂区、第二b导电类型掺杂区和第三a导电类型掺杂区;

6、b导电类型阱区,所述b导电类型阱区设置在所述b导电类型深阱区内,且所述b导电类型阱区内设有第一a导电类型掺杂区、第二a导电类型掺杂区和第三b导电类型掺杂区;

7、所述第一b导电类型掺杂区、所述第一a导电类型掺杂区、所述第二a导电类型掺杂区和所述第二b导电类型掺杂区依次沿第一方向排布,且分别沿第二方向延伸,所述第一方向和所述第二方向垂直;

8、所述第三a导电类型掺杂区和/或所述第三b导电类型掺杂区沿所述第一方向延伸,且所述第三a导电类型掺杂区和所述第三b导电类型掺杂区通过金属导线相连。

9、在一种可能的实现方式中,所述第三a导电类型掺杂区和/或所述第三b导电类型掺杂区沿所述第一方向延伸,具体包括:

10、所述第三a导电类型掺杂区沿所述第一方向延伸,且所述第三a导电类型掺杂区设置在所述第一b导电类型掺杂区、所述第一a导电类型掺杂区、所述第二a导电类型掺杂区和所述第二b导电类型掺杂区的第一端;

11、所述第三b导电类型掺杂区沿所述第一方向延伸,且所述第三b导电类型掺杂区设置在所述第一b导电类型掺杂区、所述第一a导电类型掺杂区、所述第二a导电类型掺杂区和所述第二b导电类型掺杂区的第二端。

12、在一种可能的实现方式中,所述第三a导电类型掺杂区还包括:

13、第一分支区域,所述第一分支区域沿所述第二方向延伸,且设置在所述第一b导电类型掺杂区远离所述第一a导电类型掺杂区的一侧;

14、第二分支区域,所述第二分支区域沿所述第二方向延伸,且设置在所述第二b导电类型掺杂区远离所述第二a导电类型掺杂区的一侧。

15、在一种可能的实现方式中,所述第三b导电类型掺杂区还包括:

16、第三分支区域,所述第一分支区域沿所述第二方向延伸,且设置在所述第一a导电类型掺杂区和所述第二a导电类型掺杂区之间。

17、在一种可能的实现方式中,所述第三a导电类型掺杂区和/或所述第三b导电类型掺杂区沿所述第一方向延伸,具体包括:

18、所述第三a导电类型掺杂区沿所述第二方向延伸,所述第三b导电类型掺杂区沿所述第一方向延伸。

19、在一种可能的实现方式中,所述第三a导电类型掺杂区,包括:

20、第一a导电类型掺杂子区域,所述第一a导电类型掺杂子区域设置在所述第一b导电类型掺杂区远离所述第一a导电类型掺杂区的一侧;

21、第二a导电类型掺杂子区域,所述第二a导电类型掺杂子区域设置在第二b导电类型掺杂区远离所述第二a导电类型掺杂区的一侧。

22、在一种可能的实现方式中,所述第三b导电类型掺杂区,包括:

23、第一b导电类型掺杂子区域,所述第一b导电类型掺杂子区域设置在所述第一b导电类型掺杂区、所述第一a导电类型掺杂区、所述第二a导电类型掺杂区和所述第二b导电类型掺杂区的第一端;

24、第二b导电类型掺杂子区域,所述第二b导电类型掺杂子区域设置在所述第一b导电类型掺杂区、所述第一a导电类型掺杂区、所述第二a导电类型掺杂区和所述第二b导电类型掺杂区的第二端。

25、在一种可能的实现方式中,所述第三b导电类型掺杂区,还包括:

26、第三b导电类型掺杂子区域,所述第三b导电类型掺杂子区域连接在所述第一b导电类型掺杂子区域和所述第二b导电类型掺杂子区域之间,沿所述第二方向延伸,且所述第三b导电类型掺杂子区域设置在所述第一a导电类型掺杂区和所述第二a导电类型掺杂区之间。

27、在一种可能的实现方式中,所述第三a导电类型掺杂区和/或所述第三b导电类型掺杂区沿所述第一方向延伸,具体包括:

28、所述第三a导电类型掺杂区沿所述第一方向延伸,所述第三b导电类型掺杂区沿所述第二方向延伸。

29、在一种可能的实现方式中,所述a导电类型为p型,所述b导电类型为n型;

30、或者,所述a导电类型为n型,所述b导电类型为p型。

31、第二方面,本申请实施例提供了一种微处理芯片,包括第一方面任一项所述的esd防护器件。

32、在本申请实施例中,采用简单紧凑的版图布局方式,实现了两个端口之间双向的esd防护,适用于全芯片。

技术特征:1.一种esd防护器件,其特征在于,包括:

2.根据权利要求1所述的esd防护器件,其特征在于,所述第三a导电类型掺杂区和/或所述第三b导电类型掺杂区沿所述第一方向延伸,具体包括:

3.根据权利要求2所述的esd防护器件,其特征在于,所述第三a导电类型掺杂区还包括:

4.根据权利要求2所述的esd防护器件,其特征在于,所述第三b导电类型掺杂区还包括:

5.根据权利要求1所述的esd防护器件,其特征在于,所述第三a导电类型掺杂区和/或所述第三b导电类型掺杂区沿所述第一方向延伸,具体包括:

6.根据权利要求5所述的esd防护器件,其特征在于,所述第三a导电类型掺杂区,包括:

7.根据权利要求5所述的esd防护器件,其特征在于,所述第三b导电类型掺杂区,包括:

8.根据权利要求7所述的esd防护器件,其特征在于,所述第三b导电类型掺杂区,还包括:

9.根据权利要求1所述的esd防护器件,其特征在于,所述第三a导电类型掺杂区和/或所述第三b导电类型掺杂区沿所述第一方向延伸,具体包括:

10.根据权利要求1-9任一项所述的esd防护器件,其特征在于,

11.一种微处理芯片,其特征在于,包括权利要求1-10任一项所述的esd防护器件。

技术总结本申请提供了一种ESD防护器件及微处理芯片,所述ESD防护器件包括:A导电类型衬底;B导电类型深阱区;A导电类型阱区,A导电类型阱区内设有第一B导电类型掺杂区、第二B导电类型掺杂区和第三A导电类型掺杂区;B导电类型阱区,B导电类型阱区内设有第一A导电类型掺杂区、第二A导电类型掺杂区和第三B导电类型掺杂区;第一B导电类型掺杂区、第一A导电类型掺杂区、第二A导电类型掺杂区和第二B导电类型掺杂区分别沿第二方向延伸;第三A导电类型掺杂区和/或第三B导电类型掺杂区沿第一方向延伸。在本申请实施例中,采用简单紧凑的版图布局方式,实现了两个端口之间双向的ESD防护,适用于全芯片。技术研发人员:许杞安受保护的技术使用者:上海领帆微电子有限公司技术研发日:技术公布日:2024/7/25本文地址:https://www.jishuxx.com/zhuanli/20240731/178440.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表