一种位线读取电路、存储器及电子设备的制作方法

- 国知局

- 2024-07-31 19:14:19

本技术涉及电路,尤其涉及一种位线读取电路、存储器及电子设备。

背景技术:

1、现有的计算系统中,动态随机存取存储器(dynamic random access memory,dram)作为内存,可以用于暂存中央处理器(central processing unit,cpu)的运算数据,以及与硬盘等外部存储器交换的数据。

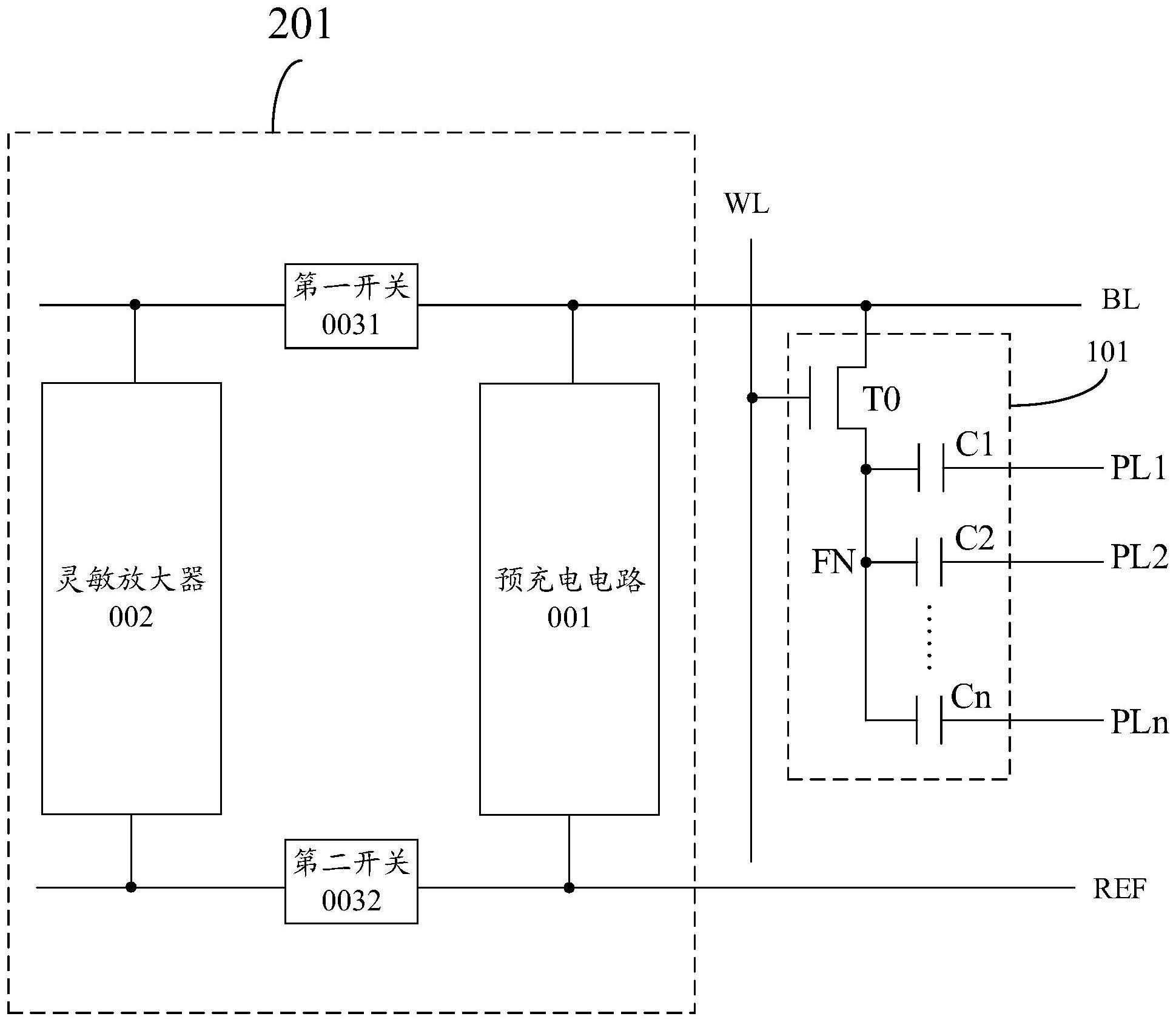

2、随着基于1t1c的dram的尺寸微缩逐渐碰到瓶颈,基于1tnc的铁电存储器(ferroelectric random access memory,feram)成为进一步提高dram集成密度的重要选项。如图1所示,在一个1tnc的储存单元中,n个铁电电容c1~cn的一端分别由n个板线(plate line)pl1~pln控制,这n个铁电电容c1~cn的另一端则连接到铁电存储单元内公共的节点fn,节点fn连到场效应晶体管(field effect transistor,fet)t0的源极一端,场效应晶体管t0的漏极一端连接到公共的位线(bit line,bl),场效应晶体管t0的栅极则连到字线(word line,wl)。铁电电容的信息可以通过位线bl上由于电荷变化而导致的电压变化并通过灵敏放大器(sense amplifier,sa)放大并读出。位线bl上电荷的变化主要来自非易失性的铁电电容受到超过矫顽场强度的电压时释放出来的极化电荷。

3、由于n个铁电电容c1~cn有一端连在了公共的节点fn上,为了区分这n个铁电电容c1~cn中的选中的铁电电容和未选中的n-1个铁电电容,未选中的铁电电容在读写过程中将承受“半选(half-select)”的外加电压vw/2,亦即选中铁电电容承受的电压vw的一半。通常“半选”电压vw/2小于矫顽场电压vc,所以未选中的铁电电容不会释放出显著的极化电荷。为了和传统双倍速率(double data rate,ddr)dram协议兼容,在一行铁电存储单元激活(activate)之后直至下一个预充电(precharge)命令之前,选中的铁电存储单元中的节点fn因为与灵敏放大器相连,将长时间处于0或者vw的电压状态,而未选中的板线pl处于vw/2,因此铁电存储单元中未选中的铁电电容(例如图1中c2~cn)将处于“半选”电压状态。但是如果铁电电容长时间处于“半选”电压下,铁电电容内在的自发极化强度也会受到明显的改变,进而影响到信息读取的窗口大小。为了改善铁电电容因长时间受到“半选”电压干扰而发生极化状态的改变,通常需要对铁电电容进行周期性的刷新操作。因此,如何减小铁电电容处于“半选”电压状态是本领域技术人员亟需解决的技术问题。

技术实现思路

1、本技术提供了一种位线读取电路、存储器及电子设备,用于改善1tnc铁电存储器在读写过程中铁电电容长时间处在“半选”状态。

2、第一方面,本技术实施例提供了一种位线读取电路,该位线读取电路用于从铁电存储单元中读取电平,该位线读取电路可以包括位线、参考线、预充电电、灵敏放大器、第一开关和第二开关。位线与铁电存储单元相连,铁电存储单元一般包括n个铁电电容和一个晶体管,其中n为大于或等于2的整数,晶体管的栅极与字线连接,晶体管的第一极与位线连接,晶体管的第二极与该n个铁电电容中每一铁电电容的一端连接,而每一铁电电容的另一端分别对应连接有一条板线。灵敏放大器分别与位线和参考线连接,用于对位线和参考线上的电压进行差分放大;预充电电路分别与位线和参考线连接,用于对位线和参考线预充电;第一开关连接于灵敏放大器与预充电电路之间的位线上,用于导通或者断开灵敏放大器与预充电电路间的位线;第二开关连接于灵敏放大器与预充电电路之间的参考线上,用于导通或者断开灵敏放大器与预充电电路之间的参考线。这样,该位线读取电路在读写阶段时,灵敏放大器正常工作,第一开关使灵敏放大器与预充电电路之间的位线断开,第二开关使灵敏放大器与预充电电路之间的参考线断开,从而位线可以被预充电电路拉到与铁电存储单元中未选中的铁电电容所连接的板线相同的电压,例如未选中的铁电电容所连接的板线上的电压为vw/2,那么位线就被预充电电路拉到vw/2,这样未选中的铁电电容的两端的电压就相同,从而在读写阶段不会处于“半选”状态,进而可以降低铁电电容处于“半选”状态的时间。

3、需要说明的是,在本技术中,预充电电路与灵敏放大器相比,预充电电路在位线上的连接位置更为靠近铁电存储单元,即铁电存储单元的信息通过位线先传输至预充电电路,然后通过第一开关传输至灵敏放大器;对应的,预充电电路充至参考线上的信号需要通过第二开关才能传输至灵敏放大器。

4、下面结合具体实施例,对本技术进行详细说明。需要说明的是,本实施例中是为了更好的解释本技术,但不限制本技术。

5、示例性的,在该位线读取电路中,第一开关可以包括第一晶体管,第一晶体管的栅极与第一隔离控制线连接,第一晶体管的第一极和第二极连接于灵敏放大器与预充电电路之间的位线上,当第一隔离控制线控制第一开关导通时,位线靠近预充电电路的一端与位线靠近灵敏放大器的一端导通,两端可以实现信号传输,当第一隔离控制线控制第一开关截止时,位线靠近预充电电路的一端与位线靠近灵敏放大器的一端断开,两端之间不能实现信号的传输,从而将预充电电路与灵敏放大器隔离开。

6、在具体实施时,第一晶体管可以是p型晶体管,也可以是n型晶体管,在此不作限定。当第一晶体管为p型晶体管时,第一隔离控制线为低电平时第一晶体管导通,第一隔离控制线为高电平时第一晶体管截止;当第一晶体管为n型晶体管时,第一隔离控制线为高电平时第一晶体管导通,第一隔离控制线为低电平时第一晶体管截止。

7、以上仅是举例说明第一开关的具体结构,在具体实施时,第一开关的具体结构不限于本技术实施例提供的上述结构,还可以是本领域技术人员可知的其他结构,在此不作限定。

8、示例性的,第二开关可以包括第二晶体管,第二晶体管的栅极与第二隔离控制线连接,第二晶体管的第一极和第二极连接于灵敏放大器与预充电电路之间的参考线上,当第二隔离控制线控制第二开关导通时,参考线靠近预充电电路的一端与参考线靠近灵敏放大器的一端导通,两端可以实现信号传输,当第二隔离控制线控制第二开关截止时,参考线靠近预充电电路的一端与参考线靠近灵敏放大器的一端断开,两端之间不能实现信号的传输,从而将预充电电路与灵敏放大器隔离开。

9、在具体实施时,第二晶体管可以是p型晶体管,也可以是n型晶体管,在此不作限定。当第二晶体管为p型晶体管时,第二隔离控制线为低电平时第二晶体管导通,第二隔离控制线为高电平时第二晶体管截止;当第二晶体管为n型晶体管时,第二隔离控制线为高电平时第二晶体管导通,第二隔离控制线为低电平时第二晶体管截止。

10、以上仅是举例说明第二开关的具体结构,在具体实施时,第二开关的具体结构不限于本技术实施例提供的上述结构,还可以是本领域技术人员可知的其他结构,在此不作限定。

11、可选的,第一晶体管和第二晶体管均为n型晶体管,当然,第一晶体管和第二晶体管也可以均为p型晶体管,这样在制造时第一晶体管和第二晶体管可以采用相同的工艺形成,从而减少工艺步骤,降低成本。

12、示例性的,当第一晶体管和第二晶体管均为n型晶体管或者均为p型晶体管时,第一隔离控制线与第二隔离控制线可以为同一控制线,即第一晶体管和第二晶体管同时被同一隔离控制线控制,从而可以减少控制线的数量,并且,第一晶体管和第二晶体管可以同步被控制,不需要额外设置同步控制电路,从而可以简化电路结构。

13、示例性的,灵敏放大器的差分输入分别接位线和参考线,灵敏放大器的差分输出分别接位线和参考线,以对位线和参考线上的电压进行差分放大。

14、示例性的,灵敏放大器可以包括:n型的第三晶体管、n型的第四晶体管、p型的第五晶体管和p型的第六晶体管;其中:第三晶体管的第一极与位线连接,第三晶体管的第二极与第一参考电压源连接,第三晶体管的栅极与参考线连接;第四晶体管的第一极与参考线连接,第四晶体管的第二极与第一参考电压源连接,第四晶体管的栅极与位线连接;第五晶体管的第一极与位线连接,第五晶体管的第二极与第二参考电压源连接,第五晶体管的栅极与参考线连接;第六晶体管的第一极与参考线连接,第六晶体管的第二极与第二参考电压源连接,第六晶体管的栅极与位线连接。

15、示例性的,预充电电路可以包括:第七晶体管和第八晶体管。其中:第七晶体管的第一极与位线连接,第七晶体管的第二极与预充电电压源连接,第七晶体管的栅极与预充电控制线连接;第八晶体管的第一极与预充电电压源连接,第八晶体管的第二极与参考线连接,第八晶体管的栅极与预充电控制线连接。

16、可选地,预充电电路中还可以包括第九晶体管。第九晶体管的第一极与位线连接,第九晶体管的第二极与参考线连接,第九晶体管的栅极与预充电控制线连接。当预充电电路工作时,导通的第九晶体管可以进一步保证位线和参考线上的电压相等。

17、可选地,在本技术实施例中,预充电电路中第七晶体管、第八晶体管和第九晶体管均为n沟道晶体管或者均为p沟道晶体管,在此不作限定。

18、可选地,在本技术实施例提供的位线读取电路中,还可以包括选择电路;选择电路与位线和参考线连接,用于读取位线和参考线上的数据,或者向位线和参考线写入数据。本技术的位线读取电路不仅可以实现数据的输出,还可以实现数据的写入。

19、示例性的,该选择电路可以包括第十晶体管和第十一晶体管。第十晶体管的第一极用于写入数据或者读取数据,第十晶体管的第二极与位线连接,第十晶体管的栅极与第一选择控制线连接,第十一晶体管的第一极用于写入数据或者读取数据,第十一晶体管的第二极与参考线连接,第十一晶体管的栅极与第二选择控制线连接。当选择电路工作时,第一选择控制线控制第十晶体管导通,从而通过导通的第十晶体管向位线写入数据或者读取位线上的数据。第二选择控制线控制第十一晶体管导通,从而通过导通的第十一晶体管向参考线写入数据或者读取参考线上的数据。

20、可选地,在本技术实施例中,位线读取电路连接的参考线可以为互补位线,一般选中的位线与互补位线所连接的铁电存储单元不连接同一字线,这样当位线读取电路读取选中的位线时,互补位线的电压不受其所连接的铁电存储单元影响。

21、需要说明的是,本技术对位线bl和互补位线/bl的位置不作限定,例如位线和互补位线可以是存储器中同一存储阵列中的两条位线,也可以是存储器中不同存储阵列中的两条位线。

22、需要说明的是,本技术上述实施例中提到的晶体管可以是薄膜晶体管(thin filmtransistor,tft),也可以是金属氧化物半导体场效应管(metal oxide semiconductorfield effect transistor,mosfet),在此不作限定。在具体实施时,晶体管的第一极和第二极中之一为源极,另一为漏极,晶体管的源极和漏极可以互换,不做具体区分。

23、可选地,本技术中,位线读取电路中还可以包括控制器;控制器用于在灵敏放大器对位线和参考线上的电压进行差分放大后进行输出时使第一开关和第二开关截止,以及在向位线和参考线写入数据时使第一开关和第二开关截止。

24、示例性的,该控制器还用于控制灵敏放大器和预充电电路,以使灵敏放大器对位线和参考线上的电压进行差分放大后输出,使预充电电路对位线和参考线预充电。

25、示例性的,该控制器还可以控制选择电路读取位线和参考线上的数据,或者控制选择电路向位线和参考线写入数据。

26、在具体实施时,控制器可以通过逻辑电路实现,本领域技术人员可以根据功能来得到具体的电路结构,在此不作限定。

27、进一步地,控制器可以在时序控制器的控制下第一开关、第二开关、预充电电路、灵敏放大器以及位线读取电路的工作时序。

28、第二方面,本技术实施例还提供了一种应用于如第一方面或第一方面的各种实施方式所述的位线读取电路的读取方法,该读取方法可以包括以下步骤:

29、第一阶段:第一开关和第二开关导通,预充电电路对位线和参考线预充电;

30、第二阶段:第一开关和第二开关导通,预充电电路关闭;

31、第三阶段:第一开关和第二开关导通,灵敏放大器对位线和参考线上的电压进行差分放大;

32、第四阶段:第一开关和第二开关截止,预充电电路对位线和参考线预充电;灵敏放大器将位线和参考线上的电压输出,或者向位线和参考线写入数据;

33、第五阶段:第一开关和第二开关导通,预充电电路关闭预设时间后打开。

34、下面结合时序对本技术实施例提供的位线读取电路的工作过程作以描述。

35、在①阶段(节点(铁电存储单元中晶体管的第二极)预充阶段),选中的铁电存储单元所连接的字线开启一段时间后关闭,在字线开启期间,节点、位线和参考线被预充电电路预充至0v。

36、在②阶段(铁电翻转阶段),位线和参考线被预充电电路预充至参考电压,同时选中的铁电电容所连接的板线上电压从vw/2上拉至vw,选中的铁电电容受到vw的压差,若铁电电容自身存储的数据与外加电场方向相反(数据“1”),铁电电容极化方向将发生翻转并释放出极化电荷,使得节点的电位明显抬升;若铁电电容自身存储的数据与外加电场方向相同(数据“0”),铁电电容极化方向不发生改变,节点电位抬升不明显。

37、在③阶段(电荷共享阶段),预充电电路关闭,选中的铁电存储单元所连接的字线再次打开,节点和位线的电荷共享,位线上的电位取决于节点的电位,位线的电位会上抬(数据“1”)或者下降(数据“0”)一定幅值,参考线则维持在参考电压,两者最终形成稳定的电压差。

38、在④阶段(灵敏放大阶段),将第一参考电压源下拉到0,第二参考电压源sap上拉到vw,灵敏放大电路开始工作,如果铁电存储单元中选中的铁电电容存储的数据为“1”,灵敏放大器将位线拉高为vw,参考线拉低为0。如果铁电存储单元中选中的铁电电容存储的数据为“0”,灵敏放大器将参考线拉高为vw,位线拉低为0。从而灵敏放大器实现对位线和参考线上的电压进行差分放大,进而读出选中的铁电电容存储的信息。

39、在⑤阶段(读写阶段),第一开关和第二开关截止,预充电电路打开,节点、第一开关右侧的位线和第二开关右侧的参考线被预充电电路预充至vw/2,如果是读取操作,第一开关左侧的位线和第二开关左侧的参考线则维持④阶段时的电压,如果为写操作,第一开关左侧的位线和第二开关左侧的参考线则被改写至新的电压。

40、在⑥阶段(回写阶段),第一开关和第二开关导通,预充电电路关闭预设时间后打开,与此同时板线下拉至0再回复至vw/2,节点,第一开关右侧的位线和第二开关右侧的参考线则被第一开关左侧的位线和第二开关左侧的互补位驱动至相应电位。如果节点电压为vw,则铁电电容将被回写成数据“1”;如果节点电压为0,则铁电电容将维持在数据“0”。随后字线wl关闭,完成回写阶段所有操作。

41、由上述工作过程可知,由于第一开关和第二开关的引入,在⑤阶段,节点、第一开关右侧的位线和第二开关右侧的参考线得以维持在vw/2,使得非选中的铁电电容两端压差为0,从而避免了在该阶段非选中铁电电容的“半选”电压干扰。

42、第三方面,本技术实施例还提供了一种存储器,包括铁电存储单元以及如第一方面或第一方面的各种实施方式所述的位线读取电路,铁电存储单元包括并联的多个铁电电容以及与多个铁电电容连接的晶体管,晶体管的栅极与字线连接,晶体管的第一极与位线连接,晶体管的第二极与并联的多个铁电电容连接。由于该存储器解决问题的原理与前述一种位线读取电路相似,因此该存储器的实施可以参见前述位线读取电路的实施,重复之处不再赘述。由于本技术提出的位线读取电路可以降低铁电电容处于“半选”状态的时间,因此包含该位线读取电路的存储器同样可以降低铁电电容处于“半选”状态的时间。

43、可选地,在本技术实施例中,存储器还可以包括控制逻辑,控制逻辑用于:导通铁电存储单元;将位线上的电平读出。本技术实施例中,控制逻辑可以是存储器中的控制器,在此不作限定。

44、第四方面,本技术实施例还提供了一种电子设备,包括处理器以及与所述处理器耦合的如第三方面所述的存储器。

45、具体地,处理器可以调用存储器中存储的软件程序,以执行相应的方法,实现电子设备的相应功能。

46、上述第三方面和第四方面可以达到的技术效果可以参照上述第一方面中任一可能设计可以达到的技术效果说明,这里不再重复赘述。

本文地址:https://www.jishuxx.com/zhuanli/20240731/181986.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表