EEPROM电路的制作方法

- 国知局

- 2024-07-31 19:29:02

本发明涉及半导体集成电路领域,特别是涉及一种eeprom电路。

背景技术:

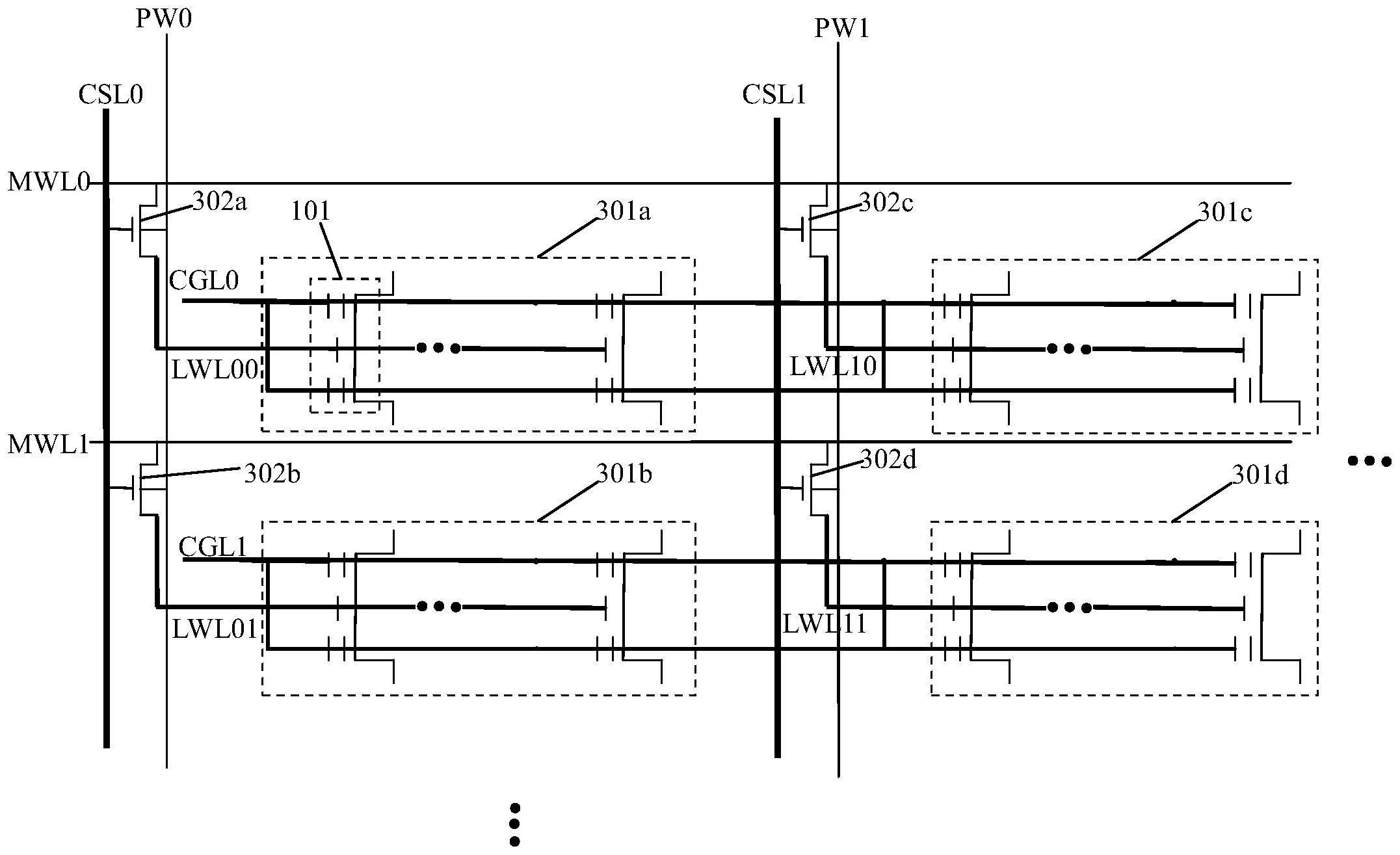

1、如图1所示,是现有eeprom的存储单元101的电路结构示意图;如图2所示,是现有eeprom的存储单元101的剖面结构示意图;如图3所示,是现有eeprom的阵列结构图;现有eeprom包括多个存储单元101,由多个所述存储单元101组成阵列单元,由多个所述阵列单元排列形成eeprom的阵列结构。

2、各所述存储单元101都采用分离栅浮栅器件。

3、如图2所示,所述分离栅浮栅器件包括:源区205和漏区206,位于所述源区205和所述漏区206之间的多个分离的具有浮栅104的第一栅极结构,位于所述第一栅极结构之间的第二栅极结构103;所述第一栅极结构中具有位于所述浮栅104顶部的控制栅105。

4、所述分离栅浮栅器件为双分离栅浮栅器件,所述第一栅极结构的数量为两个,分别用标记102a和102b表示。

5、所述分离栅浮栅器件为n型器件,所述源区205和所述漏区206都由n+区组成。

6、p型掺杂的沟道区位于所述源区205和所述漏区206之间且被各所述第一栅极结构和所述第二栅极结构103所覆盖。所述源区205和所述漏区206都形成于p型半导体衬底201且和对应的两个所述第一栅极结构的外侧面自对准,所述沟道区之间由所述源区205和所述漏区206之间的所述p型半导体衬底201组成或者进一步在所述p型半导体衬底201上进行掺杂形成。

7、所述存储单元101的所述漏区206连接到漏极d。

8、所述存储单元101的所述源区205连接源极s。

9、各所述第一栅极结构由隧穿介质层202、所述浮栅104、控制栅介质层203和所述控制栅105叠加而成。

10、各所述第二栅极结构103由字线栅介质层204和字线栅106叠加而成。

11、所述控制栅105连接到控制栅线cg,所述字线栅106连接到字线wl。

12、对所述存储单元101进行擦除(erase)时:

13、所述控制栅线cg接负擦除电压。

14、所述字线wl接正擦除电压。

15、所述漏极d和所述源极s都接0v。

16、所述负擦除电压和所述正擦除电压的电压差使各所述浮栅104中的存储电荷被擦除。

17、表一中给出了现有存储器中对所述存储单元101进行操作时的具体参数:

18、表一

19、 操作 cg(v) wl(v) s(v) d 擦除 -7 8 0 0

20、表一中,所述负擦除电压等于-7v,所述正擦除电压等于8v。

21、所述阵列单元中:各所述存储单元101排列成一行,各所述存储单元101的所述第二栅极结构103都连接对应的本地字线(local word line,lwl);各所述阵列单元的所述本地字线独立设置。图3中显示了4根所述本地字线,分别用lwl00、lwl10、lwl01和lwl11表示。

22、通常,所述阵列单元中所述存储单元101的数量包括8个即一个字节(byte)。

23、所述阵列结构中:各所述阵列单元排列形成行和列,同一行的所述阵列单元排列成阵列单元行,同一列的所述阵列单元排列成阵列单元列。

24、所述阵列结构中设置有选择管、主字线(main word line,mwl)和选择信号线(csl)。图3中,显示了4个所述选择管,分别用标记302a、302b、302c和302d表示;显示了两根所述主字线,分别用标记mwl0和mwl1表示;显示了两根所述选择信号线,分别用标记csl0和csl1表示。

25、所述主字线为行线,所述主字线的行数和所述阵列单元行的行数相同,各行所述主字线为相同行的所述阵列单元行中的各所述阵列单元共用,例如:所述主字线mwl0为第一行的所述阵列单元301a和301c共用,所述主字线mwl1为第二行的所述阵列单元301b和301d共用。

26、所述选择信号线为列线,所述选择信号线的列数和所述阵列单元列的列数相同,各列所述选择信号线为相同列的所述阵列单元列中的各所述阵列单元共用。例如:所述选择信号线csl0为第一列的所述阵列单元301a和301b共用,所述选择信号线csl1为第二列的所述阵列单元301c和301d共用。

27、所述选择管的数量和所述阵列单元的数量相同,各所述阵列单元分别和一个选择管相对应。例如:所述选择管302a和所述阵列单元301a相对应,所述选择管302b和所述阵列单元301b相对应,所述选择管302c和所述阵列单元301c相对应,所述选择管302d和所述阵列单元301d相对应。

28、各所述阵列单元的所述本地字线分别通过对应的所述选择管连接到对应的所述主字线;各所述选择管为nmos管,所述选择管的第一沟道区由第一p型体区组成,所述第一p型体区和体电极相连。各所述选择管的源极连接到对应的所述阵列单元的所述本地字线。

29、所述主字线为行线,所述选择信号线和所述体电极线都为列线。

30、同一行的各所述选择管的漏极连接到同一行对应的所述主字线。

31、同一列的各所述选择管的栅极连接到同一列对应的所述选择信号线。

32、令选定的所述阵列单元为选定单元,未选定的所述阵列单元为非选定单元。

33、对所述选定单元进行擦除时具有如下电压设置:

34、所述选定单元的列对应所述选择信号线加选择信号,使所述选定单元对应的所述选择管导通;和所述选定单元的列不同的各所述选择信号线加0v电压,使和所述选定单元的不同列的各所述非选定单元对应的所述选择管关断。

35、所述选定单元的行对应的所述主字线加正擦除电压;所述选择信号的电压大于所述正擦除电压,例如:所述选择信号的电压大小为10v,所述正擦除电压大小为8v。

36、图3中,各所述选择管的体电极都接地。

37、和所述选定单元的行不同的各所述主字线加0v。

38、所述阵列单元中,各所述存储单元101的所述控制栅都连接到对应的控制栅线。在所述阵列结构中,同一行的所述阵列单元共用同一行的所述控制栅线。图3中显示了两条所述控制栅线,分别用cgl0和cgl1表示。在所述擦除过程中,所述选定单元对应的所述控制栅线接负擦除电压。

39、由图3所示可知,以所述阵列单元301a为所述选定单元为例,擦除时所加电压为:

40、mwl0加所述正擦除电压,如8v。

41、mwl1和csl1都加0v。

42、csl0加所述选择信号,如10v。

43、csl0会使第一列的所述选择管导通,所述选择管302a会导通,但是,由于所述选择管302a的体电极接地,会使得所述选择管302a的源极电压下降为7.5v,这是因为,源极和体电极之间具有较大的电压差,这个电压差对应n+源区和p型的体区形成的二极管来说是反偏电压,较大的反偏电压最后会所述选择管302a的导通性能受到影响,从而使源漏电压增加,故源极电压会下降。所以,所述选择管302的源极电压不能达到漏极的8v,这样lwl00就只为7.5v,不能达到设定的8v,故擦除效率会降低。

44、由于csl1为0v,故第二列的各所述选择管都断开,对应的源极都是浮置(floating)状态,如所述选择管302c和302d的源极都是浮置状态。

45、由于mwl1为0v,故即使第一列的第二行的所述选择管302b导通,所述选择管302b的源极为0v。

技术实现思路

1、本发明所要解决的技术问题是提供一种eeprom电路,能对选择管的体电极进行偏置控制且在擦除时能通过对选择管的体电极的偏置控制消除由于选择管的源极和体电极的压差过大而产生源极电压过低,从而能提高选定单元的本地字线的电压并从而提高擦除效应。

2、为此,本发明提供的eeprom电路包括多个存储单元,由多个所述存储单元组成阵列单元,由多个所述阵列单元排列形成eeprom的阵列结构。

3、各所述存储单元都采用分离栅浮栅器件。

4、所述分离栅浮栅器件包括:源区和漏区,位于所述源区和所述漏区之间的多个分离的具有浮栅的第一栅极结构,位于所述第一栅极结构之间的第二栅极结构;所述第一栅极结构中具有位于所述浮栅顶部的控制栅。

5、所述阵列单元中:各所述存储单元排列成一行,各所述存储单元的所述第二栅极结构都连接对应的本地字线;各所述阵列单元的所述本地字线独立设置。

6、所述阵列结构中:各所述阵列单元排列形成行和列,同一行的所述阵列单元排列成阵列单元行,同一列的所述阵列单元排列成阵列单元列。

7、所述阵列结构中设置有选择管、主字线、选择信号线和体电极线。

8、各所述阵列单元分别和一个选择管相对应,各所述阵列单元的所述本地字线分别通过对应的所述选择管连接到对应的所述主字线;各所述选择管为nmos管,所述选择管的第一沟道区由第一p型体区组成,所述第一p型体区和体电极相连。

9、各所述选择管的源极连接到对应的所述阵列单元的所述本地字线。

10、所述主字线为行线,所述选择信号线和所述体电极线都为列线。

11、同一行的各所述选择管的漏极连接到同一行对应的所述主字线。

12、同一列的各所述选择管的栅极连接到同一列对应的所述选择信号线。

13、同一列的各所述选择管的体电极连接到同一列对应的所述体电极线。

14、令选定的所述阵列单元为选定单元,未选定的所述阵列单元为非选定单元。

15、对所述选定单元进行擦除时具有如下电压设置:

16、所述选定单元的列对应所述选择信号线加选择信号,使所述选定单元对应的所述选择管导通;和所述选定单元的列不同的各所述选择信号线加0v电压,使和所述选定单元的不同列的各所述非选定单元对应的所述选择管关断。

17、所述选定单元的行对应的所述主字线加正擦除电压;所述选择信号的电压大于所述正擦除电压。

18、所述选定单元的列对应所述体电极线加正偏置电压,所述正偏置电压小于所述正擦除电压,和所述选定单元的列不同的各所述体电极线加0v电压,通过所述正偏置电压的设置减少所述选定单元对应的所述选择管的所述第一p型体区和n+的第一源区之间的偏压,从而提高所述选定单元对应的所述本地字线的电压。

19、和所述选定单元的行不同的各所述主字线加所述正偏置电压。

20、进一步的改进是,所述阵列单元中,各所述存储单元的所述控制栅都连接到对应的控制栅线。

21、进一步的改进是,所述正偏置电压采用所述eeprom的电源电压。

22、进一步的改进是,所述选择信号的电压由对应的电荷泵提供;所述正擦除电压由对应的电荷泵提供。

23、进一步的改进是,所述正擦除电压达8v以上。

24、进一步的改进是,所述选择信号的电压达10v以上。

25、进一步的改进是,所述阵列单元中所述存储单元的数量包括8个。

26、进一步的改进是,所述分离栅浮栅器件为双分离栅浮栅器件,所述第一栅极结构的数量为两个。

27、进一步的改进是,所述分离栅浮栅器件为n型器件,所述源区和所述漏区都由n+区组成。

28、p型掺杂的沟道区位于所述源区和所述漏区之间且被各所述第一栅极结构和所述第二栅极结构所覆盖。

29、进一步的改进是,在所述擦除过程中,各所述存储单元的源区和漏区都接地。

30、进一步的改进是,在所述阵列结构中,同一行的所述阵列单元共用同一行的所述控制栅线。

31、进一步的改进是,在所述擦除过程中,所述选定单元对应的所述控制栅线接负擦除电压。

32、进一步的改进是,各所述第一栅极结构由隧穿介质层、所述浮栅、控制栅介质层和所述控制栅叠加而成。

33、各所述第二栅极结构由字线栅介质层和字线栅叠加而成。

34、进一步的改进是,所述浮栅的材料包括多晶硅,所述控制栅的材料包括多晶硅,所述字线栅的材料包括多晶硅。

35、进一步的改进是,所述隧穿介质层的材料包括氧化层,所述控制栅介质层的材料包括氧化层,所述字线栅介质层的材料包括氧化层。

36、现有电路中,选定单元的选择管的体电极直接接地,而选择管的漏极是接较高的正擦除电压,源极电压为漏极电压传递而来,故选择管的源极和漏极电压都比体电极的电压大很多,选择管的体区反偏较大即体区和源区以及体区和漏区之间的都有较大的反偏,这会使源漏电压增加,使得源极电压相对于漏极电压下降较大,从而使得选择管的源极提供到本地字线的正擦除电压变小,从而影响擦除效率;本发明中,在阵列结构中增加设置了列排列的体电极线,各列选择管的体电极也即背栅电极连接到体电极线,在进行擦除时,对体电极线的电压也做了特别的设置,将选定单元所在列对应的体电极线的电压设置为正偏置电压,正偏置电压大于0v以及小于主字线所提供的正擦除电压,由于选定单元的本地字线的电压需要通过选择管从主字线的正擦除电压传递过来,正偏置电压设置后能降低选择管的第一源区和第一p型体区之间的压差,故能减少选择管的源漏电压,使得选择管的源极电压得到提高,使得选择管的漏极连接的正擦除电压能很好的传递到本地字线,从而提高擦除效率。

本文地址:https://www.jishuxx.com/zhuanli/20240731/182707.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表