一种内存条测试方法、装置、电子设备及介质与流程

- 国知局

- 2024-07-31 19:44:36

本发明涉及内存条测试领域,尤其涉及一种内存条测试方法、装置、电子设备及介质。

背景技术:

1、随着半导体行业的飞速发展,内存条行业也逐渐成熟。多样的组成导致了内存条的失效模式不再像内存颗粒那样简单明了,容易定位和分析。

2、内存条的失效需要根据实际失效情况多方面排查,通过还原失效的实际应用场景,多方位进行分析、复现,进而找到内存条真正失效的原因,现有技术可以找出真正失效的原因,但是实现的成本过高,导致行业内的工程师在实际工作中浪费了大量时间,也浪费了大量资源。因此,以较低成本实现一套全面的测试方法是极其必要的。

技术实现思路

1、本发明所要解决的技术问题是:如何设计出一种内存条测试方法,能够以较低成本实现一套全面的测试方法。

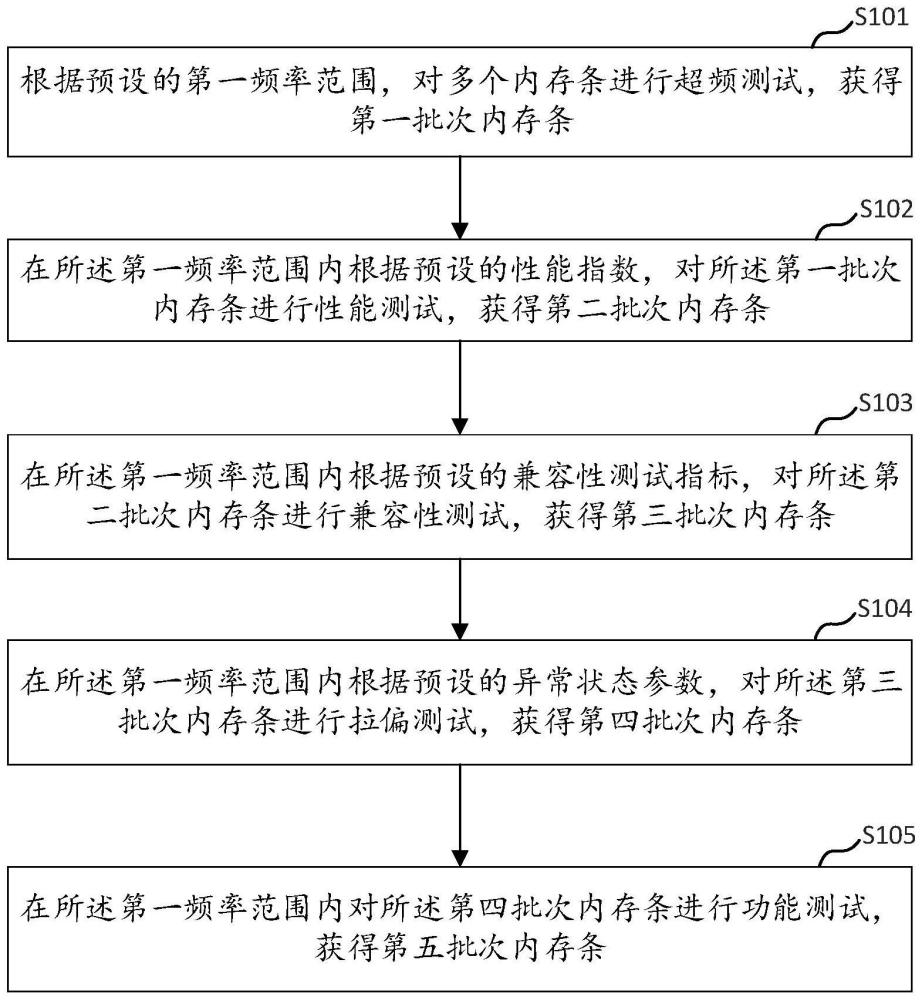

2、为解决上述问题,本发明实施例提出一种内存条测试方法、装置、电子设备及介质,现有技术中检测出内存条真正失效的原因需要耗费大量时间且效率低下,发明人研究发现其原因在于检测方案当中的检测路线不合理;本申请所述方案中的检测路线为首先通过超频测试实现内存条样本的预处理,然后通过性能测试和兼容性测试将最容易出现异常的因素作为排除条件,接着对余下的内存条样本进行拉偏测试以实现进阶测试,最后只选择通过了进阶测试的内存条样本进行功能测试,内存条不会因不合理的检测路线而导致资源浪费或效率低下,显著降低了内存条的测试成本。

3、第一方面,本发明提出一种内存条测试方法,所述方法包括:

4、根据预设的第一频率范围,对多个内存条进行超频测试,获得第一批次内存条,所述第一批次内存条为在所述预设的第一频率范围的条件下顺利通过所述超频测试的内存条;在所述第一频率范围内根据预设的性能指数,对所述第一批次内存条进行性能测试,获得第二批次内存条,所述第二批次内存条为在所述预设的性能指数下顺利通过所述性能测试的内存条;在所述第一频率范围内根据预设的兼容性测试指标,对所述第二批次内存条进行兼容性测试,获得第三批次内存条,所述第三批次内存条为在所述预设的兼容性测试指标下顺利通过所述兼容性测试的内存条;在所述第一频率范围内根据预设的异常状态参数,对所述第三批次内存条进行拉偏测试,获得第四批次内存条,所述第四批次内存条为在预设的异常状态参数下顺利通过所述拉偏测试的内存条;在所述第一频率范围内对所述第四批次内存条进行功能测试,获得第五批次内存条,所述第五批次内存条为在所述功能测试中未出现失效和/或故障的内存条;其中,所述功能测试包括失效分析测试。

5、其进一步的技术方案为,在所述第一频率范围内对所述第五批次内存条进行场景切换测试,获得第六批次内存条,所述第六批次内存条为在所述场景切换测试中未出现失效和/或故障的内存条;其中,所述场景切换测试包括启动、重启以及睡眠之间的切换测试。

6、其进一步的技术方案为,在所述第一频率范围内对所述第六批次内存条进行信号完整性测试,获得第七批次内存条,所述第七批次内存条为在所述信号完整性测试中未出现失效和/或故障的内存条;其中,所述信号完整性测试包括受干扰时的信号质量测试。

7、其进一步的技术方案为,根据预设的第一频率范围,对多个内存条进行超频测试,获得第一批次内存条以及多个基频内存条,所述多个基频内存条为在所述预设的第一频率范围的条件下未通过所述超频测试的内存条;降低所述预设的第一频率范围的上限以及下限,获得预设的第二频率范围;根据所述预设的第二频率范围,对所述多个基频内存条进行基频测试,获得第一批次基频内存条,所述第一批次基频内存条为在所述预设的第二频率范围的条件下未通过所述超频测试的基频内存条。

8、其进一步的技术方案为,在所述第二频率范围内根据预设的性能指数,对所述第一批次基频内存条进行性能测试,获得第二批次基频内存条,所述第二批次基频内存条为在所述预设的性能指数下顺利通过所述性能测试的基频内存条;在所述第二频率范围内根据预设的兼容性测试指标,对所述第二批次基频内存条进行兼容性测试,获得第三批次基频内存条,所述第三批次基频内存条为在所述预设的兼容性测试指标下顺利通过所述兼容性测试的基频内存条;在所述第二频率范围内根据预设的异常状态参数,对所述第三批次基频内存条进行拉偏测试,获得第四批次基频内存条,所述第四批次基频内存条为在预设的异常状态参数下顺利通过所述拉偏测试的基频内存条;在所述第二频率范围内对所述第四批次基频内存条进行功能测试,获得第五批次基频内存条,所述第五批次基频内存条为在所述功能测试中未出现失效和/或故障的基频内存条;其中,所述功能测试包括失效分析测试。

9、其进一步的技术方案为,在所述第二频率范围内对所述第五批次基频内存条进行场景切换测试,获得第六批次基频内存条,所述第六批次基频内存条为在所述场景切换测试中未出现失效和/或故障的基频内存条;其中,所述场景切换测试包括启动、重启以及睡眠之间的切换测试;在所述第二频率范围内对所述第六批次基频内存条进行信号完整性测试,获得第七批次基频内存条,所述第七批次基频内存条为在所述信号完整性测试中未出现失效和/或故障的基频内存条;其中,所述信号完整性测试包括受干扰时的信号质量测试。

10、其进一步的技术方案为,根据预设的测试方式对多个颗粒进行筛选,获得多个合格的颗粒,所述预设的测试方式包括逻辑测试以及环境模拟测试;将spd芯片、电路元件、pcb板以及多个所述合格的颗粒进行组装,获得多个内存条。

11、第二方面,本发明提出一种内存条测试装置,所述内存条测试装置包括用于执行如第一方面所述方法的单元。

12、第三方面,本发明提出一种电子设备,包括:存储器,用于存放计算机程序;处理器,用于执行存储器上所存放的程序时,实现如第一方面所述方法的步骤。

13、第四方面,本发明提出计算机可读存储介质,所述存储介质存储有计算机程序,所述计算机程序当被处理器执行时可实现如第一方面所述的方法。

14、综上所述,现有技术中检测出内存条真正失效的原因需要耗费大量时间且效率低下,发明人研究发现其原因在于检测方案当中的检测路线不合理;本申请所述方案中的检测路线为首先通过超频测试实现内存条样本的预处理,然后通过性能测试和兼容性测试将最容易出现异常的因素作为排除条件,接着对余下的内存条样本进行拉偏测试以实现进阶测试,最后只选择通过了进阶测试的内存条样本进行功能测试,内存条不会因不合理的检测路线而导致资源浪费或效率低下,显著降低了内存条的测试成本。

技术特征:1.一种内存条测试方法,其特征在于,所述方法包括:

2.根据权利要求1所述的内存条测试方法,其特征在于,所述方法还包括:

3.根据权利要求2所述的内存条测试方法,其特征在于,所述方法还包括:

4.根据权利要求1所述的内存条测试方法,其特征在于,所述根据预设的第一频率范围,对多个内存条进行超频测试,获得第一批次内存条,包括:

5.根据权利要求4所述的内存条测试方法,其特征在于,所述根据所述预设的第二频率范围,对所述多个基频内存条进行基频测试,获得第一批次基频内存条之后,所述根据预设的第一频率范围,对多个内存条进行超频测试,获得第一批次内存条,还包括:

6.根据权利要求5所述的内存条测试方法,其特征在于,所述在所述第二频率范围内对所述第四批次基频内存条进行功能测试,获得第五批次基频内存条之后,所述根据预设的第一频率范围,对多个内存条进行超频测试,获得第一批次内存条,还包括:

7.根据权利要求1所述的内存条测试方法,其特征在于,所述根据预设的第一频率范围,对多个内存条进行超频测试,获得第一批次内存条之前,还包括:

8.一种内存条测试装置,其特征在于,所述内存条测试装置包括用于执行如权利要求1-7任一项所述方法的单元。

9.一种电子设备,其特征在于,包括:

10.一种计算机可读存储介质,其特征在于:

技术总结本发明涉及一种内存条测试方法、装置、电子设备及介质,包括根据预设的第一频率范围,对多个内存条进行超频测试,获得第一批次内存条;在第一频率范围内根据预设的性能指数,对第一批次内存条进行性能测试,获得第二批次内存条;在第一频率范围内根据预设的兼容性测试指标,对第二批次内存条进行兼容性测试,获得第三批次内存条;在第一频率范围内根据预设的异常状态参数,对第三批次内存条进行拉偏测试,获得第四批次内存条;在第一频率范围内对第四批次内存条进行功能测试,获得第五批次内存条。现有技术中检测出内存条真正失效的原因需要耗费大量时间且效率低下,本申请方案解决了上述问题,显著降低了内存条的测试成本。技术研发人员:李创锋,陈霖受保护的技术使用者:深圳市金泰克半导体有限公司技术研发日:技术公布日:2024/3/12本文地址:https://www.jishuxx.com/zhuanli/20240731/183792.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表